Fターム[5F092AD25]の内容

ホール/MR素子 (37,442) | 素子の動作 (2,918) | 磁化 (1,415) | 磁化方向を制御する方法 (989) | スピン注入により磁化を反転するもの (779)

Fターム[5F092AD25]に分類される特許

81 - 100 / 779

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

磁気抵抗効果素子及びそれを搭載した不揮発性磁気メモリ

【課題】高速かつ消費電力が極めて小さい不揮発性メモリを提供する。

【解決手段】不揮発性磁気メモリに、高出力なトンネル磁気抵抗効果素子を装備し、スピントランスファートルクによる書込み方式を適用する。トンネル磁気抵抗効果素子1は、CoとFeとBを含有する体心立方構造の強磁性膜304と、(100)配向した岩塩構造のMgO絶縁膜305と、強磁性膜306とを積層した構造を有する。

(もっと読む)

半導体装置

【課題】半導体層と強磁性金属層との間のショットキー障壁による接触抵抗を低減し、かつ高効率のスピン注入を実現するための界面抵抗の最適化を可能とすること。

【解決手段】半導体層10と、前記半導体層にスピン偏極した電子を注入、または前記半導体層からスピン偏極した電子を受ける強磁性金属層12と、前記半導体層と前記強磁性金属層との間に設けられ、前記強磁性金属層より小さな仕事関数を有する金属膜16と、前記金属膜と前記半導体層との間に設けられた絶縁膜14と、を具備する半導体装置。

(もっと読む)

磁気スタックおよびこのようなスタックを備えたメモリセル

【課題】磁気スタックおよびこのようなスタックを備えたメモリセルを提供すること。

【解決手段】本発明は、平面外磁化を有する磁気スタック(4)に関し、前記スタックは、

−コバルト、鉄およびニッケル、ならびにこれらの材料をベースとする磁気合金の群から選択される1つまたは複数の材料で構成された第1の磁気層(1)と、

−第1の層の材料と共有界面を形成すると界面起源の垂直異方性を与えることができる金属材料で構成された第2の層(2)と

を備え、スタック(4)は、第1の層(1)の上に堆積した第3の層(3)をさらに備え、第2の層(2)が第3の層(3)の上に堆積し、第3の層(3)が、第1の層の材料との10%未満の混和性を有する金属材料で構成されていることを特徴としている。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】磁気抵抗効果素子のスピン注入磁化反転特性の劣化が抑制され、製造歩留まりが高い不揮発性記憶装置の製造方法を提供する。

【解決手段】実施形態によれば、複数のメモリセルを有する不揮発性記憶装置の製造方法であって、前記メモリセルのそれぞれは、第1電極を含む下地層と、前記下地層の上に設けられた磁気抵抗効果素子と、前記磁気抵抗効果素子の上に設けられた第2電極と、を有する。前記磁気抵抗効果素子は、記憶層である第1磁性層と、前記第1磁性層の上に設けられたトンネルバリア層と、前記トンネルバリア層の上に設けられ、参照層である第2磁性層と、を含む。前記第2磁性層の表面の一部もしくは前記第1磁性層の表面の一部にイオン化されたガスクラスタを照射して、前記第2磁性層の一部および前記第1磁性層の一部をエッチングする。

(もっと読む)

磁気抵抗素子及び磁気記憶装置

【課題】書き込み電流を低減させたまま、リテンション、特に固定磁化層の大きなリテンションを十分に確保することができ、熱的に安定な動作を可能とする信頼性の高い磁気抵抗素子を実現する。

【解決手段】MTJ10は、下部磁性層1と上部磁性層3とでトンネルバリア層2を挟持し、上部磁性層3上にキャップ層4が形成されてなり、下部磁性層1は、トンネルバリア層2と接するCoFeBからなる第1自由層1aと、第1自由層1aに接するTaからなる挿入層1bと、挿入層1bに接するRuからなるスペーサ層1cと、スペーサ層1cに接するCoPtからなる第2自由層1dとを有して構成される。

(もっと読む)

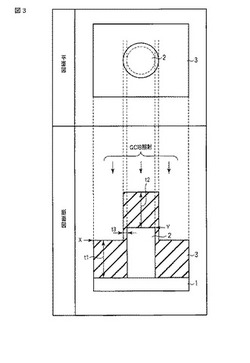

磁気記録素子及び磁気メモリ

【課題】磁気記録素子のMR比の向上を図る。

【解決手段】実施形態に係わる磁気記録素子は、磁化が可変で磁化容易軸方向が膜面に垂直となる方向の磁気記録層11と、磁化が膜面に垂直となる方向に固定される磁気固着層12と、磁気記録層11と磁気固着層12との間の非磁性バリア層13と、磁気記録層11と非磁性バリア層13との間の挿入層14とを備える。挿入層14は、軟磁性材料、ホイスラー合金、ハーフメタル酸化物、及び、ハーフメタル窒化物のうちの1つを含む。

(もっと読む)

半導体記憶装置

【課題】安定した特性の磁気抵抗効果素子を有する半導体記憶装置を提供する。

【解決手段】本発明の実施形態にかかる半導体記憶装置は、複数の磁気抵抗効果素子を有し、この各磁気抵抗効果素子は、半導体基板上に形成され、且つ、その膜面に対して垂直な磁化容易軸を有する第1の磁性層と、第1の磁性層上に形成された非磁性層と、非磁性層上に形成され、且つ、その膜面に対して垂直な磁化容易軸を有する第2の磁性層と、からなる積層構造を有し、保護膜を介して各磁気抵抗効果素子の側壁を覆うように設けられ、且つ、磁気抵抗効果素子に対して、磁化容易軸に沿った方向に引張応力を与える側壁膜を備え、側壁膜のうちの第1の磁性層を覆う部分は、側壁膜のうちの第2の磁性層を覆う部分と比べて厚い。

(もっと読む)

半導体記憶装置

【課題】磁気抵抗効果素子間の磁気的な干渉作用を遮断し、安定した動作を可能にし、且つ、容易に製造することができる半導体記憶装置を提供する。

【解決手段】本発明の実施形態にかかる半導体記憶装置は、半導体基板上にマトリックス状に配列した複数の磁気抵抗効果素子を有し、各磁気抵抗効果素子は、半導体基板上に形成された第1の磁性層と、第1の磁性層上に形成された非磁性層と、非磁性層上に形成された第2の磁性層とからなる積層構造を有し、隣り合う各磁気抵抗効果素子の間には、金属、又は、磁性体材料が分散された絶縁膜が埋め込まれている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】製造コストの増加を抑えつつ、直列に接続されたMTJ素子を所望の特性の抵抗体として機能させることが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、磁化方向に応じて抵抗値が変化可能な複数の記憶用MTJ素子が、半導体基板上に配置されたメモリセルアレイ領域を備える。半導体記憶装置は、複数の抵抗用MTJ素子が、前記半導体基板上に第1の方向および前記第1の方向に垂直な第2の方向に沿って配置された抵抗素子領域を備える。前記半導体基板の上面に平行な前記抵抗用MTJ素子の第1の断面の面積は、前記半導体基板の前記上面に平行な前記記憶用MTJ素子の第2の断面の面積よりも、大きい。

(もっと読む)

磁気メモリチップを有する半導体装置の製造方法

【課題】アセンブリ段階において外部磁場から磁気メモリチップを保護する。

【解決手段】主面に磁気メモリ素子および複数のワイヤボンドパッドが形成された磁気メモリチップを準備する。シリコンより高透磁率を有する第1の磁気シールド板を磁気メモリチップの主面に搭載する。磁気メモリチップをリードフレームのダイパッド上に搭載しダイアタッチフィルムにより接着する。磁気メモリチップのワイヤボンドパッドとリードフレームのリードとをワイヤで電気的に接続する。磁気メモリチップ、磁気シールド板、ワイヤ及びリードの一部を樹脂により封止する。複数の磁気メモリチップを有するシリコンウェハを準備し、シリコンウェハの裏面を研削することによりシリコンウェハを所定の厚さまで薄くしてダイアタッチフィルムを張り付けた後にシリコンウェハをダイシングして各々がダイアタッチフィルムをその裏面に有する複数の磁気メモリチップを形成する。

(もっと読む)

半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

(もっと読む)

磁気メモリセル及びランダムアクセスメモリ

【課題】信頼性の高い低消費電力不揮発性メモリを提供する。

【解決手段】磁気メモリセルが備えるトンネル磁気抵抗効果素子402の強磁性自由層200の磁化容易軸方向に対して直交する方向、特に膜面垂直方向に45度の角度をなす方向に適当な磁界を印加した状態でスピントランスファートルクにより強磁性自由層の磁化反転を行う。

(もっと読む)

3端子スピントルク発振素子(STO)

【課題】3端子スピントルク発振素子(STO)を提供する。

【解決手段】スピントルク発振素子(STO)は、非磁性導電スペーサ層を有する巨大磁気抵抗(GMR)構造とトンネルバリア層を有するトンネル磁気抵抗(TMR)構造の両方の一部を形成する単一の自由強磁性層を有する。STOは、導電スペーサ層を通じてスピントルク励起電流を、そして、トンネルバリア層を通じて相対的に小さな検知電流を供給する電気回路に接続する3つの電気端子を有する。STOが磁界センサとして使用される際には、励起電流は、外部磁界が存在しない状態において自由層の磁化を固定された基底周波数において発振させる。検知電流に結合された検出器は、外部磁界に応答して基底周波数からの自由層磁化発振周波数のシフトを検出する。

(もっと読む)

磁気記憶装置及び磁気記憶装置の製造方法

【課題】 基準素子の抵抗値のばらつきを抑制することが望まれている。

【解決手段】 基板上に磁気抵抗素子及び基準素子が形成されている。磁気抵抗素子は、トンネル絶縁層を自由磁化層と固定磁化層とで挟んだ構造を有し、自由磁化層の磁化方向によって低抵抗状態と高抵抗状態との間で抵抗が変化し、第1の方向に長い平面形状を有する。基準素子は、トンネル絶縁層を自由磁化層と固定磁化層とで挟んだ構造を有し、磁気抵抗素子の低抵抗状態の抵抗と高抵抗状態の抵抗との間の抵抗を有し、第1の方向と直交する第2の方向に長い平面形状を有する。

(もっと読む)

交換バイアスを有する磁気デバイス

【課題】所与の厚さの反強磁性層に対する交換バイアスが増加した磁気デバイスを提案することによって従来技術の欠点を克服すること。

【解決手段】本発明は、自由層として知られている、可変磁化方向を有する磁気層と、前記自由層と接触している、前記自由層の磁化方向をトラップすることができる第1の反強磁性層とを備えた磁気デバイスに関する。磁気デバイスは、さらに、安定化層として知られている、自由層とは反対側の面を介して第1の反強磁性層と接触している、強磁性体から作製される層を備えており、前記自由層および安定化層の磁化方向は実質的に垂直である。前記自由層および安定化層のうちの第1の層は磁化を有しており、その方向は、前記第1の層の平面内に配向されており、一方、前記自由層および安定化層のうちの2つの層の第2の層も磁化を有しており、その方向は、前記第2の層の平面外に配向されている。

(もっと読む)

記憶素子及び記憶装置

【課題】外部放射線に対し耐性を有し、誤動作なく安定した動作する信頼性の高い記憶素子の提供。

【解決手段】記憶素子は、情報を磁性体の磁化状態により保持する記憶層と、記憶層に記憶された情報の基準となる磁化を有する磁化固定層と、記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する。そして記憶層、中間層、磁化固定層を有する層構造の積層方向に流れる電流に伴って発生するスピントルク磁化反転を利用して記憶層の磁化を反転させることにより情報の記憶を行うとともに、記憶層は、Bを含有する強磁性層を含み、Bにふくまれる10Bの同位体比率が、自然界における19.9%よりも低くなっている。

(もっと読む)

記憶素子及びメモリ

【課題】書き込み電流を増大させることなく、熱安定性を改善することができるメモリを提供する。

【解決手段】情報を磁性体の磁化状態により保持する記憶層を有し、この記憶層に対して、中間層を介して磁化固定層が設けられ、中間層が絶縁体から成り、積層方向にスピン偏極した電子を注入することにより、記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる記憶素子と、この記憶素子の積層方向に流す電流を供給する配線とを備え、記憶素子の上に隣接して積層された層に、記憶層と熱膨張係数の異なる、TiN,WN,TaN,Moのうちのいずれかの材料が用いられ、記憶層に歪が印加されているメモリを構成する。

(もっと読む)

垂直磁化磁気抵抗効果素子及び磁気メモリ

【課題】垂直磁気異方性を有する強磁性材料を用いて作製した磁気抵抗効果素子において、ビット情報に対応する磁化の平行状態及び反平行状態の熱安定性が不均衡になり、保存している情報により記録保持時間が異なる状態を改善する。

【解決手段】磁気抵抗効果素子を構成する参照層106と記録層107の面積を異ならせることにより、保存している情報に応じた記録保持時間の差を補正する。

(もっと読む)

記憶素子及び記憶装置

【課題】書き込み電流(反転電流)および熱安定性のばらつきを抑制し、安定して動作する、信頼性の高い記憶素子の提供。

【解決手段】記憶素子は、情報を磁性体の面内磁化状態により保持する記憶層と、該記憶層に記憶された情報の基準となる磁化を有する磁化固定層と、記憶層と磁化固定層の間に設けられる非磁性体による中間層とを有する。

そして記憶層、中間層、磁化固定層を有する層構造の積層方向に流れる電流に伴って発生するスピントルク磁化反転を利用して上記記憶層の磁化を反転させることにより情報の記憶を行うとともに記憶層の困難軸方向の異方性磁界が、垂直方向の異方性磁界よりも小さくなっている。

(もっと読む)

81 - 100 / 779

[ Back to top ]