Fターム[5F101BA36]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG周囲絶縁膜 (3,604) | 薄膜化又は絶縁膜材料の特徴部位 (1,645) | CGとFG間 (1,254)

Fターム[5F101BA36]に分類される特許

201 - 220 / 1,254

半導体装置の製造方法

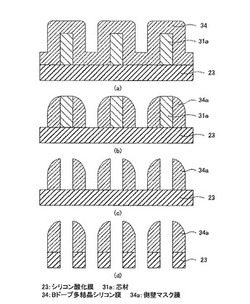

【課題】製造工程時間の増加を抑制して、微細なラインアンドスペースパターンを形成可能な半導体装置の製造方法を提供する。

【解決手段】被加工材であるシリコン酸化膜23上に、パターニングされた芯材31aとなるアンドープ多結晶シリコン膜31を形成する工程と、アンドープ多結晶シリコン膜31をスリミングして芯材31aとする工程と、芯材31aの側面及び上面、並びにシリコン酸化膜23の上面を被うように、シリコン酸化膜23と同じシリコン酸化膜にボロンが導入されたBドープ多結晶シリコン膜34を形成する工程と、芯材31a及びシリコン酸化膜23の上面のBドープ多結晶シリコン膜34を除去し、芯材31aの側面にBドープ多結晶シリコン膜34からなる側壁マスク膜34aを形成する工程と、芯材31aを除去する工程と、側壁マスク膜34aをマスクとしてシリコン酸化膜23をエッチング加工する工程とを備える。

(もっと読む)

半導体装置

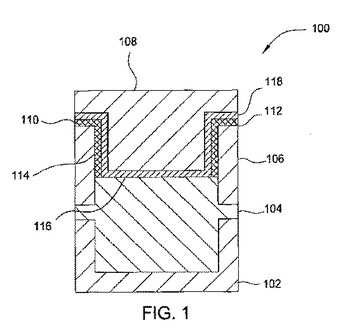

【課題】トランジスタ間の分離性が良好な半導体装置を提供する。

【解決手段】半導体装置において、第1導電型の半導体基板と、前記半導体基板の上層部分を複数の能動領域に区画する素子分離絶縁膜と、前記能動領域の上部に相互に離隔して形成された第2導電型のソース層及びドレイン層と、前記半導体基板上における前記ソース層と前記ドレイン層との間のチャネル領域の直上域に設けられたゲート電極と、前記半導体基板と前記ゲート電極との間に設けられたゲート絶縁膜と、第1導電型であり、実効的な不純物濃度が前記半導体基板の実効的な不純物濃度よりも高く、前記能動領域における前記ソース層及び前記ドレイン層の直下域に形成され、前記ゲート電極の直下域には形成されていないパンチスルーストッパ層と、を設ける。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位変換回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

単一ステップによる選択的窒化の方法および装置

半導体基板を選択的に1ステップで窒化するための方法および装置が提供される。窒素は、選択的窒化プロセスを利用することにより、シリコン領域および酸化ケイ素領域を有する半導体基板のシリコン領域中に選択的に組み込まれる。窒素含有プラズマを形成し、このプラズマからイオンをフィルタリングまたは除去することにより、基板に窒素含有ラジカルが向けられてもよく、または、選択前駆体を使用する熱窒化プロセスを実施してもよい。遠隔プラズマジェネレータが、1つまたは複数のイオンフィルタ、シャワーヘッド、およびラジカル分配器を任意に備える処理チャンバに結合されてもよく、または、in situプラズマが生成され、1つまたは複数のイオンフィルタもしくはイオンシールドが、チャンバ内においてプラズマ発生ゾーンと基板支持体との間に配設されてもよい。  (もっと読む)

(もっと読む)

半導体装置と不揮発性半導体記憶装置

【課題】キャパシタのコンタクトプラグ形成に伴うショート不良を低減させることができ、素子信頼性の向上をはかる。

【解決手段】半導体装置であって、半導体基板10上に、第1の絶縁膜21,第1の導電層22,第2の絶縁膜23,及び第2の導電層24が積層され、且つ導電層22,24の一部が接続された積層構造部と、導電層22を接続部を含む第1の領域と接続部を含まない第2の領域に分離する層間絶縁膜26と、第2の領域の一周辺部で、導電層21,絶縁膜22,及び基板10に形成された素子分離溝に埋め込まれた素子分離絶縁膜15と、第1の領域に接続された第1のコンタクトプラグ31と、第2の領域に接続され且つ素子分離絶縁膜15の上方に形成された第2のコンタクトプラグ32と、第2の領域側の一周辺部に隣接する領域で基板10に接続された第3のコンタクトプラグ33を備えた。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】素子分離絶縁膜の埋め込み後の化学機械研磨法による研磨で、浮遊ゲート電極をストッパ膜として使用できるようにする。

【解決手段】シリコン基板1にゲート絶縁膜4、下層多結晶シリコン膜5a、上層多結晶シリコン膜5bを積層形成する。上層多結晶シリコン膜5bは、成膜時に炭素を1×1018atoms/cm3以上例えば2×1020〜2×1021atoms/cm3の範囲の濃度で添加される。素子分離溝1bを形成した後に、素子分離絶縁膜2を埋め込み、化学機械研磨法の研磨で素子分離溝1b内以外の部分を除去する。この時、上層多結晶シリコン膜5bがスクラッチの発生を抑制できるストッパ膜として利用でき、シリコン窒化膜などを不要とした構成とすることができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のトランジスタ160と、第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成され、第1のトランジスタ160のゲート電極と、第2のトランジスタ162のソース・ドレイン電極とは、電気的に接続され、第1の配線と、第1のトランジスタ160のソース電極とは、電気的に接続され、第2の配線と、第1のトランジスタ160のドレイン電極とは、電気的に接続され、第3の配線と、第2のトランジスタ162のソース・ドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のトランジスタ162のゲート電極とは、電気的に接続される。

(もっと読む)

半導体装置

【課題】バーズビーク酸化に関する問題を効果的に解決することが可能な半導体装置を提供する。

【解決手段】半導体基板1上に形成されたトンネル絶縁膜2aと、トンネル絶縁膜上に形成された浮遊ゲート電極3と、浮遊ゲート電極上に形成された電極間絶縁膜6と、電極間絶縁膜上に形成された制御ゲート電極7と、トンネル絶縁膜と浮遊ゲート電極との間に形成され、且つ浮遊ゲート電極のチャネル長方向に平行な一対の側面の下端近傍に形成された一対の酸化膜4aと、トンネル絶縁膜と浮遊ゲート電極との間に形成され、且つ一対の酸化膜の間に形成された窒化膜2cとを備え、一対の酸化膜はそれぞれ、チャネル幅方向に平行な断面において上から下に向かってしだいに幅が広くなっている楔状の形状を有している。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体OSを用い、オフ状態でのソースとドレイン間のリーク電流(オフ電流)が少ない書き込み用トランジスタ162、書き込み用トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルを有する半導体装置において、メモリセルへの情報の書き込みは、書き込み用トランジスタ162のソース電極またはドレイン電極の一方と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードFGに電位を供給し、ノードFGに所定量の電荷を保持させることで行う。書き込みを1×109回行う前後において、メモリセルのメモリウィンドウ幅の変化量は2%以内である。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】不揮発性半導体記憶装置の高集積化,高耐圧化,高速化,加工容易性を同時に実現する。

【解決手段】トンネル絶縁膜上のフローティングゲート電極層,ゲート間絶縁膜,第1,第2コントロールゲート電極層及び金属シリサイド膜を備えるメモリセルトランジスタと、高電圧用ゲート絶縁膜21上の高電圧用ゲート電極層51,一部分開口したゲート間絶縁膜25,第1,第2コントロールゲート電極層48,46及び金属シリサイド膜53を備える高電圧トランジスタと、トンネル絶縁膜20上のフローティングゲート電極層50,一部分開口したゲート間絶縁膜25,第1,第2コントロールゲート電極層48,46及び金属シリサイド膜53を備える低電圧トランジスタと、メモリセルトランジスタ,高電圧トランジスタ及び低電圧トランジスタのソース・ドレイン領域上に直接配置されるライナー絶縁膜27とを備える不揮発性半導体記憶装置の製造方法。

(もっと読む)

不揮発性半導体記憶装置と半導体装置および、不揮発性半導体記憶装置の製造方法

【課題】配線間に形成される容量を低減でき、メモリセルのしきい値電圧の変動を抑制できる不揮発性半導体記憶装置およびこの製造方法を提供する。

【解決手段】半導体基板1上に、第1絶縁膜15を介して形成された第1フローティングゲートFGa及び第2フローティングゲートFGbと、第1フローティングゲートFGa上に、第3絶縁膜18aを介して形成され、幅が第1フローティングゲートFGaより広い第1幅広部28aを有する第1コントロールゲートCG1と、第2フローティングゲートFGb上に、同様に形成された第2幅広部28bを有する第2コントロールゲートCG2と、第1コントロールゲートCG1と、第2コントロールゲートCG2とを覆うように形成された層間絶縁膜17と、層間絶縁膜17において、少なくとも、第1フローティングゲートFGaと第2フローティングゲートFGbとの間に位置する部分に形成された空隙部GAとを備える。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体以外の半導体材料が用いられた第1のチャネル形成領域を有する第1のトランジスタ160と、第1のトランジスタ160の上方の、酸化物半導体材料が用いられた第2のチャネル形成領域を有する第2のトランジスタ162と、容量素子164と、を有し、第2のトランジスタ162の第2のソース電極または第2のドレイン電極の一方と、容量素子164の電極の一方とは、電気的に接続される。

(もっと読む)

誘電体膜の製造方法

【課題】比誘電率の低下を軽減しつつリーク電流値を低減し、スパッタ率の低下による堆積速度の減少を抑制し、かつ、面内均一性に優れた誘電体膜の製造方法を提供すること。

【解決手段】本発明の一実施形態に係る誘電体膜の製造方法は、基板上に、AlとSiとOを主成分とする金属酸化物である誘電体膜を形成する誘電体膜の製造方法であって、Al元素とSi元素のモル比率Si/(Si+Al)が0<(B/(A+B))≦0.1であり、非晶質構造を有する金属酸化物を形成する工程と、該非晶質構造を有する金属酸化物に1000℃以上のアニール処理を施し、結晶相を含む金属酸化物を形成する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】不揮発性メモリを用いた半導体装置において、消去動作の高速化及び低消費電力化を実現する。

【解決手段】チャネル形成領域、トンネル絶縁膜及び浮遊ゲートを順に積層した不揮発性メモリにおいて、チャネル形成領域を酸化物半導体層により構成する。さらに、チャネル形成領域の下側に、浮遊ゲートと対向する位置に消去用の金属配線を設けた構造とする。上記構造により、消去動作において、浮遊ゲートに蓄積された電荷はチャネル形成領域を介して金属配線に引き抜かれる。これにより、半導体装置の消去動作を高速化し、低消費電力化を実現できる。

(もっと読む)

電界効果型トランジスタ、半導体メモリ、表示素子、画像表示装置及びシステム

【課題】比誘電率が高くリーク電流の少ない絶縁膜を提供する。

【解決手段】基板と、前記基板上に形成されたソース電極、ドレイン電極、及びゲート電極と、前記ゲート電極に所定の電圧を印加することによりソース電極とドレイン電極との間にチャネルが形成される半導体層を有し、前記ゲート電極と前記半導体層の間にゲート絶縁層と、を備え、前記ゲート絶縁層は、アルカリ土類金属の中から選ばれた1または2種類以上の元素と、Ga、Sc、Y、及びCeを除くランタノイドの中から選ばれた1または2種類以上の元素とを含むアモルファス複合金属酸化物絶縁膜により形成されていることを特徴とする電界効果型トランジスタを提供することにより上記課題を解決する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】

本発明は、コンタクトホールのアスペクト比の低減可能な半導体記憶装置及びその製造

方法を提供する。

【解決手段】

半導体基板11a上に形成された所定の間隔を隔てて設けられ、直列接続された複数の

メモリセルトランジスタM、複数の前記メモリセルトランジスタMの両端に形成された選

択ゲートトランジスタTを有する複数のNANDストリングと、隣接する前記NANDス

トリングの前記選択ゲートトランジスタT間に設けられたコンタクトプラグ18とを備え

、隣接する前記選択ゲートトランジスタT間の第1の方向における幅が前記メモリセルト

ランジスタMの前記ゲート長のk倍(kは自然数)と前記所定の間隔の(k+1)倍の総

和と等しい場合には、第1の方向における前記コンタクトプラグ18の幅は、前記メモリ

セルトランジスタMの前記ゲート長のk倍と前記所定の間隔の(k−1)倍の総和よりも

長いことを特徴とする半導体記憶装置。

(もっと読む)

半導体装置

【課題】記憶容量の大容量化に伴うメモリ誤動作の発生を抑制できる不揮発性メモリを含む半導体装置を提供すること。

【解決手段】半導体基板と、その表面に埋め込まれた素子分離絶縁膜と、該基板上の複数の不揮発性のメモリセルを備え、該メモリセルは、該基板上の第1絶縁膜、第1絶縁膜上の電荷蓄積層、電荷蓄積層上方の制御ゲート電極及び制御ゲート電極と電荷蓄積層の間の第2絶縁膜を備え、該メモリセルのチャネル幅方向の断面において、素子分離絶縁膜上面は該基板表面よりも高く且つ電荷蓄積層上面よりも低く、第2絶縁膜は素子分離絶縁膜上面及び電荷蓄積層上面上に設けられ、素子分離絶縁膜上面上の第2絶縁膜は電荷蓄積層上面上の第2絶縁膜よりも誘電率が低く且つ電荷蓄積層上面上の第2絶縁膜とは組成が異なる領域を含み及び複数の該メモリセルの隣接する該メモリセル間の素子分離絶縁膜上面上の制御ゲート電極は下に向かって突出している。

(もっと読む)

不揮発性メモリ

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】不揮発性メモリは、第1のトランジスタ20及び第2のトランジスタ21を有するメモリセルを有し、第1のトランジスタ20は第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタ21は酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタ160と、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

201 - 220 / 1,254

[ Back to top ]