Fターム[5F101BA36]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG周囲絶縁膜 (3,604) | 薄膜化又は絶縁膜材料の特徴部位 (1,645) | CGとFG間 (1,254)

Fターム[5F101BA36]に分類される特許

121 - 140 / 1,254

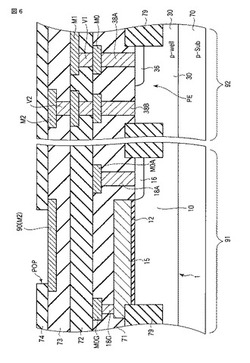

半導体装置

【課題】半導体装置を高集積化する。

【解決手段】本実施形態の半導体装置は、絶縁体内に設けられ、半導体集積回路を含んでいる半導体基板70と、絶縁体の開口部POPを介してその上面が露出するパッド90と、パッド90下方において半導体基板70のキャパシタ領域91内に設けられる複数のキャパシタ1と、を具備し、キャパシタ1は、所定の被覆率を満たすように、パッド90下方のキャパシタ領域91内に設けられ、キャパシタ1の2つの電極にそれぞれ接続されるコンタクト18A,18Gは、開口部POPと上下に重ならない位置に設けられている。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】フローティングゲート電極は、高い不純物濃度領域と低い不純物濃度領域とからなり、高い不純物濃度領域は、コントロールゲート絶縁膜と接する部分に配置し、低い不純物濃度領域はトンネル絶縁膜と接する領域に配置し、フローティングゲート電極のコントロールゲート絶縁膜と接する表面部分には微細凹凸を形成した。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル領域のエッジ近傍のトンネル絶縁膜上には、トンネル絶縁膜とは異なる材質の絶縁膜からなる電界緩和層を配置した。

(もっと読む)

半導体装置の製造方法

【課題】注入した不純物の拡散を抑制しつつ結晶欠陥を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、リンまたはボロンを分子状イオンの形態で含有する第1の不純物80と、リンまたはボロンよりも注入量が少ない炭素、フッ素または窒素を分子状イオンの形態で含有する、もしくは、リンまたはボロンよりも注入量が少ない炭素を原子イオンの形態で含有する第2の不純物81と、を半導体層1に注入して不純物注入層9を形成する工程を含む。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を提供する。

【解決手段】トンネル領域とフローティングゲート電極との間には、膜厚の異なる複数のトンネル絶縁膜を形成した。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】浮遊ゲート電極の細りを補償して信頼性を向上させた不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置10では、第1の幅W1を有する活性領域12が、半導体基板11の主面に形成された素子分離層13で分離されている。第1ゲート絶縁膜14が、活性領域12に形成されている。第1の幅W1より狭い第2の幅W2を有する第1導電層15aが、第1ゲート絶縁膜14を介して活性領域12に形成されている。第1の幅W1と第2の幅W2の差を補償するように第3の幅W3を有する第2導電層15aが第1導電層15aの側壁に形成されている。第1ゲート電極15は、第1導電層15aと第2導電層15bを含んでいる。第2ゲート絶縁膜16が、第1ゲート電極15および素子分離層13上にコンフォーマルに形成されている。第2ゲート電極17が、第2ゲート絶縁膜16上に形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離溝を塗布系の材料で埋め込む素子分離構造において、熱処理時に素子分離溝に大きな応力が作用することを防止する。

【解決手段】メモリセル領域に形成され第1の開口幅を有する第1の素子分離溝と、周辺回路領域に形成され第1の開口幅より大きい第2の開口幅を有する第2の素子分離溝と、第1の素子分離溝の内面に形成された第1の酸化膜と、第1の酸化膜上に形成されて前記第1の素子分離溝内に埋め込まれた第1の塗布型酸化膜と、第2の素子分離溝の内面のうちの側部に形成された第2の酸化膜と、第2の素子分離溝内の内面のうちの底部上に形成された第3の酸化膜と、第3の酸化膜上に形成されて第2の素子分離溝内に埋め込まれた第2の塗布型酸化膜とを備えた。

(もっと読む)

不揮発性記憶素子及びその製造方法

【課題】 信頼性を向上可能な不揮発性記憶素子及びその製造方法を提供する。

【解決手段】 不揮発性素子は、基板100、基板100の上に形成され、制御ベースゲート120a及び制御ベースゲート120aの上に形成される制御金属ゲート125anを有する制御ゲート電極137、制御ゲート電極137と基板100との間に形成される電荷格納領域110a、制御ゲート電極137の上に形成される制御ゲートマスクパターン130、及び制御ゲートマスクパターン130及び制御ベースゲート120aの間に形成された制御金属ゲート125aの側壁の上に形成される酸化防止スペーサ135aを備える。このとき、制御金属ゲート125anの幅は、制御ゲートマスクパターン130の幅より小さくなるように形成されている。これにより、制御金属ゲート125anが酸化工程又は酸化物等によって酸化されることを防止することができる。

(もっと読む)

半導体基板の作製方法

【課題】半導体基板の欠陥を低減する。また、歩留まり高く欠陥の少ない半導体基板を作製する。また、歩留まり高く半導体装置を作製する。

【解決手段】支持基板に酸化絶縁層を介して半導体層を設け、該半導体層の端部における、支持基板及び酸化絶縁層の密着性を高めた後、半導体層の表面の絶縁層を除去し、半導体層にレーザ光を照射して、平坦化された半導体層を得る。半導体層の端部において、支持基板及び酸化絶縁層の密着性を高めるために、半導体層の表面から、レーザ光を照射する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】電極間絶縁膜7下において、埋め込み絶縁膜9が上下に分離されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、空隙AG1にて分離された上側の埋め込み絶縁膜9は電極間絶縁膜7下に積層し、下側の埋め込み絶縁膜9はトレンチ2内に配置する。

(もっと読む)

半導体記憶装置

【課題】チャネル領域にソース領域及びドレイン領域を形成せずに、信頼性が高い動作が可能な半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、第1の方向に延びる同一導電形のチャネル領域と、チャネル領域上に設けられた第1の絶縁膜と、第1の絶縁膜上に設けられた複数の浮遊ゲートと、浮遊ゲートの上に設けられた第2の絶縁膜と、第2の絶縁膜の上に設けられた制御ゲートとを備えている。複数の浮遊ゲートは第1の方向及びこれに交差する第2の方向に分断されている。制御ゲートは第1の方向に対して交差する第2の方向に延びている。浮遊ゲートのフリンジ電界によって、第1の方向で隣り合う浮遊ゲート間の下のチャネル領域の表面に反転層が形成される。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】空隙AG1の埋め込み絶縁膜4が除去される前に側壁保護膜3´にてトンネル絶縁膜5の側壁を覆うことにより、埋め込み絶縁膜4とトンネル絶縁膜5との間でウェット処理のエッチング選択比が確保できない場合においても、トンネル絶縁膜5を保護できるようにする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】浮遊ゲート電極膜と制御ゲート電極膜との間に設ける電極間絶縁膜の絶縁特性をより一層改善する。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板にゲート絶縁膜を介して形成された電荷蓄積層と、前記電荷蓄積層の上に形成され、シリコン窒化膜を2層のシリコン酸化膜で挟んだ積層構造を含む複数層構造で構成された電極間絶縁膜と、前記電極間絶縁膜上に形成された制御電極層とを備え、前記電極間絶縁膜の前記シリコン窒化膜について、前記電荷蓄積層の上面部分上の前記シリコン窒化膜の膜厚を、前記電荷蓄積層の側面部分上の前記シリコン窒化膜よりも薄くし、前記シリコン窒化膜上に形成された前記シリコン酸化膜について、前記電荷蓄積層の上面部分上の前記シリコン酸化膜の膜厚を、前記電荷蓄積層の側面部分上の前記シリコン酸化膜よりも厚くした。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】データの保持期間を長くする半導体装置又は半導体記憶装置を提供する。

【解決手段】一対の不純物領域を有する第1の半導体層152aと、第1の半導体層と同じ材料であり、第1の半導体層と離間する第2の半導体層152bと、第1、第2の半導体層の上に設けられた第1の絶縁層153と、第1の絶縁層153を介して第1の半導体層に重畳する第1の導電層154と、第1の絶縁層153を介して第1の導電層に重畳し、第1の半導体層と異なる材料である第3の半導体層156と、第1の導電層及び第3の半導体層に電気的に接続される第2の導電層157bと、第3の半導体層156に電気的に接続され、第2の導電層と同じ材料である第3の導電層157aと、第3の半導体層、第2の導電層、及び第3の導電層の上に設けられた第2の絶縁層158と、第2の絶縁層を介して第3の半導体層に重畳する第4の導電層159と、を含む。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】トレンチ2内に埋め込まれた第2の埋め込み絶縁膜4の一部が除去されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、浮遊ゲート電極6間が完全に埋め込まれないようにして制御ゲート電極8間にカバー絶縁膜10が掛け渡されることで、ビット線方向にDBに隣接する浮遊ゲート電極6間に空隙AG2が形成されている。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】レンチ2内に埋め込まれた埋め込み絶縁膜3の一部を除去することで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1を形成し、空隙AG1は、制御ゲート電極8下に潜るようにしてトレンチ2に沿って連続して形成する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】対向する二つの記憶素子のコントロールゲートのゲート長に起因する記憶素子の特性のばらつきを抑制する。

【解決手段】上記の課題を解決するために、不揮発性半導体記憶装置(1)を以下のように構成する。第1不揮発性メモリセル(1a)は、第1チャネル領域(11a)と、第1フローティングゲート(5a)と、第1コントロールゲート(6a)とを含むものとする。また、第2不揮発性メモリセル(1b)は、第2チャネル領域(11b)と、第2フローティングゲート(5b)と、第2コントロールゲート(6b)とを含むものとする。ここにおいて、第1チャネル領域(11a)は、第1フローティングゲート側チャネル領域(13a)と、第1コントロールゲート側チャネル領域(12a)とを備え、第1コントロールゲート側チャネル領域(12a)は不純物濃度が濃い高濃度ポケット領域(10)を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】スタック構造のゲート電極を有する不揮発性メモリの低電圧動作化・低消費電力化を実現しうる半導体装置の製造方法を提供する。

【解決手段】素子分離絶縁膜上に第1の導電膜を形成し、素子領域上に第1の絶縁膜を形成し、第1の絶縁膜上及び第1の導電膜が形成された素子分離絶縁膜上に第2の導電膜を形成し、第2の導電膜及び第1の導電膜をパターニングし、第2の導電膜により形成された第1の部分が素子領域上に位置し、第1の導電膜と第2の導電膜の積層膜により形成された第2の部分が素子分離絶縁膜上に位置するフローティングゲートを形成し、フローティングゲート上に第2の絶縁膜を形成し、第2の絶縁膜上にコントロールゲートを形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】柱状のチャネル層となる半導体層に沿って、複数の浮遊ゲート型の不揮発性メモリセルが積層された構造の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、柱状の半導体膜131の側面にトンネル誘電体膜141、浮遊ゲート電極膜142、ゲート間絶縁膜143および制御ゲート電極膜144を備えるメモリセルMCが半導体膜131の延在方向に複数設けられるメモリセル列を、半導体基板101上に略垂直に複数配置した不揮発性半導体記憶装置が提供される。ここで、浮遊ゲート電極膜142と制御ゲート電極膜143は、柱状の半導体膜131の全周のうち特定の方向の側面にのみ形成されている。

(もっと読む)

半導体メモリ及びその製造方法

【課題】半導体メモリの構造の簡略化と製造プロセスの簡易化とを実現する。

【解決手段】半導体基板と、半導体基板内に形成され、かつ互いに直交する第1及び第2の方向にそれぞれ延在する第1及び第2のソース領域104、109とを有する半導体メモリ。第1及び第2のソース領域はそれぞれ拡散領域であって、交差する部分で電気的に接続されている。また半導体メモリは、第2のソース領域109と同一方向に延在するビットライン108と、第2のソース領域109上に形成されたソースラインとを有し、ソースラインと第2のソース領域109とのコンタクトと、ビットライン108と半導体基板内に形成されたドレイン領域とのコンタクトとは直線状に配置されている。

(もっと読む)

121 - 140 / 1,254

[ Back to top ]