Fターム[5F101BA36]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | FG型 (6,485) | FG周囲絶縁膜 (3,604) | 薄膜化又は絶縁膜材料の特徴部位 (1,645) | CGとFG間 (1,254)

Fターム[5F101BA36]に分類される特許

161 - 180 / 1,254

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書 き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】電気的書き換え可能な半導体不揮発性メモリにおいて、第2導電型のドレイン領域内のトンネル領域の表面には、薄い不純物濃度の第1導電型の領域を形成した。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込みを高速化した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置110は、ベース半導体層10aと、電極70aと、チャネル半導体層30aと、ベーストンネル絶縁膜20aと、チャネルトンネル絶縁膜40aと、電荷保持層50aと、ブロック絶縁膜60aと、を有するメモリ部MC1を備える。チャネル半導体層30aは、ベース半導体層10aと電極70aとの間に設けられ、電極70aに対向するチャネル部31aを含む。ベーストンネル絶縁膜20aは、ベース半導体層10aとチャネル半導体層30aとの間に設けられる。チャネルトンネル絶縁膜40aは、電極70aとチャネル部31aとの間に設けられる。電荷保持層50aは、電極70aとチャネルトンネル絶縁膜40aとの間に設けられ、電荷を保持する。ブロック絶縁膜60aは、電極70aと電荷保持層50aとの間に設けられる。

(もっと読む)

不揮発性半導体記憶装置の製造方法及び不揮発性半導体記憶装置

【課題】シリサイド工程による不具合を抑制しつつ、十分な量のシリサイドを形成することのできる不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】不揮発性半導体記憶装置の製造方法は、浮遊ゲート電極、浮遊ゲート電極上の第1の電極間絶縁膜及び第1の電極間絶縁膜上の制御ゲート電極を有するメモリセルトランジスタを形成し、下側ゲート電極、第2の電極間絶縁膜及び第2の電極間絶縁膜上の上側ゲート電極を有する電界効果トランジスタを形成する。制御ゲート電極及び上側ゲート電極の上面が露出するように層間絶縁膜を形成する。制御ゲート電極及び上側ゲート電極の上面が層間絶縁膜の上面よりも低くなるようにエッチバックする。制御ゲート電極、上側ゲート電極及び層間絶縁膜上の全面に第1の導電膜を形成する。第1の層間絶縁膜をエッチバックする。制御ゲート電極、上側ゲート電極及び第1の導電膜上に金属を堆積してシリサイド化する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】隣接セルとの容量を抑制することが可能な半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態の半導体記憶装置は、第1の方向および前記第1の方向と直交する第2の方向に配置される複数のメモリセルトランジスタを備える。前記メモリセルトランジスタのそれぞれは、半導体基板上に形成される第1の絶縁膜と、前記第1の絶縁膜上に形成される浮遊ゲート電極と、前記浮遊ゲート電極上に形成される第2の絶縁膜と、前記第2の絶縁膜上に形成される制御ゲート電極と、を有する。前記第1および第2の方向に隣接する2つの前記メモリセルトランジスタの前記浮遊ゲート電極は、前記隣接する方向の側面に括れた領域を有する。

(もっと読む)

半導体装置の製造方法

【課題】工程数を増加させることなく、高耐圧トランジスタへのイオン注入を的確に実行することを可能にする。

【解決手段】

第1素子形成領域(AA1)のうち、第1トランジスタ(Tr1)のゲート電極が形成されるべき第1領域(R1’)の直上に位置するマスク材(M1)の第1部分(H1’)を除去する一方、第1部分(H1’)以外の第1素子形成領域(AA1)にはマスク材(M1)を残存させる。一方、第2素子形成領域(AA2)のうち、第2トランジスタ(Tr2)のゲート電極が形成されるべき第2領域(R1)の直上に位置するマスク材の少なくとも第2部分(H1)と、第2トランジスタ(Tr1)のソース/ドレイン拡散領域が形成されるべき第3領域(R2、R3)の直上に位置するマスク材の少なくとも第3部分(H2,H3)とを除去してマスク材の開口を形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 セル部のブロック絶縁膜の誘電率を低下させることなく、セル部のブロック絶縁膜を分断するセル間における絶縁膜中の欠陥を低減し、電荷保持特性の劣化を抑制する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】 実施形態の不揮発性半導体記憶装置においては、半導体基板上にトンネル絶縁膜、前記トンネル絶縁膜上に電荷蓄積層、前記電荷蓄積層上にブロック絶縁膜が設けられる。前記半導体基板に設けられた素子分離溝部に埋め込まれ、底面が前記半導体基板と前記トンネル絶縁膜の接する面の高さよりも低く、かつ上面が前記電荷蓄積層および前記ブロック絶縁膜の接する面の高さよりも低い第1の素子分離絶縁膜が設けられる。前記第1の素子分離絶縁膜上に形成され、前記ブロック絶縁膜の側面と接して前記ブロック絶縁膜上面まで突出し、かつSi濃度が前記ブロック絶縁膜よりも高い第2の素子分離絶縁膜が設けられる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択トランジスタのカットオフ特性を維持しつつ、オフセット特性の悪化を抑制する。

【解決手段】半導体基板の表層部を活性領域に分離する素子分離絶縁膜と、前記半導体基板の活性領域上のゲート絶縁膜上に形成され第1の導電層、電極間絶縁膜および第2の導電層を有するメモリゲート電極および前記メモリゲート電極の両脇に位置する前記活性領域に形成された第1のソース/ドレイン領域を備えたメモリセルトランジスタと、前記メモリセルトランジスタに隣接して配置され、前記第1のゲート絶縁膜上に導電層を積層した選択ゲート電極および前記選択ゲート電極の両脇に位置する前記活性領域に形成された第2のソース/ドレイン領域を備えた選択ゲートトランジスタとを有し、前記活性領域に形成される少なくとも前記第2のソース/ドレイン領域は、前記活性領域の表層部が掘り下げられた凹部に設けられていることを特徴とする。

(もっと読む)

不揮発性プログラマブルロジックスイッチおよび半導体集積回路

【課題】回路サイズを減少させることを可能にする。

【解決手段】素子分離領域102によって分離された、隣接する第1導電型の第1半導体領域101aおよび第2導電型の第2半導体領域101cと、第1半導体領域101a上に設けられた不揮発性メモリセルトランジスタ10と、第2半導体領域101c上に設けられ、第1半導体領域101aに設けられた第1ドレイン領域10bと電気的に接続されたゲート電極20C2とを有するパストランジスタ20と、第1半導体領域101aに設けられ第1半導体領域に基板バイアスを印加する第1電極8と、第2半導体領域101cに設けられ第2半導体領域に基板バイアスを印加する第2電極9と、を備えている。

(もっと読む)

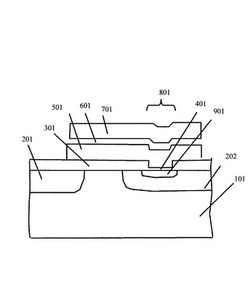

不揮発性メモリのゲートのパターニング方法

【課題】不揮発性メモリ(NVM)領域及び前記NVM領域と重ならないよう非NVM領域を有する半導体基板の上にNVMのゲートスタックを形成する。

【解決手段】

上記の製造方法は、半導体基板上のNVM領域及び非NVM領域に選択ゲート層を形成する工程と、NVM領域及び非NVM領域における選択ゲート層を同時にエッチングする工程と、NVM領域及び非NVM領域における半導体基板上に電荷蓄積層を形成する工程と、NVM領域及び非NVM領域における電荷蓄積層上に制御ゲート層を形成する工程と、NVM領域及び非NVM領域における電荷蓄積層を同時にエッチングする工程とを備える。NVM領域における選択ゲート層をエッチングする工程は、電荷蓄積層の部分が選択ゲート層の第1部分上にあり、かつ選択ゲート層の第1部分の側壁と重なるように行い、かつ、制御ゲート層の部分を電荷蓄積層の部分上にあるように行う。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】周辺回路領域の素子の寿命が劣化するのを抑制しつつ、浮遊ゲート電極と制御ゲート電極とのカップリング性を確保する。

【解決手段】シリコン基板11は、セル領域および周辺回路領域が設けられている。トンネル絶縁膜12は、セル領域および周辺回路領域のシリコン基板11上に形成されている。浮遊ゲート電極膜13は、セル領域および周辺回路領域のトンネル絶縁膜12上に形成されている。電極間絶縁膜16は、セル領域の浮遊ゲート電極膜13上に形成されている。シリコン酸化膜14および電極間絶縁膜16は、周辺回路領域の浮遊ゲート電極膜13上に形成されている。制御ゲート電極膜17は、セル領域および周辺回路領域の電極間絶縁膜16上に形成されている。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、且つ書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。また半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば酸化物半導体材料を用いて半導体装置を構成する。また半導体装置の各メモリセルの酸化物半導体材料を用いたトランジスタを直列に接続する。更に、第j(jは2以上m以下の自然数)のメモリセルの容量素子の端子の一方に電気的に接続される配線と、第(j−1)のメモリセルのチャネルが酸化物半導体層に形成されたトランジスタのゲート端子に電気的に接続される配線と、を同じ配線(第jのワード線)とする。これによってメモリセルあたりの配線の数を減らし、メモリセルあたりの占有面積を低減する。

(もっと読む)

半導体装置の製造方法

【課題】加工膜と非加工膜をRIE法で選択的に加工するときに、非加工膜の加工量を低減させる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層1,7,8の上に非加工膜14を形成する工程と、非加工膜14および下地層1,7,8に溝4を形成する工程と、溝内を埋め込むように加工膜5を形成する工程と、非加工膜14を露出させるように加工膜5を平坦化する工程とを備える。更に、加工膜5および非加工膜14の上に保護膜16を形成する工程と、RIE法を用いて、保護膜16をエッチングすると共に、加工膜5を選択的にエッチングして溝内の加工膜5を落とし込む工程とを備える。

(もっと読む)

半導体素子用パターン構造物の形成方法

【課題】ラインパターン構造物の形成方法を提供すること。

【解決手段】ラインパターン構造物及びその形成方法において、ラインパターン構造物は切断部位を含むライン形状を有する少なくとも1つの第1ラインパターンを含む。最外郭に位置する前記第1ラインパターンと隣り合って前記第1ラインパターンと平行した延在ラインと、前記第1ラインパターンの切断部位と隣接する領域で前記第1ラインパターン方向へ向かうように前記延在ラインから突出された少なくとも1つの突出パターンを含む2つの第2ラインパターンを含む。前記ラインパターン構造物は不良が減少し、簡単な工程を通じて形成されてもよい。

(もっと読む)

不揮発性半導体記憶装置

【課題】ゲート電極間絶縁膜のリーク電流を抑制し、電気的信頼性を向上した不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板上に行列状に形成された複数のメモリ素子と、同一列方向のメモリ素子に選択的に接続される複数のビット線と、同一行方向のメモリ素子に接続される複数のワード線とを具備し、各メモリ素子は、半導体基板上に順次形成された第1のゲート絶縁膜、電荷蓄積層、第2のゲート絶縁膜、制御電極と、電荷蓄積層の対向する側面に沿って、前記シリコン基板上面に形成された1対の不純物注入層とを具備し、ビット線に垂直な方向に沿った断面における電荷蓄積層の上部コーナー部が曲面を有し、上部コーナー部が前記第1のゲート絶縁膜の上方にある。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル領域でシリサイドの成長速度を抑制しつつ、周辺回路領域では十分な量のシリサイドを形成することのできる不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板と、メモリセル領域に形成されたメモリセルトランジスタと、周辺回路領域に形成された電界効果トランジスタとを備える。メモリセルトランジスタは、半導体基板上に第1のゲート絶縁膜を介して形成された浮遊ゲート電極と、浮遊ゲート電極上に配置される第1の電極間絶縁膜と、第1の電極間絶縁膜上に配置される制御ゲート電極とを有する。制御ゲート電極は、積層された複数の導電膜により形成される。制御ゲート電極は、積層された複数の導電膜間の界面のうちの少なくとも1つに形成され金属原子の拡散を抑制するバリア膜を有する。制御ゲート電極は、その一部がシリサイド化されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の小型化を図ること。

【解決手段】第1の領域IにフラッシュメモリセルFLを形成する工程と、第2の領域IIにキャパシタQの第1の電極11aを形成する工程と、第2の絶縁膜14として第1の酸化シリコン膜14a、窒化シリコン膜14b、及び第2の酸化シリコン膜14cをこの順に形成する工程と、第1の電極11aの一部領域CRにおける窒化シリコン膜14bと第2の酸化シリコン膜14cとを除去する工程と、第3の領域IIIHにおける第1の絶縁膜10と第2の絶縁膜14とをウエットエッチングする工程と、キャパシタQの第2の電極30aを形成する工程と、一部領域CRにおける第1の酸化シリコン膜14aをエッチングして除去する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置

【課題】キャパシタを形成する領域の占有面積を縮小する。

【解決手段】本実施形態の半導体装置は、半導体基板10内に設けられた半導体領域AACと、半導体領域AAC内に設けられる複数のキャパシタCm,Cnを含むキャパシタ群と、を具備し、キャパシタCm,Cnのそれぞれは、半導体領域AAC上のキャパシタ絶縁膜42Aと、キャパシタ絶縁膜42A上のキャパシタ電極34Am,34Amと、キャパシタ電極34Am,34Amに隣接する拡散層32Aとを有し、を有し、キャパシタ電極34Am,34Anに接続される配線29m,29nのそれぞれは、キャパシタCm,Cn毎に電気的に分離され、キャパシタ電極Cm,Cnのそれぞれに異なる電位Vm,Vnが印加されている。

(もっと読む)

フラッシュメモリアレイのワード線構造を保護するためのワード線保護装置およびフラッシュメモリアレイのためのワード線構造

【課題】製造中に、プロセスに関連する帯電からフラッシュメモリのワード線およびメモリセルを保護するための方法と構造とを与える。

【解決手段】ドープされたポリシリコンのワード線110aの端部にドープされていないポリシリコン110bが形成され、抵抗110bが生成される。これを通じて、プロセスにより生じる電荷が、基板に結合された、ドープされたポリシリコン放電構造110cへ放電される。ワード線抵抗110b、および、放電構造110cは、単一のパターニングされたポリシリコン構造として形成される。ワード線110aおよび放電部分110cは導電性になるように選択的にドープされ、また、抵抗部分110bは、製造後に通常のセル動作が可能なほどに十分高い抵抗が与えられる一方で、製造中にプロセスに関連する電荷に対しては放電路を供給するように、実質的にドープされない。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】半導体記憶装置を微細化した場合であっても、十分にカップリング比を高くする。

【解決手段】半導体記憶装置は、マトリクス状に配置されたメモリセルと複数のワード線16とを有する。メモリセル13は、行方向に複数個直列接続される。ワード線16は、複数のメモリセル13の制御ゲートを行方向と直交する列方向にそれぞれ接続する。メモリセル13の行方向の間隔は、第1の間隔と第1の間隔より広い第2の間隔とが交互に繰り返されている。

(もっと読む)

半導体装置及びその製造方法

【課題】フローティングゲートとコントロールゲートとが積層されたスタック構造のゲート電極を有する半導体装置に関し、隣接メモリセル間やメモリセルとビット線との間における短絡不良を防止しうる半導体装置及びその製造方法を提供する。

【解決手段】トンネルゲート絶縁膜22上に、第1の幅を有する導電膜24、ONO膜28、コントロールゲート40を形成する。コントロールゲート40をマスクとして導電膜24をエッチングしてフローティングゲート26を形成した後、層間絶縁膜80を形成し、第1の方向の幅が第1の幅よりも広いコンタクトホール84を形成する。その後、コンタクトホール84の内壁に、サイドウォールスペーサ88を形成する。

(もっと読む)

161 - 180 / 1,254

[ Back to top ]