Fターム[5F101BA42]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | トラップ蓄積型 (3,039) | 絶縁膜材料 (2,488)

Fターム[5F101BA42]の下位に属するFターム

単層絶縁膜 (120)

窒化膜含む (1,689)

アルミナを含むもの (327)

不純物含有 (46)

バンドギャップ、傾斜構造 (63)

Fターム[5F101BA42]に分類される特許

241 - 243 / 243

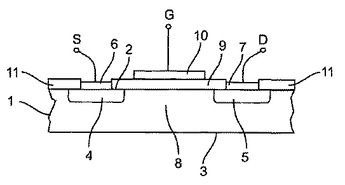

トンネル層に量子ドットを有するトランジスタ

本発明は、半導体本体(1)内に配置された半導体部品を記述したもので、前記半導体部品は、第1の導電型である少なくとも1つのソース領域(4)及び少なくとも1つのドレイン領域(5)を有し、ソース領域とドレイン領域の間に配置された第2の導電型である少なくとも1つの本体領域(8)を有し、絶縁層(9)により半導体本体から絶縁された少なくとも1つのゲート電極(10)を有し、前記絶縁層(9)は好ましくは焼結された一体化量子ドット含有層である。本発明は更に、量子ドット含有誘電性懸濁液が半導体本体に塗布され、次に例えば焼結によって一体化される上記の半導体部品の作製方法を記述する。  (もっと読む)

(もっと読む)

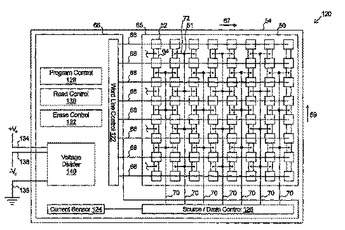

スタガー式ローカル接続構造を持つメモリセルアレイ

メモリセルアレイ(50)は、半導体基板(54)に製造された、2次元アレイのメモリセル(52)を含む。メモリセル(52)は、行方向(67)を形成する複数の行と、列方向(69)を形成する複数の列で並べられている。メモリセル(52)の各列は、複数の交互に配置されたチャネル領域(58)及びソース/ドレイン領域(64)を含む。各ソース/ドレイン領域(64)上には導電性インターコネクト(72)が配置されており、この導電性インターコネクト(72)はただ1つのその他のソース/ドレイン領域(64)に結合する。この1つのソース/ドレイン領域(64)とは、その列に隣接する第2の列に存在する領域である。導電性インターコネクト(64)は、1つおきの導電性インターコネクト(64)がその列の右側に隣接する列に接続するように、また、1つおきの導電性インターコネクトが、その列の左側に隣接する列に接続するように、配置される。複数のソース/ドレインコントロールライン(70)は、隣接するメモリセル(52)の列間に延在し、また、その隣接する列と列との間を結合する各導電性インターコネクト(72)に電気的に結合する。  (もっと読む)

(もっと読む)

電界効果トランジスタ及びその製造方法

SiC基板1と、SiC基板1表面に形成されたソース3a及びドレイン3bと、SiC表面に接して形成され厚さが1分子層以上のAlN層5と、その上に形成されたSiO2層とを有する絶縁構造と、この絶縁構造上に形成されたゲート電極15とを有しており、SiCとの間の界面状態を良好に保ちつつ、リーク電流を抑制することができる。 (もっと読む)

241 - 243 / 243

[ Back to top ]