Fターム[5F101BA42]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | トラップ蓄積型 (3,039) | 絶縁膜材料 (2,488)

Fターム[5F101BA42]の下位に属するFターム

単層絶縁膜 (120)

窒化膜含む (1,689)

アルミナを含むもの (327)

不純物含有 (46)

バンドギャップ、傾斜構造 (63)

Fターム[5F101BA42]に分類される特許

81 - 100 / 243

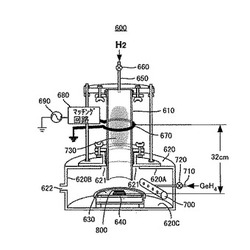

半導体製造装置、ゲルマニウムドットの製造方法およびそれを用いた半導体メモリの製造方法

【課題】ゲルマニウムからなるドットの密度を向上可能な半導体製造装置を提供する。

【解決手段】半導体製造装置600は、石英管610と、反応室620と、石英管610内へH2ガスを供給する配管650と、石英管610内にリモート水素プラズマを生成するアンテナ670、マッチング回路680および高周波電源690と、反応室620内で基板800を保持する基板ホルダー630と、基板800を加熱するヒーター640と、ゲルマンガスを基板800の近傍に供給する噴出器700および配管710とを備える。

(もっと読む)

メモリセルの電荷貯蔵層の製造プロセス

【課題】新規な電荷貯蔵フィルム(又は層)のアーキテクチャ、及び先行技術の欠点を克服できるこのアーキテクチャの製造プロセスを提供する。

【解決手段】メモリセルの金属粒子を含む電荷貯蔵層を製造するプロセスであって、前記層が、表面に前記金属粒子を含む有機層からなり、前記プロセスが:金属、半導体又は電気絶縁基板上に、カチオン形態にて少なくとも1つの金属元素を錯化できる基を表面に含む有機層37をグラフトする工程;前記層を、カチオン形態にて前記金属元素を含む溶液と接触させることによって、前記金属元素を前述の基によって錯化する工程;及び前記錯化金属元素を酸化状態0の金属元素に還元することによって、金属粒子39を得る工程を含む、プロセス。

(もっと読む)

半導体装置

【課題】電極間絶縁膜として高誘電率絶縁膜を用いた場合における隣接する電荷蓄積層間の寄生容量の増加を抑制できる半導体装置を提供すること。

【解決手段】半導体装置は、半導体基板1と、半導体基板1上に設けられたメモリセルアレイであって、ワード線方向に複数の不揮発性メモリセルが第1の絶縁膜10を介して並んだメモリセル列を含み、複数の不揮発性メモリセルの各々は、トンネル絶縁膜2と、電荷蓄積層3と、誘電率が7以上またはシリコン窒化膜の誘電率よりも高い第2の絶縁膜5と、制御電極6とを備え、第2の絶縁膜5のワード線方向の幅が、電荷蓄積層3の上面から該上面と対向する制御ゲート電極6の対向面に向かって単調に増加し、かつ、前記メモリセル列中のワード線方向に隣接する二つの不揮発性メモリセルの二つの第2の絶縁膜5が、制御ゲート電極6の下面において離れている前記メモリセルアレイとを備えている。

(もっと読む)

メモリ装置

【課題】電荷トラップ層からのトンネル効果による電子の漏れを抑制することができ、データの保持時間の長期化を図ることができるとともに、トンネル酸化膜の薄膜化を可能として、データの書き込み速度の向上を図ることのできるメモリ装置を提供する。

【解決手段】シリコン層と、シリコン層と接して設けられたゲート絶縁膜と、ゲート絶縁膜に接して設けられたゲート電極とを有するメモリ素子を具備したメモリ装置において、ゲート絶縁膜は、トンネル酸化膜、電荷トラップ膜、ブロック酸化膜の3層を積層して構成されたゲート絶縁膜であり、ゲート電極は、ブロック酸化膜上に形成されたゲート電極であって、シリコン層が、当該シリコン層の厚さが2nm以上14nm以下となるように、ゲート絶縁膜によって挟まれた部分、又はゲート絶縁膜と他の絶縁膜とによって挟まれた部分を有する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】不揮発性半導体記憶装置を構成するメモリセルの縮小化および高密度化を実現することにより、製品となる不揮発性半導体記憶装置のさらなる小型化を達成できる技術を提供する。

【解決手段】メモリセルMC1とメモリセルMC2の間に自己整合的にソース配線SLを形成する。具体的には、メモリゲート電極MG1の側壁に形成されているサイドウォールSWと、メモリゲート電極MG2の側壁に形成されているサイドウォールSWの両方に自己整合的に接触するようにソース配線SLを形成する。さらに、メモリゲート電極MG1、MG2、MGだけでなく、コントロールゲート電極CG1、CG2、CGもサイドウォール形状にする。

(もっと読む)

不揮発性半導体記憶装置及びその駆動方法

【課題】半導体層と絶縁膜との間の界面の特性を改善した不揮発性半導体記憶装置及びその駆動方法を提供する。

【解決手段】不揮発性半導体記憶装置101は、チャネル1aとチャネル1aの両側に設けられたソース領域及びドレイン領域2とを有する半導体層1と、チャネル1aの上に設けられた第1絶縁膜3Aと、第1絶縁膜3Aの上に設けられた電荷保持層3Bと、電荷保持層3Bの上に設けられた第2絶縁膜3Cと、第2絶縁膜3Cの上に設けられたゲート電極4と、を有するメモリセルと、ゲート電極4と半導体層1との間に、一定の振幅と一定の周波数とを有するバースト信号を印加し、電荷保持層に電荷の書き込み及び消去の少なくともいずれかの処理を行う駆動部20と、を備える。

(もっと読む)

不揮発性半導体記憶装置及びその駆動方法

【課題】メモリセル内に保持する電荷の、チャネルに対して垂直方向の位置を情報量として利用するNAND型の不揮発性半導体記憶装置及びその駆動方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1チャネル8aと、第1チャネル8aの両側に設けられたソース領域及びドレイン領域5aと、を有する半導体基板1aと、第1チャネル8aの上に設けられた第1絶縁膜3aと、第1絶縁膜3aの上に設けられた電荷保持層4と、電荷保持層4の上に設けられた第2絶縁膜3bと、第2絶縁膜3bの上に設けられた第2チャネル8bと、第2チャネル8bの両側に設けられたソース領域及びドレイン領域と、を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置の信頼性を向上できる技術を提供することにあり、特に、スプリットゲート型トランジスタのメモリゲート電極への給電を確実に行なうことができる技術を提供する。

【解決手段】給電配線ESLは、給電配線ESLの一端を終端部TE1上に配置し、かつ、給電配線ESLの他端を終端部TE2上に配置し、さらに、給電配線ESLの中央部をダミー部DMY上に配置している。つまり、終端部TE1と終端部TE2およびダミー部DMYはほぼ同じ高さであるので、終端部TE1上からダミー部DMY上を介して終端部TE2上に配置されている給電配線ESLの大部分は同じ高さに形成される。

(もっと読む)

半導体記憶素子、半導体記憶素子の製造方法

【課題】従来のSiNを用いた電荷蓄積膜に比べ、高効率に電荷を蓄積および消去でき、かつ、蓄積した電荷を長時間保持する半導体記憶素子、半導体記憶素子の製造方法を得る。

【解決手段】この半導体記憶素子は、半導体基板に設けられたソース領域およびドレイン領域と、ソース領域およびドレイン領域との間の半導体基板上に設けられたトンネル絶縁膜と、トンネル絶縁膜上に設けられた電荷蓄積膜と、電荷蓄積膜上に設けられたブロック絶縁膜と、ブロック絶縁膜上に設けられたゲート電極と、電荷蓄積層とブロック絶縁膜との界面付近に設けられた気体分子を含む領域とを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】下層の絶縁膜が窒化するのを抑制するとともに上層の絶縁膜からの酸素の拡散を抑制して電荷捕獲密度の低下を可及的に防止することを可能にする。

【解決手段】第1絶縁膜2と、第1絶縁膜上に形成され、窒素が添加されたアモルファスシリコン層4aと、アモルファスシリコン層上に形成された第1窒化シリコン層4bと、第1窒化シリコン層上に形成された第2絶縁膜10と、を備えていることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】最適化されたトンネル絶縁膜を有する半導体装置を提供する。

【解決手段】半導体領域101と、半導体領域の表面に形成されたトンネル絶縁膜103と、トンネル絶縁膜の表面に形成され、シリコン及び窒素を含有する電荷蓄積絶縁膜104と、電荷蓄積絶縁膜の表面に形成されたブロック絶縁膜105と、ブロック絶縁膜の表面に形成された制御ゲート電極106と、を備え、トンネル絶縁膜は、半導体領域の表面に形成され、シリコン及び酸素を含有する第1の絶縁膜103aと、第1の絶縁膜の表面に形成された第2の絶縁膜103bと、第2の絶縁膜の表面に形成され、シリコン及び酸素を含有する第3の絶縁膜103cと、を有し、第2の絶縁膜中の電荷トラップ準位密度は、電荷蓄積絶縁膜中の電荷トラップ準位密度よりも低い。

(もっと読む)

半導体記憶装置

【課題】高集積化することができるチャージトラップ型フラッシュ構造の半導体記憶装置を提供する。

【解決手段】半導体記憶装置70には、半導体基板1の第1主面(表面)にゲート絶縁膜2、電荷蓄積膜3、高誘電率絶縁膜4、ゲート電極膜5、及び絶縁膜6が積層形成される。高誘電率絶縁膜4は、底部が上部より広い台形形状を有する。ゲート電極膜5及び絶縁膜6は、高誘電率絶縁膜4の底部端よりも内側に形成される。メモリセルトランジスタMTRのゲート長とメモリセルトランジスタMTRのゲート間は60nm以下に形成される。メモリセルトランジスタMTRのゲート間にはソース或いはドレインが設けられず、メモリセルトランジスタMTRの書き込み動作及び読み出し動作時では、発生する反転層31がソース或いはドレインの代わりをする。

(もっと読む)

不揮発性半導体記憶装置

【課題】ブロック絶縁膜の高電界リーク電流特性と低電界リーク電流特性の双方を同時に改善し、書き込み・消去及びリテンション特性の優れたメモリセル構造を提供する。

【解決手段】本発明の例に係る不揮発性半導体記憶装置は、チャネル上の第1絶縁膜102上に配置される電荷蓄積層103と、電荷蓄積層103上に配置され、複数層から構成される第2絶縁膜107と、第2絶縁膜107上に配置される制御ゲート電極108,109とを備える。第2絶縁膜107は、電荷蓄積層103の直上に配置される最下層(A)104、最下層(A)104上に配置される中間層(B)117及び中間層(B)117上に配置される最上層(C)106を含み、中間層(B)117は、(SiO2)x(Si3N4)1-x (0.75≦x≦1)で表される材料から構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の特性を向上させる。

【解決手段】電荷蓄積膜MI1に対して電荷を授受することで記憶動作を行う不揮発性メモリセルNVM1を有する半導体装置であって、不揮発性メモリセルNVM1は、シリコン基板1の主面s1に形成されたpウェルpw1と、主面s1上に電荷蓄積膜MI1を隔てて形成されたメモリゲート電極MG1とを有し、更に、シリコン基板1の主面s1のうち、電荷蓄積膜MI1下に位置するメモリチャネル領域ch1aにフッ素を含んでいる。

(もっと読む)

半導体記憶装置、及びその製造方法

【課題】動作信頼性を向上させる半導体記憶装置を提供すること。

【解決手段】基板10上にゲート膜を介在して形成された蓄積層と、前記蓄積層上に形成された第1絶縁膜16と、前記第1絶縁膜16上に形成された制御ゲート17とを含むゲート電極と、ソース及びドレインとして機能する不純物拡散層13とを備えた複数のメモリセルと、前記ゲート電極17の側面上に形成され、少なくとも前記第1絶縁膜の側面を被覆するように、且つ前記第1絶縁膜と前記制御ゲートとの間に形成されたバリア膜18、19と、前記基板10上に形成され、隣接する前記メモリセルの前記ゲート電極17間を埋設する第2絶縁膜21とを具備し、前記バリア膜は、前記メモリセルのアニール時に前記第1絶縁膜16への前記第2絶縁膜21及び前記制御ゲート17を構成する原子が拡散することを防止する材料を用いて形成される。

(もっと読む)

フラーレン誘導体組成物とこれを用いた電界効果トランジスタ素子

【課題】特定のフラーレン誘導体を用いたメソフェーズを有する組成物、および、その新しい用途を提供する。

【解決手段】複数のフラーレン誘導体からなる組成物であり、上記複数のフラーレン誘導体のそれぞれは、フラーレン部位と、フラーレン部位の含窒素五員環に結合したアルキル置換基部位との結合からなり、メソフェーズを有することを特徴とする。

(もっと読む)

半導体装置

【課題】リーク電流を抑制することが可能な半導体装置を提供する。

【解決手段】半導体装置は、素子領域20と、素子領域20上に形成されたトンネル絶縁膜30と、トンネル絶縁膜30上に形成された電荷蓄積絶縁膜40と、電荷蓄積絶縁膜40上に形成されたブロック絶縁膜60と、ブロック絶縁膜60上に形成された制御ゲート電極70と、を備えた第1及び第2のメモリセルと、第1及び第2のメモリセルの素子領域20、トンネル絶縁膜30及び電荷蓄積絶縁膜40の間に形成された素子分離領域20と、を具備し、ブロック絶縁膜60は、金属元素及び酸素を主成分として含有する第1の絶縁膜61と、シリコン及び酸素を主成分として含有する第2の絶縁膜62とで形成され、ブロック絶縁膜60の少なくとも一部は、素子分離領域50上に形成されていることを特徴とする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】データ記憶用の電荷蓄積絶縁膜を備える半導体記憶装置に関し、リーク電流の低減と好適な消去動作とを両立する。

【解決手段】ビット線とワード線とを有する半導体記憶装置であって、基板111と、前記基板上に形成された第1のゲート絶縁膜121と、前記第1のゲート絶縁膜上に形成された電荷蓄積絶縁膜122と、前記電荷蓄積絶縁膜上に形成され、ビット線方向の幅が、前記電荷蓄積絶縁膜のビット線方向の幅よりも広い第2のゲート絶縁膜123と、前記第2のゲート絶縁膜上に形成され、ビット線方向の幅が、前記電荷蓄積絶縁膜のビット線方向の幅よりも狭く、且つ、前記第2のゲート絶縁膜のビット線方向の幅よりも狭いゲート電極124と、前記ゲート電極のビット線方向の側面に形成された側壁絶縁膜131とを備えることを特徴とする半導体記憶装置。

(もっと読む)

半導体装置の作製方法

【課題】薄型化及び小型化を達成しながら、外部ストレス、及び静電気放電に耐性を有する信頼性の高い半導体装置を提供することを目的の一とする。また、作製工程においても外部ストレス、又は静電気放電に起因する形状や特性の不良を防ぎ、歩留まり良く半導体装置を作製することを目的の一とする。さらに低コストで生産性高く半導体装置を作製することを目的の一とする。

【解決手段】半導体集積回路を囲いこむように覆う導電性遮蔽体により、半導体集積回路の静電気放電による静電気破壊(回路の誤動作や半導体素子の損傷)を防止する。導電性遮蔽体はめっき法により電気的に接続するように形成する。また、導電性遮蔽体の形成にめっき法を用いるために、低コストで生産性高く半導体装置を作製することができる。

(もっと読む)

金属酸化物絶縁膜の成膜方法

【課題】不揮発性半導体メモリ素子向けの絶縁膜形成において、リーク電流密度を低減でき、デバイス特性及び信頼性を向上させることができる金属酸化物絶縁膜の成膜方法を提供する。

【解決手段】Kr以上の原子量を有する希ガスを導入して、導入希ガスより重い金属元素を含む金属酸化物ターゲットを用い、LaHfO、LaAlO、ZrAlOのように導入希ガスより重いLaまたはHfなどの金属元素を含む金属酸化物絶縁膜をスパッタ成膜する。

(もっと読む)

81 - 100 / 243

[ Back to top ]