Fターム[5F101BA42]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | トラップ蓄積型 (3,039) | 絶縁膜材料 (2,488)

Fターム[5F101BA42]の下位に属するFターム

単層絶縁膜 (120)

窒化膜含む (1,689)

アルミナを含むもの (327)

不純物含有 (46)

バンドギャップ、傾斜構造 (63)

Fターム[5F101BA42]に分類される特許

21 - 40 / 243

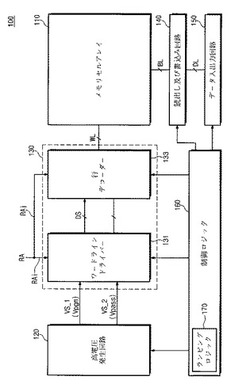

不揮発性メモリ装置

【課題】一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供することによって、読出しマージン減少による信頼性の下落を防止できる不揮発性メモリ装置が提供される。

【解決手段】本発明の実施形態による不揮発性メモリ装置は、基板と直交する方向に積層された複数のメモリセルを含むメモリセルアレイと、ワードラインを通じて前記メモリセルアレイに連結された行選択回路と、前記ワードラインに提供される電圧を発生する電圧発生回路と、を含み、前記電圧発生回路は、目標電圧レベルまで段階的に増加させる方式に前記電圧を発生する。本発明の実施形態による不揮発性メモリ装置は、一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供できる。したがって、読出しマージン減少による信頼性の下落が防止され得る。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込み時間の短縮及び読み出し電圧の上昇の抑制を図る不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリ部と、制御部と、を備える。メモリ部は、積層構造体と、半導体ピラーと、記憶層と、内側絶縁膜と、外側絶縁膜と、メモリセルトランジスタと、を有する。制御部は、メモリセルトランジスタの各閾値を正または負の一方に設定する制御、及び各閾値のうち0ボルトから最も離れた第n閾値の分布の幅よりも、第n閾値と同じ符号の第m(mはnよりも小さい1以上の整数)閾値の分布の幅を狭く設定する制御を行う。

(もっと読む)

半導体記憶装置の製造方法

【課題】製造が容易なNAND型半導体記憶装置の製造方法を提供する。

【解決手段】製造方法は、基板101上に第1絶縁膜105及び第2絶縁膜106を交互に積層して積層体110を形成する工程と、第1絶縁膜105及び第2絶縁膜106の積層方向に延び、積層体110を貫通する貫通孔114を形成する工程と、貫通孔114の内面上に、MONOS116を構成するブロック絶縁膜、チャージトラップ膜及びトンネル誘電体膜の少なくとも一部を形成する工程と、トンネル誘電体膜上にチャネル半導体117を形成する工程と、積層体110にトレンチ121を形成する工程と、トレンチ121を介してエッチングを施すことにより、第2絶縁膜106を除去する工程と、第2絶縁膜106を除去した後の空間内に導電材料を埋め込む工程と、を備える。

(もっと読む)

不揮発性記憶素子及びその製造方法

【課題】 信頼性を向上可能な不揮発性記憶素子及びその製造方法を提供する。

【解決手段】 不揮発性素子は、基板100、基板100の上に形成され、制御ベースゲート120a及び制御ベースゲート120aの上に形成される制御金属ゲート125anを有する制御ゲート電極137、制御ゲート電極137と基板100との間に形成される電荷格納領域110a、制御ゲート電極137の上に形成される制御ゲートマスクパターン130、及び制御ゲートマスクパターン130及び制御ベースゲート120aの間に形成された制御金属ゲート125aの側壁の上に形成される酸化防止スペーサ135aを備える。このとき、制御金属ゲート125anの幅は、制御ゲートマスクパターン130の幅より小さくなるように形成されている。これにより、制御金属ゲート125anが酸化工程又は酸化物等によって酸化されることを防止することができる。

(もっと読む)

帯電体並びにそれを用いた電界効果トランジスタ及びメモリ素子

【課題】 フローティングゲートメモリやMNOSメモリのような極薄膜の絶縁層を必要とせず、印刷、塗布でメモリ素子が製造可能となる簡便で、注入電荷量の制御が容易な帯電体、並びにこの帯電体をゲート絶縁膜に用いてFETを作製することにより、閾値電圧制御が可能で、長時間制御された閾値電圧状態を保持可能なFET及びメモリ素子を提供する。

【解決手段】 電荷注入が生じる電界強度(以降、電荷注入耐圧)および絶縁耐圧がそれぞれECI,HおよびEBHである絶縁体(以下,高電荷注入耐圧材料)と、その電荷注入耐圧ECI,LがECI,L < ECl,Hの関係にある絶縁体(以下、低電荷注入耐圧材料)の二種類の絶縁体を積層した絶縁物で、高電荷注入耐圧材料と低電荷注入耐圧材料のそれぞれに接し離れた2枚の電極にECI,L < |E| < EBH の電界強度で電圧を印加して低電荷注入耐圧材料側から電荷を絶縁体内に注入して帯電させる帯電体。

(もっと読む)

半導体装置の製造方法

【課題】ウィンドウ特性の向上とリテンション特性の向上とを同時に図ることのできる半導体装置の製造方法を提供する。

【解決手段】シリコン基板上に、トンネル酸化膜、チャージトラップ膜、ブロッキング酸化膜、ゲート電極が、下側からこの順で形成された積層構造を有する半導体装置を製造する方法であって、前記ブロッキング酸化膜を形成する工程が、前記チャージトラップ膜上に結晶質膜を形成する結晶質膜形成工程と、前記結晶質膜の上層にアモルファス膜を形成するアモルファス膜形成工程とを具備し、前記結晶質膜形成工程と、前記アモルファス膜形成工程とを同一の処理容器内で連続的に行う。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】特性を向上させる不揮発性メモリを有する半導体装置を提供する。

【解決手段】半導体装置を、制御ゲート電極CGと、制御ゲート電極CGと隣合うように配置されたメモリゲート電極MGと、絶縁膜3と、その内部に電荷蓄積部を有する絶縁膜5と、を有するよう構成する。このうち、メモリゲート電極MGは、絶縁膜5上に位置する第1シリコン領域6aと、第1シリコン領域6aの上方に位置する第2シリコン領域6bと、を有するシリコン膜よりなり、第2シリコン領域6bは、p型不純物を含有し、第1シリコン領域6aのp型不純物の濃度は、第2シリコン領域6bのp型不純物の濃度よりも低く構成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】集積度を向上させた不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1積層構造体と、第1半導体層と、第1有機膜と、第1半導体側絶縁膜と、第1電極側絶縁膜と、を備えた不揮発性半導体記憶装置が提供される。前記第1積層構造体は、第1方向に沿って積層された複数の第1電極膜と、前記複数の第1電極膜どうしの間に設けられた第1電極間絶縁膜と、を有する。前記第1半導体層は、前記複数の第1電極膜の側面に対向する。前記第1有機膜は、前記複数の第1電極膜の前記側面と前記第1半導体層との間に設けられ有機化合物を含む。前記第1半導体側絶縁膜は、前記第1有機膜と前記第1半導体層との間に設けられる。前記第1電極側絶縁膜は、前記第1有機膜と前記複数の第1電極膜の前記側面との間に設けられる。

(もっと読む)

半導体装置

【課題】パーコレーションリークを抑制可能な構造を有する半導体装置を提供する。

【解決手段】ソース領域18、ドレイン領域18及びチャネル領域を有する半導体領域と、チャネル領域上に形成された第1のトンネル絶縁膜12と、第1のトンネル絶縁膜上に形成され、エネルギー障壁を有する障壁層13と、障壁層上に形成された第2のトンネル絶縁膜14と、第2のトンネル絶縁膜上に形成され、SiY(SiO2)X(Si3N4)1-X (ただし、0≦X≦1、Y>0)で表される絶縁膜を具備する電荷蓄積部15と、電荷蓄積部上に形成され、エネルギー障壁の高さを制御する制御電極17とを備え、X及びYは、[2×2X/(4−2X)+(4−4X)/(4−2X)]×[Y/(Y+7−4X)]≧0.016 なる関係を満たし、障壁層は、クーロンブロッケイド条件を満たす導電性微粒子を含んだ微粒子層で形成されている。

(もっと読む)

3次元半導体記憶素子

【課題】優れた信頼性を有し、高集積化のために最適化された3次元半導体記憶素子が提供される。

【解決手段】本発明の素子によれば、積層構造体が基板上に配置されて第1の方向に延長される。積層構造体は交互に反復的に積層されたゲートパターン及び絶縁パターンを含む。垂直形活性パターンが積層構造体を貫通する。積層構造体は第1の部分及び第2の部分を含み、積層構造体の第2の部分は第1の方向と垂直である第2の方向に第1の部分より小さい幅を有する。積層構造体の第2の部分の横にストラッピングコンタクトプラグが配置されて、共通ソース領域と接触される。

(もっと読む)

半導体記憶装置

【課題】 本発明の実施形態によれば、プロセッサの処理速度を低下させることなく、フラッシュメモリの信頼性を維持する半導体記憶装置を提供することができる。

【解決手段】 第1の電極に第1の電位を与え、全てのバックゲート電極に第1の電位よりも低い第2の電位を与え、第1乃至第n−1のフロントゲート電極に第1の電位よりも高い第3の電位を与え、第n以上のフロントゲート電極に第2の電位と第3の電位との間の第4の電位を与えることで半導体層に情報を書き込むことを特徴とする

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置を構成する回路を高集積度化する。

【解決手段】一つの実施形態によれば、半導体記憶装置は、半導体基板と複数のメモリセルトランジスタを有する。前記複数のメモリセルトランジスタは、前記半導体基板に設けられた深溝にトレンチゲートが埋設され、直列接続される。メモリセルの書き込み動作及び読み出し動作のとき、トレンチゲートの周囲及び間の前記半導体基板の領域に、前記半導体基板とは逆導電型の反転層が形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込みを高速化した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置110は、ベース半導体層10aと、電極70aと、チャネル半導体層30aと、ベーストンネル絶縁膜20aと、チャネルトンネル絶縁膜40aと、電荷保持層50aと、ブロック絶縁膜60aと、を有するメモリ部MC1を備える。チャネル半導体層30aは、ベース半導体層10aと電極70aとの間に設けられ、電極70aに対向するチャネル部31aを含む。ベーストンネル絶縁膜20aは、ベース半導体層10aとチャネル半導体層30aとの間に設けられる。チャネルトンネル絶縁膜40aは、電極70aとチャネル部31aとの間に設けられる。電荷保持層50aは、電極70aとチャネルトンネル絶縁膜40aとの間に設けられ、電荷を保持する。ブロック絶縁膜60aは、電極70aと電荷保持層50aとの間に設けられる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】生産性を向上した一括加工型3次元積層メモリ構成の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、積層構造体MLと、選択ゲート電極SGと、半導体ピラーSPと、記憶層48と、内側絶縁膜42と、外側絶縁膜43と、選択ゲート絶縁膜SGIと、を備えた不揮発性半導体記憶装置が提供される。積層構造体は、第1方向に積層された複数の電極膜61と、電極間絶縁膜62と、を有する。選択ゲート電極は、積層構造体と積層された複数の選択ゲート導電膜71と、選択ゲート導電膜間絶縁膜72と、を有する。半導体ピラーは、積層構造体及び選択ゲート電極を第1方向に貫通する。記憶層は、電極膜と半導体ピラーとの間に、内側絶縁膜は、記憶層と半導体ピラーとの間に、外側絶縁膜は、記憶層と電極膜との間に、選択ゲート絶縁膜は、選択ゲート導電膜と半導体ピラーとの間に設けられる。

(もっと読む)

不揮発性記憶素子

【課題】本発明は、中間絶縁層、電荷蓄積層、及びトンネル絶縁層のうちの少なくとも1つが酸化ガリウムを含まない場合に比べて、情報の書込みと消去を繰り返しても閾値電圧の変動が抑制された不揮発性記憶素子を提供する。

【解決手段】基板と、ソース電極と、ドレイン電極と、チャネル層と、電荷蓄積層と、ゲート電極と、前記チャネル層及び前記電荷蓄積層の間に設けられたトンネル絶縁層と、前記電荷蓄積層及び前記ゲート電極の間に設けられた、中間絶縁層と、を備え、前記中間絶縁層、前記電荷蓄積層、及び前記トンネル絶縁層が酸化ガリウムを含み、前記チャネル層が有機半導体層である不揮発性記憶素子である。

(もっと読む)

不揮発性メモリー装置、そのプログラム方法、不揮発性メモリー装置を含むメモリーシステム、電子装置及びシステム

【課題】カップリングノイズ、Vpass障害、及びVpgm障害による閾値電圧の変化を減らすことができる不揮発性メモリー装置、そのプログラム方法、不揮発性メモリー装置を含むメモリーシステム、電子装置及びシステムを提供する。

【解決手段】本発明の不揮発性メモリー装置は、複数の物理ページで構成されるメモリーセルアレイと、複数の物理ページが一次的にプログラムされた後に複数の物理ページが二次的にプログラムされるようにプログラム順序を定めるためのプログラムシーケンサーと、を備え、一次的なプログラム動作のプログラム状態P0は、二次的なプログラム動作のビットラインセットアップ区間で複数の物理ページに印加されるワードライン電圧より低いことを特徴とする。

(もっと読む)

半導体装置

【課題】不揮発性メモリと容量素子を有し、性能を向上させる半導体装置を提供する。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MG6nとp型ウエルPW1との間および制御ゲート電極CG4nとメモリゲート電極MG6nとの間には、内部に電荷蓄積層5bを有する絶縁膜5が形成されている。この絶縁膜5は、酸化シリコン膜5aと、その上に形成された窒化シリコン膜5bと、その上に形成された酸化シリコン膜5cと、その上に形成されかつ酸化シリコン膜5cよりも薄い絶縁膜5dとの積層膜からなる。この絶縁膜5dは、ポリシリコンからなるメモリゲート電極MG6nに接している。絶縁膜5dは、Hf,Zr,Al,Ta,Laのうちの少なくとも1種を含む金属化合物により形成されているため、フェルミピニングを生じることができ、誘電率が高い。

(もっと読む)

半導体記憶素子、及び半導体記憶装置

【課題】 高効率に電荷を蓄積及び消去することができ、かつ蓄積した電荷を長時間保持することができる半導体記憶素子、及び半導体記憶装置を提供する

【解決手段】 半導体層19と、半導体層19上に設けられたトンネル絶縁膜18と、トンネル絶縁膜18上に設けられ、膜厚が0.9nm以上2.8nm以下であり、立方晶ハフニア粒子17を含む電荷蓄積膜16と、電荷蓄積膜16上に設けられたブロック絶縁膜15と、ブロック絶縁膜15上に設けられた制御電極13とを備えることを特徴とする半導体記憶素子。

(もっと読む)

半導体装置およびその製造方法

【課題】電荷を蓄積可能な電荷蓄積膜を有する不揮発性メモリセルを含む半導体装置において、データ保持特性劣化を改善し、その信頼性を向上させることにある。

【解決手段】半導体基板の主面に不揮発性メモリセルを含む半導体装置であって、不揮発性メモリセルは、半導体基板上に第1絶縁膜と、導電膜と、第2絶縁膜と、電荷を蓄積可能な電荷蓄積膜とを有する。また、電荷蓄積膜上に第3絶縁膜と、第1ゲート電極と、第1絶縁膜から前記第1ゲート電極までの一連の積層膜と接するように第4絶縁膜と、第1絶縁膜と並ぶように前記半導体基板上に第5絶縁膜とを有する。さらに、第5絶縁膜上に形成され、第4絶縁膜の側面に前記第1ゲート電極と隣り合うように第2ゲート電極と、第1ゲート電極と第2ゲート電極を挟むように半導体基板にソース領域およびドレイン領域とを有する。半導体装置は、導電膜と電荷蓄積膜が平面的に重なり合うように形成されている。

(もっと読む)

半導体記憶装置、及びその製造方法

【課題】 高効率に電荷を蓄積及び消去することができ、かつ蓄積した電荷を長時間保持することができる半導体記憶装置、及びその製造方法を提供する。

【解決手段】 半導体記憶装置10は、半導体基板11と、半導体基板11内に離間して設けられたソース領域3及びドレイン領域2と、ソース領域3とドレイン領域2との間であって半導体基板11上に設けられたトンネル絶縁膜12と、トンネル絶縁膜12上に設けられ、酸化物クラスターを含む電荷蓄積膜13と、電荷蓄積膜13上に設けられたブロック絶縁膜14と、ブロック絶縁膜14上に設けられたゲート電極15とを備える。

(もっと読む)

21 - 40 / 243

[ Back to top ]