Fターム[5F101BD35]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | 分離 (2,126)

Fターム[5F101BD35]の下位に属するFターム

ウェル (283)

LOCOS (105)

ガードリング寄生チャンネル防止拡散 (21)

Fターム[5F101BD35]に分類される特許

161 - 180 / 1,717

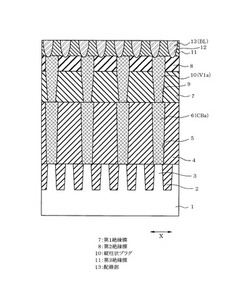

半導体装置およびその製造方法

【課題】配線部を通じた信号伝搬速度を向上できるようにした半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板上に形成された第1絶縁膜と、前記第1絶縁膜上に形成された、前記第1絶縁膜より比誘電率が高い第2絶縁膜と、前記第2絶縁膜と隣接する側面が順テーパ形状を有し、前記第1絶縁膜および前記第2絶縁膜を貫通して形成された複数の縦柱状プラグと、前記第2絶縁膜上に形成された、前記第2絶縁膜よりも比誘電率が低い第3絶縁膜と、前記複数の縦柱状プラグの上部に到達するように前記第3絶縁膜に形成された複数の溝と、前記複数の溝内にそれぞれ形成され、前記複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部と、を備える。

(もっと読む)

電子部品の製造方法

【課題】導電膜を含む層の加工によって密の配線と疎の配線とが混在して形成された配線層で、所望の配線間の領域にのみ空隙を形成することができる電子部品の製造方法を提供する。

【解決手段】実施形態によれば、電子部品の製造方法は、まず、密の配線と疎の配線とを含む配線パターンとなるように、基板1上の導電性材料膜を含む加工対象を加工する。ついで、密の配線の形成領域にのみ配線間を埋め込む犠牲膜111を形成した後、基板1上に絶縁膜112を形成する。絶縁膜112上にレジスト113を塗布し、密の配線の形成領域上の一部と疎の配線の形成領域とが露出するようにレジスト113のパターニングを行った後、レジスト113をマスクとして絶縁膜112をエッチングする。さらに、密の配線の形成領域上の一部を通して、犠牲膜111を除去する。そして、疎の配線の形成領域で隣接する配線間を埋め込むように基板1上に埋込絶縁膜114を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク電流の発生を防止でき、微細化に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、素子分離膜により分離される素子領域を有する半導体基板31と、前記素子領域上にゲート絶縁膜を介して設けられる第1導電層FGと、前記第1導電層および前記素子分離膜上に設けられ、前記第1導電層上に開口を有するゲート間絶縁膜IPDと、前記ゲート間絶縁膜を介して、前記素子領域上および前記素子分離膜上にわたって配置される第2導電層CG1と、前記第1導電層上に設けられ、周囲の溝により前記第2導電層と電気的に分離され、前記ゲート間絶縁膜の前記開口を介して前記第1導電層と接続される第3導電層CG2と、前記第1導電層を挟むように、前記素子領域中に隔離して設けられるソースまたはドレイン拡散層38とを具備する。

(もっと読む)

半導体記憶装置

【課題】メモリアレイの周辺に配置される周辺回路の専有面積を小さくすることができる半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、メモリアレイと、周辺回路と、を備える。メモリアレイは、複数のメモリセルと、複数のワード線と、複数のビット線と、を有し、4つのブロックを有する。周辺回路は、第1ブロックに属するワード線に接続された第1転送トランジスタと、第2ブロックに属する前記ワード線に接続された第2転送トランジスタと、第3ブロックに属するワード線に接続された第3転送トランジスタと、を含むトランジスタグループを有する。第1〜第3転送トランジスタにおいては、それぞれのソース及びドレインのいずれか他方を共有し、ソース及びドレインのいずれか一方と他方とをむすぶ方向が隣り合う転送トランジスタどうしで互いに90°または180°異なる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体記憶装置

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

フローティングゲート半導体メモリデバイスおよびそのようなデバイスの製造方法

【課題】NANDフラッシュメモリデバイスを電気的、物理的に小型化し、良好なデータ保持と電気的特性を備えたフローティングゲートデバイスを提供する。

【解決手段】フローティングゲートメモリデバイスの製造方法に関し、ベース基板100、埋め込み絶縁層、および単結晶半導体上部層から形成される、半導体−オン−絶縁体基板が提供される。トレンチが基板中に形成され、フローティングゲートとして働く単結晶上部部分を有する高層フィン型構造111−114を形成する。埋め込み絶縁層の一部は、フローティングゲートデバイスのトンネル酸化物層101’として働く。ゲート誘電体層160は、熱酸化により単結晶上部部分の側壁の上に形成され、薄い膜厚のゲート誘電体層を可能にする。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲート電極および当該選択ゲート電極に隣接する他のゲート電極間の間隔を所望の距離に調整できるようにした不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】複数本のラインパターンのうち選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてマスクした条件にて複数本のラインパターンの側壁面をスリミングし、選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてパターン間膜を埋込むと共にスリミングされたラインパターンの側壁面に沿ってパターン間膜を形成し、選択ゲート電極の形成領域のラインパターンをマスクした条件にて当該ラインパターン以外のラインパターンを除去しマスクされたラインパターンを残留させ、パターン間膜および残留したラインパターンをマスクとして第1膜を異方性エッチングし、第1膜をマスクとして導電膜をエッチングする不揮発性半導体記憶装置の製造方法を提供する。

(もっと読む)

不揮発性メモリ及びその製造方法

【課題】

不揮発性メモリ構造を提供する。

【解決手段】

必要に応じて、LDD領域が、アクティブ領域のゲートチャネル領域の保護のためのマスクを用いてイオン注入によって形成され得る。2つのゲートが、互いに離隔され、アクティブ領域の中央領域の2つの側方のそれぞれでアイソレーション構造上に配設される。これら2つのゲートの各々は、その全体がアイソレーション構造上に配置されてもよいし、部分的にアクティブ領域の中央領域の側方部分に重なってもよい。電荷トラップ層及び誘電体層が、格納ノード機能を果たすように、2つのゲートの間且つアクティブ領域上に形成される。これらは更に、スペーサとして機能するように、2つのゲートの全ての側壁上に形成されてもよい。ソース/ドレイン領域が、ゲート及び電荷トラップ層の保護のためのマスクを用いて、イオン注入によって形成される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】低いビットコストで積層化可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1メモリセルアレイ層10と、第1絶縁層31と、第2メモリセルアレイ層20とを有する。第1メモリセルアレイ層10は、複数の第1メモリセルMC1を具備する第1NANDセルユニットNU1を有する。第1メモリセルMC1は、第1半導体層11と、その上に形成された第1ゲート絶縁膜12と、第1浮遊ゲート13とを有する。第2メモリセルアレイ層20は、複数の第2メモリセルMC2を具備する第2NANDセルユニットNU2を有する。第2メモリセルMC2は、第2浮遊ゲート23と、第2ゲート絶縁膜22と、第2半導体層21とを有する。上下に連続する第1及び第2浮遊ゲート13,23の第1の方向の両側面に第1の方向と直交する第2の方向に延びる制御ゲート33が形成される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】動作特性の向上を図ることができる不揮発性半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコンを含む基板と、前記基板上に間隔をあけて設けられた複数のメモリセルと、前記メモリセルの側壁に形成された絶縁膜と、を備えている。そして、前記絶縁膜は、前記メモリセル同士の間に形成された空隙部の上方において、隣接する前記メモリセルに向けて突出する突出部を有している。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化した半導体集積回路において用いられるキャパシタを提供する。

【解決手段】誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する仕事関数が5.0電子ボルト以上、好ましくは5.5電子ボルト以上のn型半導体による電極を有するキャパシタである。電極の仕事関数が高いため、誘電体のポテンシャル障壁が高くなり、誘電体が10nm以下と薄くても十分な絶縁性を保てる。特に、誘電体が、high−k材料である場合に顕著な効果が認められる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】浮遊ゲートと制御ゲートとの間におけるリークを抑制することができる不揮発性半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコンを含む基板と、前記基板上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた浮遊ゲートと、前記浮遊ゲート上に設けられたリーク抑制部と、前記リーク抑制部上に設けられたゲート間絶縁膜と、前記ゲート間絶縁膜上に設けられた制御ゲートと、を備える。前記リーク抑制部の誘電率は、前記ゲート間絶縁膜の誘電率よりも高くなっている。

(もっと読む)

半導体記憶装置の製造方法

【課題】高集積化を図ることができる半導体記憶装置の製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、基板上に第1膜と第2膜とを交互に積層して第1積層体を形成する工程と、前記第1積層体上に第3膜と第4膜とを交互に積層して第2積層体を形成する工程と、前記第1膜のエッチング速度よりも前記第3膜のエッチング速度の方が低くなる条件でエッチングを施すことにより、前記第2積層体及び前記第1積層体を貫く貫通ホールを形成する工程と、前記貫通ホールの内面上に電荷蓄積膜を形成する工程と、前記貫通ホール内に半導体部材を形成する工程と、を備える。そして、前記第1膜と前記第2膜とを相互に異なる材料によって形成し、前記第3膜と前記第4膜とを相互に異なる材料によって形成し、前記第1膜と前記第3膜とを相互に異なる材料によって形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】隣接セル間干渉を抑制した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1メモリストリングと、ソースコンタクトと、第2メモリストリングと、シールド導電層と、を備えた不揮発性半導体記憶装置を提供する。第1メモリストリングは、第1軸に沿って並ぶ第1メモリセル及び第2メモリセルを含む。ソースコンタクトは、第1メモリストリングのソース側の端に設けられる。第2メモリストリングは、第1軸に対して直交する第2軸に沿って第1メモリセルと並ぶ第3メモリセルを含み、第1軸に沿って延在する。シールド導電層は、第1メモリストリングと第2メモリストリングとの間において第1軸に沿って延在し、ソースコンタクトと電気的に接続される。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コンタクトとアクティブエリアとの間のショートマージンを確保できる半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板の上層部分に形成され、前記上層部分を第1方向に延びる複数本のアクティブエリアに区画する複数本の素子分離絶縁体と、前記アクティブエリアに接続されたコンタクトと、を備える。そして、各前記アクティブエリアの上面のうち、前記第1方向における一部の領域には、前記第1方向に対して直交する第2方向において前記アクティブエリアの全体にわたって凹部が形成されている。前記第1方向において、隣り合う前記アクティブエリアにそれぞれ接続された2本の前記コンタクトの位置は相互に異なる。前記コンタクトは前記凹部の側面に接し、底面には接していない。

(もっと読む)

半導体記憶装置

【課題】動作速度が高い半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、一方向に沿って相互に平行に配列された複数枚のゲート電極膜と、前記一方向に延び、前記複数枚のゲート電極膜を貫通する半導体部材と、前記ゲート電極膜と前記半導体部材との間に設けられた電荷蓄積膜と、を備える。前記ゲート電極膜における前記半導体部材に対向した端部には、前記一方向に沿って突出した凸部が設けられており、前記ゲート電極膜間の空間の一部は気体層となっている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ゲートの端部に集中する電界を緩和し、電荷のトラップおよびトンネル絶縁膜の破壊を抑制し、信頼性を向上させる。

【解決手段】半導体記憶装置は、半導体基板上に設けられたアクティブエリアを備えている。素子分離部が、アクティブエリア間に設けられ、絶縁膜で充填されている。データを記憶する複数のメモリセルがアクティブエリアに形成されている。空洞が、アクティブエリアのメモリセルが形成された部分の上端縁部と素子分離部内の絶縁膜との間に設けられている。

(もっと読む)

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

161 - 180 / 1,717

[ Back to top ]