Fターム[5F101BE01]の内容

不揮発性半導体メモリ (42,765) | 周辺技術 (5,862) | アドレス回路デコード回路 (208)

Fターム[5F101BE01]に分類される特許

1 - 20 / 208

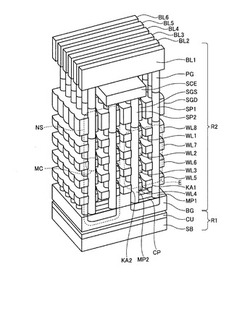

半導体装置および半導体装置の製造方法

【課題】ホールの微細化を図りつつ、ホールとスリットとを一括形成する。

【解決手段】4層分のワード線WL4〜WL1が順次積層されるとともに、ワード線WL4〜WL1にそれぞれ隣接するように4層分のワード線WL5〜WL8が順次積層され、ワード線WL5〜WL8が柱状体MP1にて貫かれるとともに、ワード線WL1〜WL4が柱状体MP2にて貫かれることで、NANDストリングNSが構成され、ワード線WL1〜WL8およびセレクトゲート電極SGD、SGSはロウ方向に沿って幅が周期的に変化されている。

(もっと読む)

不揮発性メモリ装置、不揮発性メモリ装置のプログラム方法、不揮発性メモリ装置を含むメモリシステム

【課題】向上された信頼性を有する不揮発性メモリ装置のプログラム方法が提供される。

【解決手段】本発明のプログラム方法は、第1メモリセルトランジスターの閾値電圧がプログラム状態から移動する傾向を判別する段階と、判別結果に応答して、複数の検証電圧の中で第1検証電圧を選択する段階と、第1メモリセルトランジスターの閾値電圧が変化するように第1メモリセルトランジスターをプログラムする段階と、で構成される。プログラムする段階は第1メモリセルトランジスターの閾値電圧が十分に変化されたかを第1検証電圧を利用して検証する段階を含む。判別する段階は第1メモリセルトランジスターの閾値電圧の第1範囲からの変化を判別する段階を含む。

(もっと読む)

半導体記憶装置およびデータ書込み方法

【課題】MOS構造を有する各メモリセルにおいて信頼性が高い2ビットのデータの記憶が容易な半導体記憶装置およびデータ書込み方法を提供する。

【解決手段】MOS構造を有するメモリセル10は、ゲート電極13の第1半導体領域121側に設けられた第1記憶部141と、ゲート電極13の第2半導体領域122側に設けられた第2記憶部142とを有する。第1記憶部141に電子を保持させる第1電荷移動ステップと、第2記憶部142に電子を保持させる第2電荷移動ステップとを交互に行うことで、第1記憶部141および第2記憶部142の双方に所定量の電子を保持させる。

(もっと読む)

半導体メモリ

【課題】素子間リークを低減できる半導体メモリを提供する。

【解決手段】本実施形態の半導体装置は、第1のゲート絶縁膜上の電荷蓄積層と、第1の絶縁体を介して電荷蓄積層上に設けられる制御ゲート電極とを含むメモリセルと、アクティブ領域AAH上の第2のゲート絶縁膜20Hと、第2のゲート絶縁膜上の第1の電極層21Hと、を含むトランジスタHTと、素子分離絶縁膜15H上に設けられるシールドゲート電極SIGと、を有する。シールドゲート電極SIGの底部は、素子分離絶縁膜15Hの最も高い上面より半導体基板10の底部側に位置している。

(もっと読む)

半導体メモリ及びその製造方法

【課題】素子分離絶縁膜の応力に起因する素子特性の劣化を低減する。

【解決手段】本実施形態の半導体メモリは、第1のゲート絶縁膜上の電荷蓄積層と電荷蓄積層上に積層される制御ゲート電極とを含む第1のアクティブ領域AA内のメモリセルMCと、第2のゲート絶縁膜20L上の第1の電極層21Lと、を含む、第2のアクティブ領域AAL内の第1のトランジスタLTとを具備する。第2のアクティブ領域AALを定義する第2の素子分離絶縁膜19Xは、第1の膜190と、第1の膜190と第2のアクティブ領域AALとの間の第2の膜195とを含み、第1の膜190の上面は、第2の膜195の上面よりも、半導体基板10の底部側に位置している。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】ビット線接続部の微細化を実現する不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、p型の半導体基板101と、半導体基板101内に形成され、メモリセルのビット線とセンスアンプ部を接続するビット線接続トランジスタHTkが形成されるp型の第1のPウェル102と、第1のPウェル102を囲み、第1のPウェル102を半導体基板101から電気的に分離するn型の第1のNウェル103と、を備える。

(もっと読む)

半導体記憶装置

【課題】データの読み出し速度を向上する。

【解決手段】半導体記憶装置1は、メモリセルアレー1aと、コラム線1bと、第1および第2のデータ線1d,1eと、データの読み出し時には、コラム線1bに第1および第2のデータ線1d,1eの一方を選択して接続し、データの書き込み時には、コラム線1bに第1および第2のデータ線1d,1eを接続するスイッチ1cと、第1および第2のデータ線1d,1eに接続された読み出し回路1fと、第1および第2のデータ線1d,1eに接続された書き込み回路1gと、を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】誤書込みを抑制した不揮発性半導体記憶装置を提供する。

【解決手段】制御回路は、書込み動作時、複数のビット線中の書込み禁止ビット線の電圧を第1電圧まで上げた後、書込み禁止ビット線をフローティング状態とする。続いて、制御回路は、書込み禁止ビット線以外の書込みビット線の電圧を第2電圧まで上げ、これに伴うカップリングにより書込み禁止ビット線の電圧を上げる。これにより、制御回路は、書込み禁止ビット線に対応するメモリストリング内のメモリトランジスタに対して書込み動作を禁止する。一方、制御回路は、書込みビット線に対応するメモリストリング内のメモリトランジスタに対して書込み動作を実行する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも

制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワ

イドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジス

タのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわた

って情報を保持することが可能である。また、信号線の電位変化のタイミングを、書き込

みワード線の電位変化のタイミングより遅らせる。これによって、データの書き込みミス

を防ぐことが可能である。

(もっと読む)

半導体記憶装置

【課題】高性能な乱数を生成することができ、予測困難性を向上できる半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、複数のメモリセルMCが配置されるメモリセルアレイ11と、乱数(Random number)を発生させる乱数発生回路16と、メモリセルアレイ11および乱数発生回路16を制御するコントローラ19とを少なくとも具備する。乱数発生回路16は、生成した制御パラメータ(Read voltage parameter)によりメモリセルMCを読み出した結果にもとづく乱数パラメータ(PRESET)を生成する乱数制御回路162と、乱数パラメータ(PRESET)をシード値として用いて乱数(Random number)を発生させる擬似乱数生成回路161とを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】複数のメモリストリングのうち特定のメモリストリングに対して選択的に消去動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、メモリセルアレイ、複数のメモリストリング、ドレイン側選択トランジスタ、ソース側選択トランジスタ、複数のワード線、複数のビット線、ソース線、ドレイン側選択ゲート線、ソース側選択ゲート線、及び制御回路を有する。制御回路は、選択したビット線に第1電圧を印加して当該ビット線に接続されたメモリストリングに対し消去動作を実行する一方、非選択としたビット線に第2電圧を印加して当該ビット線に接続されたメモリストリングに対し消去動作を禁止する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 BiCSメモリのような積層型メモリの書き込み動作を高速化することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】 積層型のメモリセル構造を有する不揮発性半導体記憶装置であって、半導体基板上に、複数のメモリセルを積層してなるストリングを複数個配置したメモリセルアレイ11と、メモリセルアレイ11の任意のストリングをサンプルストリングとして選択し、該選択したサンプルストリングに対してデータの書き込みを行う回路12,14,16,30と、サンプルストリングの各メモリセルに対する書き込み回数をレイヤー毎に保持する書き込み回数記憶部31と、記憶部31に記憶されたレイヤー毎の書き込みパルス数を同一レイヤーの他のストリングのメモリセルの書き込み電圧の初期値に反映させる回路33とを備えている。

(もっと読む)

半導体装置、及び半導体装置の制御方法。

【課題】簡便な半導体装置の評価試験を実現する。

【解決手段】半導体装置10は、それぞれ内部信号MAを生成する第1及び第2のコアチップCC0,CC1を備え、第1及び第2のコアチップCC0,CC1のそれぞれに、貫通電極を介して他方のコアチップとスパイラル接続された第2及び第3のノードN2,N3を設け、この第2及び第3のノードN2,N3を介して、観測対象の内部信号MAを外部に出力することを技術思想とするものである。こうして出力される複数の内部信号MAを外部のテスター等によって観測することで、各コアチップの評価試験を並列に行える。

(もっと読む)

不揮発性メモリ装置

【課題】 パストランジスタ間の空間確保が可能な不揮発性メモリ装置を提供する

【解決手段】 不揮発性メモリ装置100が備える行デコーダ120は、パストランジスタ部123_L、123_Rを含む。パストランジスタ部123_L、123_Rは、メモリブロック110の左右に配列される。ブロック選択信号BLKWL1によって共通ゲートを形成するパストランジスタ端Pass TR 0とパストランジスタ端Pass TR 8とは、選択的に活性化される第1駆動信号ラインSI1及び第2駆動信号ラインSI2によって独立して駆動される。互に異なるブロック選択信号BLKWLによって駆動されるパストランジスタは、1つの活性領域の上に形成され得る。これにより、1つの活性領域の上に2つのパストランジスタを形成する場合、パストランジスタ部123_L、123_Rのチャンネル方向の大きさを減らすことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】高品質な半導体装置を提供する。

【解決手段】P型の半導体基板10と、半導体基板10内に形成されるNウェル11、半導体基板10内かつNウェル11上に形成されるPウェル12、及びPウェル12上に形成されるメモリセルトランジスタMTを含むCell領域と、半導体基板10内に形成されるNウェル14、及びNウェル上14に形成されるトランジスタHVP−Trを含むHVP−Tr領域と、半導体基板10上に形成されるトランジスタHVN―Trを含むHVN―Tr領域と、半導体基板10内に形成されるNウェル22、半導体基板10内かつNウェル22上に形成されるPウェル23、およびPウェル23上に形成されるトランジスタLVNE−Trを含むLVNE−Tr領域と、を具備し、Nウェル11及びNウェル22の底面の位置はNウェル14の底面の位置よりも低く、Nウェル14の底面の位置はPウェル12及びPウェル23の底面の位置よりも低い。

(もっと読む)

半導体装置

【課題】制御チップと複数の被制御チップが積層されたタイプの半導体装置において、コマンド信号よりも層アドレス信号を早く伝送させる。

【解決手段】互いに異なる層情報を保持する複数の被制御チップCC0〜CC7と、被制御チップCC0〜CC7に対して層アドレス信号A13〜A15及びコマンド信号ICMDを共通に供給する制御チップIFとを備える。層アドレス信号A13〜A15を構成する各ビットは、複数の第1の貫通電極のうち、被制御チップごとに並列接続された少なくとも2本の貫通電極を経由して伝送され、コマンド信号ICMDを構成する各ビットは、出力切り替え回路及び入力切り替え回路によって選択された対応する1本の貫通電極を経由して伝送される。これにより、コマンド信号ICMDよりも先に層アドレス信号A13〜A15が各被制御チップに到達する。

(もっと読む)

半導体装置

【課題】半導体装置を高集積化する。

【解決手段】本実施形態の半導体装置は、絶縁体内に設けられ、半導体集積回路を含んでいる半導体基板70と、絶縁体の開口部POPを介してその上面が露出するパッド90と、パッド90下方において半導体基板70のキャパシタ領域91内に設けられる複数のキャパシタ1と、を具備し、キャパシタ1は、所定の被覆率を満たすように、パッド90下方のキャパシタ領域91内に設けられ、キャパシタ1の2つの電極にそれぞれ接続されるコンタクト18A,18Gは、開口部POPと上下に重ならない位置に設けられている。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリブロック内で選択的に消去動作を実行することが可能な積層型の不揮発性半導体記憶装置を提供する。

【解決手段】メモリブロック中の少なくとも1つのサブブロックを選択的に消去する消去動作を実行する際、選択された第1のサブブロックにおいては、ビット線及びソース線に第1電圧を印加する一方、ワード線には第1電圧よりも小さい第2電圧を印加する。ドレイン側選択ゲート線、及びソース側選択ゲート線には、第1電圧よりも所定の値だけ低い第3電圧を印加する。非選択とされた第2のサブブロックにおいては、ドレイン側選択ゲート線、及びソース側選択ゲート線には、第1電圧と略同一の第4電圧を印加する。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】データの保持期間を長くする半導体装置又は半導体記憶装置を提供する。

【解決手段】一対の不純物領域を有する第1の半導体層152aと、第1の半導体層と同じ材料であり、第1の半導体層と離間する第2の半導体層152bと、第1、第2の半導体層の上に設けられた第1の絶縁層153と、第1の絶縁層153を介して第1の半導体層に重畳する第1の導電層154と、第1の絶縁層153を介して第1の導電層に重畳し、第1の半導体層と異なる材料である第3の半導体層156と、第1の導電層及び第3の半導体層に電気的に接続される第2の導電層157bと、第3の半導体層156に電気的に接続され、第2の導電層と同じ材料である第3の導電層157aと、第3の半導体層、第2の導電層、及び第3の導電層の上に設けられた第2の絶縁層158と、第2の絶縁層を介して第3の半導体層に重畳する第4の導電層159と、を含む。

(もっと読む)

1 - 20 / 208

[ Back to top ]