Fターム[5F101BE06]の内容

不揮発性半導体メモリ (42,765) | 周辺技術 (5,862) | 消去 (2,505)

Fターム[5F101BE06]の下位に属するFターム

Fターム[5F101BE06]に分類される特許

21 - 40 / 68

半導体装置

【課題】実施形態によれば、他の特性を損ねずにセル間の電荷の移動を抑制することができる半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、積層体と、第1の絶縁膜と、電荷蓄積膜と、第2の絶縁膜と、チャネルボディとを備えている。積層体は、基板上にそれぞれ交互に積層された複数の電極層と複数の絶縁層とを有する。第1の絶縁膜は積層体を貫通して形成されたホールの側壁に設けられている。電荷蓄積膜はホール内における第1の絶縁膜の内側に設けられている。電荷蓄積膜は、電極層に対向する部分で電極層に向かって突出し、他の部分よりも膜厚が厚い凸部を有する。第2の絶縁膜は電荷蓄積膜の内側に設けられている。チャネルボディは第2の絶縁膜の内側に設けられている。

(もっと読む)

半導体記憶装置及びその高電圧制御方法

【課題】チャージポンプ等の高電圧生成部の回路面積を削減する。

【解決手段】半導体記憶装置は、ワードライン及びビットラインが接続されマトリクス状に配置された複数のメモリセル21と、ワードラインを駆動する複数のワードラインドライバ23a及び23b、電源電圧を昇圧して高電圧を生成するチャージポンプ11と、複数のメモリセル21のうちアクセスに関係のある箇所には高電圧が印加され、アクセスに関係のない箇所には電源電圧が印加されるように制御するX方向高電圧制御回路31及びY方向高電圧制御回路32とを備える。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】トンネル領域を有する半導体不揮発性メモリにおいて、トンネル領域の周囲部分は掘り下げられており、掘り下げられたドレイン領域には、空乏化電極絶縁膜を介して、トンネル領域の一部を空乏化するための電位を自由に与えることが可能な空乏化電極を配置する。

(もっと読む)

半導体不揮発性メモリ装置

【課題】 占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】 ドレイン領域内のトンネル領域と微細穴に埋め込まれる形で形成されたフローティングゲート電極の側面との間にはトンネル絶縁膜を設け、微細穴に接するドレイン領域の表面付近には、電気的にフローティング状態である第1導電型のトンネル防止領域を設けた。

(もっと読む)

不揮発性メモリ装置及びその製造方法

【課題】不揮発性メモリ装置及びその製造方法を提供すること。

【解決手段】直列に接続した複数のメモリセルを含むメモリストリングと、前記メモリストリングの両端部にそれぞれ接続する第1及び第2選択トランジスタとを、含む不揮発性メモリ装置であって、前記メモリストリングが、第1半導体層145、及びメモリゲート絶縁膜を隔てて前記第1半導体層145と接する第2導電層125を含み、前記第1及び第2選択トランジスタが、それぞれ、前記第1半導体層145の一端及び他端と接続する第2及び第3半導体層165A、165Bを含み、前記第2導電層125が配置されない領域の前記第1半導体層145と接する第4半導体層165Cと、を含む。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】対向する二つの記憶素子のコントロールゲートのゲート長に起因する記憶素子の特性のばらつきを抑制する。

【解決手段】上記の課題を解決するために、不揮発性半導体記憶装置(1)を以下のように構成する。第1不揮発性メモリセル(1a)は、第1チャネル領域(11a)と、第1フローティングゲート(5a)と、第1コントロールゲート(6a)とを含むものとする。また、第2不揮発性メモリセル(1b)は、第2チャネル領域(11b)と、第2フローティングゲート(5b)と、第2コントロールゲート(6b)とを含むものとする。ここにおいて、第1チャネル領域(11a)は、第1フローティングゲート側チャネル領域(13a)と、第1コントロールゲート側チャネル領域(12a)とを備え、第1コントロールゲート側チャネル領域(12a)は不純物濃度が濃い高濃度ポケット領域(10)を備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】集積度を向上させた不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1積層構造体と、第1半導体層と、第1有機膜と、第1半導体側絶縁膜と、第1電極側絶縁膜と、を備えた不揮発性半導体記憶装置が提供される。前記第1積層構造体は、第1方向に沿って積層された複数の第1電極膜と、前記複数の第1電極膜どうしの間に設けられた第1電極間絶縁膜と、を有する。前記第1半導体層は、前記複数の第1電極膜の側面に対向する。前記第1有機膜は、前記複数の第1電極膜の前記側面と前記第1半導体層との間に設けられ有機化合物を含む。前記第1半導体側絶縁膜は、前記第1有機膜と前記第1半導体層との間に設けられる。前記第1電極側絶縁膜は、前記第1有機膜と前記複数の第1電極膜の前記側面との間に設けられる。

(もっと読む)

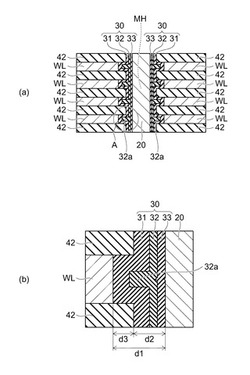

不揮発性半導体記憶装置

【課題】柱状のチャネル層となる半導体層に沿って、複数の浮遊ゲート型の不揮発性メモリセルが積層された構造の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、柱状の半導体膜131の側面にトンネル誘電体膜141、浮遊ゲート電極膜142、ゲート間絶縁膜143および制御ゲート電極膜144を備えるメモリセルMCが半導体膜131の延在方向に複数設けられるメモリセル列を、半導体基板101上に略垂直に複数配置した不揮発性半導体記憶装置が提供される。ここで、浮遊ゲート電極膜142と制御ゲート電極膜143は、柱状の半導体膜131の全周のうち特定の方向の側面にのみ形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリは、半導体基板1上に絶縁膜3を介して形成された制御ゲート電極CGと、半導体基板1上に電荷蓄積部を有する絶縁膜5を介して形成されたメモリゲート電極MGとを有しており、メモリゲート電極MGは、制御ゲート電極CGの側面22上に絶縁膜5を介してサイドウォールスペーサ状に形成されている。制御ゲート電極CGは、メモリゲート電極MGに絶縁膜5を介して隣接する側とは反対側の側面21の下部21aが突出し、また、メモリゲート電極MGに絶縁膜5を介して隣接する側の側面22の下部22aが後退している。メモリゲート電極MGは、制御ゲート電極CGに絶縁膜5を介して隣接する側の側面23の下部23aが突出している。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリセルと低電圧動作トランジスタや高電圧動作トランジスタを集積化し、異種トランジスタを混載する半導体装置の製造法を提供する。

【解決手段】半導体装置の製造方法は、(a)トンネル絶縁膜、Fゲート電極膜、電極間絶縁膜を堆積したFゲート電極構造を形成し(b)ゲート絶縁膜を形成し(c)導電膜、エッチストッパ膜を堆積し(d)エッチストッパ膜、導電膜をエッチングした積層ゲート電極構造を形成し(e)積層ゲート電極構造の側壁上に第1絶縁膜を形成し(f)積層ゲート電極側壁上に第1サイドウォールスペーサ層を形成し(g)エッチストッパ層を除去し(h)他の領域の導電層から、ゲート電極構造を形成し(i)積層ゲート電極構造、ゲート電極構造側壁上に第2サイドウォールスペーサを形成し(j)希弗酸水溶液で半導体基板表面を露出し(k)半導体基板表面にシリサイド層を形成する。

(もっと読む)

スイッチアレイ

【課題】 スイッチアレイの占有面積の縮小を図る。

【解決手段】本実施形態のスイッチアレイは、基板上に設けられる2つのスイッチと、第1の方向に延在する第1及び第2の制御線と、を具備し、スイッチのそれぞれは、メモリセルトランジスタが設けられる第1のアクティブ領域と、パストランジスタが設けられる第2のアクティブ領域と、を含み、アクティブ領域内でトランジスタのチャネル長方向に隣接するメモリセルトランジスタはソース又はドレインを共有し、第1及び第2のアクティブ領域は、トランジスタのチャネル幅方向に互いに隣接している。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去電圧を低減させることができる半導体記憶装置を提供することを課題とする。

【解決手段】チャネル形成領域を有する半導体膜と、半導体膜のチャネル形成領域上に、第1の絶縁層、浮遊ゲート電極、第2の絶縁層、制御ゲート電極を設ける。浮遊ゲート電極材料には、半導体基板よりも仕事関数があまり大きくならない窒化チタンとすることにより、消去電圧低減を図ったものである。なお、上記窒化チタンのチタン組成比は、低消費電力化及び誤書き換え耐性の観点から56atomic%以上75atomic%以下がよい。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルから確実にデータを読み出すことのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は、複数の不揮発性メモリセルに接続されるワード線と不揮発性メモリセルを選択してデータ読み出し動作を制御する制御回路とを備える。制御回路はデータ読み出し動作実行の際、選択メモリセルに接続された選択ワード線に、隣接する閾値電圧分布の中間電圧に第1の調整電圧を加えた電圧を印加し、選択ワード線に隣接する第1の非選択ワード線に、不揮発性メモリセルを導通させ得る読み出しパス電圧から第2の調整電圧を引いた電圧を印加し、第1の非選択ワード線に隣接する第2の非選択ワード線に、読み出しパス電圧に第2の調整電圧を加えた電圧を印加し、第1の非選択ワード線及び第2の非選択ワード線を除く非選択のワード線に、読み出しパス電圧を印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細化が進展しても読み出し動作時の電流を維持する。

【解決手段】複数のメモリサブブロックの各々は、第1ノードと第2ノードとの間に並列接続された複数のメモリトランジスタを含む。メモリサブブロックは、第1導電層と、第2導電層と、半導体層と、第3導電層とを備える。第1導電層は、層間絶縁膜を貫通して半導体基板に対し垂直な第1方向に延びるように形成され第1ノードとして機能する。第2導電層は、層間絶縁膜を貫通して半導体基板に対し第1方向に延びるように形成され第2ノードとして機能する。半導体層は、第1導電層と第2導電層とを接続するように半導体基板と平行な第2方向に延びるように形成されメモリトランジスタのチャネル層として機能する。第3導電層は、半導体層上にゲート絶縁膜を介して形成される。ゲート絶縁膜は、電荷蓄積膜を一部に含み第3導電層を囲う閉ループ状に形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】安定した動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、複数のセルユニットを有し且つ複数のセルユニットに保持されたデータを消去する消去動作実行の単位とされる複数のメモリブロックを備える。セルユニットは、メモリストリング、第1トランジスタ、第2トランジスタ、及びダイオードを備える。第1トランジスタは、メモリストリングの一端に一端を接続されている、第2トランジスタは、メモリストリングの他端と第2配線との間に設けられている。ダイオードは、第1トランジスタの他端と第1配線との間に設けられている。ダイオードは、基板に対して垂直方向に延びる第1導電型の第2半導体層と、第2半導体層の上面に接して基板に対して垂直方向に延びる第2導電型の第3半導体層とを備える。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置を構成する回路を高集積度化する。

【解決手段】一つの実施形態によれば、半導体記憶装置は、半導体基板と複数のメモリセルトランジスタを有する。前記複数のメモリセルトランジスタは、前記半導体基板に設けられた深溝にトレンチゲートが埋設され、直列接続される。メモリセルの書き込み動作及び読み出し動作のとき、トレンチゲートの周囲及び間の前記半導体基板の領域に、前記半導体基板とは逆導電型の反転層が形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】安定した動作を実行可能な不揮発性半導体記憶装置法を提供する。

【解決手段】制御回路は、消去動作時、選択セルユニットに接続された第1配線の電圧を、選択セルユニットに含まれる第1トランジスタのゲートの電圧よりも第1電圧だけ大きくする。制御回路は、消去動作時、非選択セルユニットに接続された第1配線の電圧と、非選択セルユニットに含まれる第1トランジスタのゲートの電圧との間の電圧差を第1電圧と異なる第2電圧とする。また、制御回路は、消去動作時、選択セルユニット及び非選択セルユニットにおいて、ダミーメモリストリング中の少なくとも1つのダミーメモリトランジスタのゲートに第3電圧を印加し、ダミーメモリストリング中の別のダミーメモリトランジスタのゲートに第3電圧よりも低い第4電圧を印加する。

(もっと読む)

半導体記憶装置

【課題】1つの実施形態は、例えば、電荷蓄積層内に蓄積された電荷の第2のゲート絶縁膜を介した制御ゲート電極へのリークを低減することを目的とする。

【解決手段】1つの実施形態によれば、半導体基板内で素子分離部により画定された素子領域と、素子領域を覆う第1のゲート絶縁膜と、第1のゲート絶縁膜を覆う電荷蓄積層と、半導体基板の素子領域が確定された面側を上とした場合において、電荷蓄積層の上面を覆う第1の部分と電荷蓄積層の側面を覆う第2の部分とを有する第2のゲート絶縁膜と、第2のゲート絶縁膜を介して電荷蓄積層の上面及び側面を覆う制御ゲート電極とを備え、第1の部分の耐圧は、前記第2の部分の耐圧より高い半導体記憶装置が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGとp型ウエルPW1との間および制御ゲート電極CGとメモリゲート電極MGとの間には、絶縁膜5が形成されている。この絶縁膜5のうち、メモリゲート電極MGの下面と半導体基板1の上面との間の部分は、酸化シリコン膜9a,9bと酸化シリコン膜9a,9bに挟まれた窒化シリコン膜10aとを有している。絶縁膜5のうち、制御ゲート電極CGの側面とメモリゲート電極MGの側面との間の部分は、酸化シリコン膜6aからなり、窒化シリコン膜10aを有していない。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】不揮発性半導体記憶装置の高信頼性及び高集積化を図る。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1乃至第iのメモリストリング(iは、2以上の自然数)を有し、第2の方向に延び、第3の方向に隣接する第1及び第2のフィン型積層構造9−1,9−2と、第1のフィン型積層構造9−1の第2の方向の一端に接続され、第3の方向の幅が第1のフィン型積層構造9−1のそれよりも広い第1の部分7aと、第2のフィン型積層構造9−2の第2の方向の一端に接続され、第3の方向の幅が第2のフィン型積層構造9−2のそれよりも広い第2の部分7bとを備える。第1乃至第iのメモリストリングは、それぞれ、複数のメモリセルとアシストゲートトランジスタとを備える。アシストゲートトランジスタのアシストゲート電極AG1,AG2は、電気的に独立である。

(もっと読む)

21 - 40 / 68

[ Back to top ]