Fターム[5F101BE07]の内容

不揮発性半導体メモリ (42,765) | 周辺技術 (5,862) | 消去 (2,505) | 電気消去消去回路 (2,403)

Fターム[5F101BE07]に分類される特許

21 - 40 / 2,403

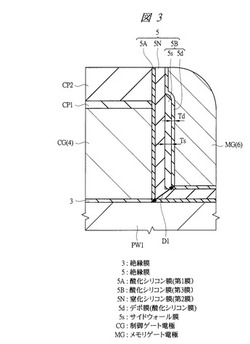

半導体装置および半導体装置の製造方法

【課題】半導体装置(不揮発性メモリを有する半導体装置)の特性を向上させる。

【解決手段】本発明の半導体装置は、制御ゲート電極CGと半導体基板との間に形成された絶縁膜3と、メモリゲート電極MGと半導体基板との間および制御ゲート電極CGとメモリゲート電極MGとの間に形成された絶縁膜5であって、その内部に電荷蓄積部を有する絶縁膜5と、を有する。この絶縁膜5は、第1膜5Aと、第1膜5A上に配置された電荷蓄積部となる第2膜5Nと、第2膜5N上に配置された第3膜5Bと、を有し、第3膜5Bは、制御ゲート電極CGとメモリゲート電極MGとの間に位置するサイドウォール膜5sと、メモリゲート電極MGと半導体基板との間に位置するデポ膜5dとを有する。かかる構成によれば、絶縁膜5の角部における距離D1を大きくすることができ、電界集中を緩和できる。

(もっと読む)

誘電体材料を含む個別要素又は半導体デバイスを含む集積回路デバイス

【課題】 本発明は、ドープされた金属酸化物誘電体材料を有する電子部品及びドープされた金属酸化物誘電体材料を有する電子部品の作製プロセスを提供する。

【解決手段】 ドープされた金属酸化物誘電体材料及びこの材料で作られた電子部品が明らかにされている。金属酸化物はIII族又はV族金属酸化物(たとえば、Al2O3、Y2O3、Ta2O5またはV2O5)で、金属ドーパントはIV族元素(Zr、Si、TiおよびHf)である。金属酸化物は約0.1重量パーセントないし約30重量パーセントのドーパントを含む。本発明のドープされた金属酸化物誘電体は、多くの異なる電子部品及びデバイス中で用いられる。たとえば、ドープされた金属酸化物誘電体は、MOSデバイスのゲート誘電体として用いられる。ドープされた金属酸化物誘電体はまた、フラッシュメモリデバイスのポリ間誘電体材料としても用いられる。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】酸素欠損の発生を抑制する。

【解決手段】ガリウム(Ga)若しくはスズ(Sn)の一部又は全部の代わりにゲルマニウム(Ge)を用いて酸化物半導体膜を構成する。ゲルマニウム(Ge)原子は、酸素(Ge)原子との結合の少なくとも一つの結合エネルギーがガリウム(Ga)又はスズ(Sn)の場合よりも高い。このため、ゲルマニウム(Ge)を用いて構成される酸化物半導体結晶において、酸素欠損が発生しにくい。このことから、ゲルマニウム(Ge)を用いて酸化物半導体膜を構成することにより、酸素欠損の発生の抑制を図る。

(もっと読む)

不揮発性メモリ装置の製造方法

【課題】不揮発性メモリ装置の製造方法を提供する。

【解決手段】基板10上に第1絶縁膜11及び第1導電膜12を形成するステップと、第1領域Cの第1導電膜12、第1絶縁膜11及び基板10をエッチングして、第1素子分離トレンチを形成するステップと、第1素子分離トレンチに埋め立てられる第1素子分離膜を形成するステップと、第2絶縁膜16及び導電性のキャップ膜17を形成するステップと、第2領域Pのキャップ膜17及び第2絶縁膜16をエッチングするステップと、第2導電膜19を形成するステップと、第1領域Cの第2導電膜19、キャップ膜17、第2絶縁膜16、第1導電膜12及び第1絶縁膜11を選択的にエッチングして、第1ゲートパターンを形成しながら、第2領域Pの第2導電膜19、第1導電膜12、第1絶縁膜11及び基板10を選択的にエッチングして、第2領域Pに第2素子分離トレンチT2、T3を形成するステップとを含む。

(もっと読む)

半導体装置の製造方法

【課題】素子分離用の大きなエアギャップを容易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】一の実施形態による半導体装置の製造方法では、基板内に素子分離溝を形成し、前記素子分離溝の側壁面にアモルファス層を形成する。さらに、前記方法では、前記素子分離溝内に前記アモルファス層を介して犠牲膜を形成し、前記犠牲膜上にエアギャップ膜を形成する。さらに、前記方法では、前記エアギャップ膜の形成後に前記犠牲膜を除去することで、前記エアギャップ膜の下部の前記素子分離溝内にエアギャップを形成する。

(もっと読む)

不揮発性メモリ装置、不揮発性メモリ装置のプログラム方法、不揮発性メモリ装置を含むメモリシステム

【課題】向上された信頼性を有する不揮発性メモリ装置のプログラム方法が提供される。

【解決手段】本発明のプログラム方法は、第1メモリセルトランジスターの閾値電圧がプログラム状態から移動する傾向を判別する段階と、判別結果に応答して、複数の検証電圧の中で第1検証電圧を選択する段階と、第1メモリセルトランジスターの閾値電圧が変化するように第1メモリセルトランジスターをプログラムする段階と、で構成される。プログラムする段階は第1メモリセルトランジスターの閾値電圧が十分に変化されたかを第1検証電圧を利用して検証する段階を含む。判別する段階は第1メモリセルトランジスターの閾値電圧の第1範囲からの変化を判別する段階を含む。

(もっと読む)

論理回路

【課題】安定した高速動作を実現しつつ、製造工程も簡素化することが可能な論理回路を提供すること。

【解決手段】この論理回路1は、バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2のFET2A,2Bを備える論理回路であって、第1及び第2のFET2A,2BのうちのFET2Aは、ゲート端子が接続されるゲート電極膜17と、半導体材料からなるチャネル層12と、ゲート電極膜17とチャネル層12との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層16と、を有する。

(もっと読む)

窒化シリコン膜の成膜方法、不揮発性記憶装置の製造方法

【課題】面内方向での膜厚の均一性に優れ、電荷保持特性に優れた窒化シリコン膜の成膜方法、及び窒化シリコン膜を備えた不揮発性記憶装置の製造方法を提供する。

【解決手段】半導体基板上に第2の窒化シリコン膜を形成する工程と、第2の窒化シリコン膜上に第2の窒化シリコン膜よりも光学吸収係数が大きくかつ光学吸収係数kが0.60〜1.26の第1の窒化シリコン膜を、ステップ成膜法により形成する工程と、を有する窒化シリコン膜の成膜方法。

(もっと読む)

不揮発性半導体記憶装置

【課題】読出動作の精度を向上させた不揮発性半導体記憶装置を提供する。

【解決手段】メモリストリングは、半導体基板の上方に設けられ、複数のメモリセルを含む。制御回路は、複数のメモリセルのうち、選択メモリセルに保持されたデータを読み出す読出動作を実行する。メモリストリングは、半導体層、電荷蓄積層、及び導電層を有する。半導体層は、半導体基板に対して垂直方向に延びメモリセルのボディとして機能する。電荷蓄積層は、半導体層の側面に設けられ、電荷を蓄積可能とされる。導電層は、半導体層と共に電荷蓄積層を挟むよう設けられメモリセルのゲートとして機能する。制御回路は、読出動作の実行前に、選択メモリセル及び非選択メモリセルを導通状態としてメモリストリングの一端から他端へと電流を流すリフレッシュ動作を実行する。

(もっと読む)

半導体装置

【課題】良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供する。また、信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極層をマスクとした不純物の導入処理によって自己整合的にチャネル形成領域と一対の低抵抗領域とが形成される酸化物半導体層を有し、ゲート電極層を挟んで設けられる一対の配線層が低抵抗領域と電気的に接続し、配線層が形成される領域の下部に低抵抗領域と接する電極層が設けられている半導体装置である。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】熱工程による負担を減らし、メモリセル特性の向上を図る。

【解決手段】本実施形態による不揮発性半導体記憶装置の製造方法よれば、基板上30に、コントロールゲートCGとなる導電膜を形成する。前記導電膜の上面から下面まで貫通するホール40を形成する。前記ホールの内面上に、ブロック絶縁膜150を形成する。前記ブロック絶縁膜上に、電荷蓄積膜151を形成する。前記電荷蓄積膜上に、トンネル絶縁膜152を形成する。前記トンネル絶縁膜上に、半導体層SPを形成する。前記半導体層上に、前記ホールが埋め込まれないように酸素乖離の触媒作用を有する材料を含む膜153を形成する。前記ホールの内側から前記膜を介して、前記トンネル絶縁膜と前記半導体層との界面を酸化する。

(もっと読む)

3Dフラッシュ構造用のエッチングプロセス

【課題】プラズマ処理室において、ウェハ上でスタックを形成するシリコン系の複数の二重層の中に高アスペクト比のフィーチャをエッチングするための方法を提供する。

【解決手段】プラズマ処理室に主エッチングガスが流入される。第1の圧力を提供しながら、主エッチングガスがプラズマにされる。20℃未満のウェハ温度が維持される。プラズマにより上記複数のシリコン系二重層のうちの複数の組を貫いてエッチングする間に、第1の圧力よりも低い第2の圧力まで圧力を降下させる。上記複数の二重層のうち第1の複数の組がエッチングされた後に、主エッチングガスの流入を停止させる。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

半導体装置の製造方法

【課題】

実施形態は、ゲート配線の抵抗が増大することを防止可能な半導体装置の製造方法を提供する。

【解決手段】

本実施形態の半導体装置の製造方法は、第1領域及び第2領域の半導体素子を形成するために、半導体基板、前記半導体基板上の第1絶縁膜、前記第1絶縁膜上の電荷蓄積層を積層し、所望のトレンチを形成する工程と、前記トレンチに素子分離膜を形成する工程と、前記素子分離膜及び前記電荷蓄積層上にストッパー膜30を形成する工程と、前記第2領域を第2絶縁膜で被膜し、前記第1領域の前記ストッパー膜30と前記素子分離膜をエッチバックする工程と、前記エッチバックされた素子分離膜、前記電荷蓄積層、第2領域の前記ストッパー膜30上に第3絶縁膜を介して配線を形成する工程とを備えることを特徴とする。

(もっと読む)

半導体装置

【課題】MONOS型不揮発性メモリの信頼性を向上させる。

【解決手段】メモリセルは、選択ゲート6とその一方の側面に配置されたメモリゲート8とを有している。メモリゲート8は、一部が選択ゲート6の一方の側面に形成され、他部がメモリゲート8の下部に形成されたONO膜7を介して選択ゲート6およびp型ウエル2と電気的に分離されている。選択ゲート6の側面にはサイドウォール状の酸化シリコン膜12が形成されており、メモリゲートの側面にはサイドウォール状の酸化シリコン膜9と酸化シリコン膜12とが形成されている。メモリゲート8の下部に形成されたONO膜7は、酸化シリコン膜9の下部で終端し、酸化シリコン膜12の堆積時にメモリゲート8の端部近傍の酸化シリコン膜12中に低破壊耐圧領域が生じるのを防いでいる。

(もっと読む)

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

メモリ装置

【課題】配線電極間の双方向の電流値、書き込み及び消去の電圧値、および記憶保持時間が制御容易なメモリ装置を提供する。

【解決手段】微結晶である第1の導電性微粒子を含む微結晶層22と、微結晶層22を挟むトンネル絶縁膜21、23とを有する第1の二重トンネル接合構造と、微結晶である第2の導電性微粒子を含む微結晶層26と、微結晶層26を挟むトンネル絶縁膜25、27とを有する第2の二重トンネル接合構造と、第1の二重トンネル接合構造と第2の二重トンネル接合構造との間に配置され、情報電荷を蓄積する電荷蓄積層と、第1の二重トンネル接合構造、電荷蓄積層、及び第2の二重トンネル接合構造を挟む第1、第2の導電層とを備える。第1の導電性微粒子の平均粒径は、第2の導電性微粒子の平均粒径と異なっている。

(もっと読む)

酸化膜の形成方法

【課題】シリコン表面のプラズマ酸化により、界面準位密度が低くリーク電流の少ない高品質な酸化膜をシリコン表面上に形成する。

【解決手段】

酸化膜の形成方法は、KrとO2の混合ガス中にプラズマを形成することにより原子状酸素O*を発生させ、前記原子状酸素O*によりシリコン表面をプラズマ酸化するプラズマ酸化工程を含み、前記プラズマ酸化工程は、800〜1200mTorrの圧力範囲において実行される。

(もっと読む)

21 - 40 / 2,403

[ Back to top ]