Fターム[5F101BE07]の内容

不揮発性半導体メモリ (42,765) | 周辺技術 (5,862) | 消去 (2,505) | 電気消去消去回路 (2,403)

Fターム[5F101BE07]に分類される特許

121 - 140 / 2,403

信号処理回路

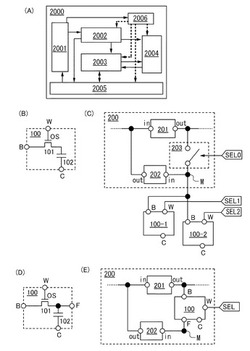

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】演算部と、メモリと、演算部及びメモリを制御する制御部と、を有し、制御部は、揮発性の記憶回路と揮発性の記憶回路に保持されたデータを記憶するための第1の不揮発性の記憶回路との組を複数有し、メモリは、第2の不揮発性の記憶回路を複数有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する。

(もっと読む)

半導体装置

【課題】瞬断もしくは瞬時電圧低下等の極めて短時間の電源停止又は電源電圧低下の場合でさえ、揮発性メモリ内のデータが消失してしまう場合があった。そこで、高速データ処理のために揮発性メモリを用いた場合であっても、データの保持時間を延ばす。

【解決手段】容量素子及び酸化物半導体を用いたトランジスタを有するメモリに揮発性メモリのデータ内容をバックアップしておくことによって、データの保持時間を長くすることができる。

(もっと読む)

記憶装置

【課題】リフレッシュ動作の回数を減らすことで、消費電力を抑える。また、先に書き込んだデータを破壊することなく、データを読み出す。

【解決手段】ソースまたはドレインの一方となる第1の電極と、ソースまたはドレインの他方となる第2の電極と、第1のチャネル形成領域に絶縁膜を介して重畳して設けられた第1のゲート電極と、を有する第1のトランジスタと、ソースまたはドレインの一方となる第3の電極と、ソースまたはドレインの他方となる第4の電極と、第2のチャネル形成領域が第2のゲート電極と第3のゲート電極との間に絶縁膜を介して設けられた第2のトランジスタと、を有するメモリセルを複数有し、第1のチャネル形成領域及び第2のチャネル形成領域は、酸化物半導体を含んでおり、第2の電極は、第2のゲート電極に直接接続されている記憶装置とする。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

記憶装置、及び当該記憶装置を用いた半導体装置

【課題】DRAMよりも書き込み、読み出しなどの動作速度が高く、SRAMよりもメモリセルあたりの半導体素子の数を減らすことができる記憶装置。

【解決手段】制御装置と、演算装置と、緩衝記憶装置とを有し、緩衝記憶装置は、主記憶装置から、或いは演算装置から送られてきたデータを、制御装置からの命令に従って記憶し、緩衝記憶装置は複数のメモリセルを有し、メモリセルは、チャネル形成領域に酸化物半導体を含むトランジスタと、トランジスタを介してデータの値に従った量の電荷が供給される記憶素子とを有する。さらに、緩衝記憶装置が有する複数のメモリセルは、バリッドビットに対応するメモリセルが、データフィールドに対応するメモリセルよりも、そのデータの保持時間が短い。

(もっと読む)

半導体記憶装置

【課題】電荷蓄積層及び制御ゲートを有する半導体記憶装置のバックバイアス効果による影響を低減させることにより集積度を向上させ、占有面積を増加させずに浮遊ゲートと制御ゲートとの容量の比をより一層増大させるとともに、製造プロセスに起因するセル特性のばらつきが抑制された半導体記憶装置を提供する。

【解決手段】半導体基板と、少なくとも1つの島状半導体層110、該島状半導体層110の側壁の周囲の全部又は一部に形成された電荷蓄積層513及び制御ゲート523から構成される少なくとも1つのメモリセルとを有する半導体記憶装置であって、前記メモリセルの島状半導体層110が不純物拡散層により前記半導体基板から電気的に絶縁されてなる。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の低抵抗化を図る。

【解決手段】本実施形態の半導体装置は、半導体基板10を覆う第1の層間絶縁膜上に設けられる配線60と、配線60の上面上に設けられるキャップ層68と、配線60と第2の層間絶縁膜との間に設けられるバリア膜62と、を含む。配線60は高融点導電層を含み、配線60の配線幅W1は、キャップ層68の幅W2よりも小さい。バリア膜62は、高融点導電層60が含む元素の化合物からなり、配線60を覆う層間絶縁膜69,70に起因する不純物が配線60内に拡散するのを抑制する。

(もっと読む)

半導体装置の駆動方法

【課題】半導体装置の駆動方法を提供する。

【解決手段】ビット線と、選択線と、選択トランジスタと、m(mは2以上の自然数)本の書き込みワード線と、m本の読み出しワード線と、ソース線と、第1乃至mのメモリセルと、を有する半導体装置において、メモリセルは、第1のトランジスタ、容量素子に蓄積された電荷を保持する第2のトランジスタを含み、第2のトランジスタは酸化物半導体層で形成されるチャネルを有する。上記構成の半導体装置の駆動方法において、メモリセルに書き込みを行う場合、第1のトランジスタを導通させて第1のソース端子または第1のドレイン端子を固定電位とし、容量素子に安定した電位の書き込みを行う。

(もっと読む)

半導体記憶装置

【課題】高性能な乱数を生成することができ、予測困難性を向上できる半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、複数のメモリセルMCが配置されるメモリセルアレイ11と、乱数(Random number)を発生させる乱数発生回路16と、メモリセルアレイ11および乱数発生回路16を制御するコントローラ19とを少なくとも具備する。乱数発生回路16は、生成した制御パラメータ(Read voltage parameter)によりメモリセルMCを読み出した結果にもとづく乱数パラメータ(PRESET)を生成する乱数制御回路162と、乱数パラメータ(PRESET)をシード値として用いて乱数(Random number)を発生させる擬似乱数生成回路161とを備える。

(もっと読む)

半導体集積回路

【課題】電荷転送効率が高い転送トランジスタを備える半導体集積回路を提供することを目的とする。

【解決手段】実施形態に係る半導体集積回路は、ゲート電極を有し、当該ゲート電極及び一の拡散層が第1配線でダイオード接続された転送トランジスタと、クロック信号が供給されるクロック信号線とを備え、前記クロック信号線の一部である第1部分クロック信号線の少なくとも一部が前記ゲート電極上に形成されていることを特徴とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】複数のメモリストリングのうち特定のメモリストリングに対して選択的に消去動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、メモリセルアレイ、複数のメモリストリング、ドレイン側選択トランジスタ、ソース側選択トランジスタ、複数のワード線、複数のビット線、ソース線、ドレイン側選択ゲート線、ソース側選択ゲート線、及び制御回路を有する。制御回路は、選択したビット線に第1電圧を印加して当該ビット線に接続されたメモリストリングに対し消去動作を実行する一方、非選択としたビット線に第2電圧を印加して当該ビット線に接続されたメモリストリングに対し消去動作を禁止する。

(もっと読む)

不揮発性メモリ装置及びその製造方法

【課題】半導体基板のセル領域と周辺回路領域との間に段差をなくして、工程を容易かつ単純にしつつ、特に、コンタクトナットオープン(Contact not open)、下部構造物に対するアタック(Attack)などを防止し、工程歩留まり及び信頼性を向上させることができる不揮発性メモリ装置及びその製造方法を提供すること。

【解決手段】周辺回路領域及び該周辺回路領域より高さが低いセル領域を有する半導体基板と、該半導体基板の前記セル領域上に配置され、複数の層間絶縁膜及び複数の制御ゲート電極が交互に積層された制御ゲート構造物と、該制御ゲート構造物が形成された前記半導体基板の前記セル領域を覆う第1の絶縁膜と、該第1の絶縁膜上の選択ゲート電極と、前記半導体基板の前記周辺回路領域上の周辺回路素子とを備えることを特徴とする。

(もっと読む)

選択トランジスタ、選択トランジスタの作成方法、メモリ装置及びメモリ装置の製造方法

【課題】少ない工程数で製造でき、フラットバンド電圧のシフトを抑制できる選択トランジスタ、選択トランジスタの作成方法、メモリ装置及びメモリ装置の製造方法を提供すること。

【解決手段】直列接続された複数のメモリトランジスタを備えたメモリ装置で用いられる選択トランジスタであって、半導体基板上に形成されたトンネル絶縁層と、トンネル絶縁層上に形成された電荷蓄積層と、電荷蓄積層上に形成され、アルゴンをソースガスとするガスクラスタイオンビームが照射されたブロッキング絶縁層と、ブロッキング絶縁層上に形成されたゲート電極と、ゲート電極の両側の半導体基板中に形成されたソース/ドレイン領域と、を具備する。

(もっと読む)

二重ゲート電極構造を含む半導体装置及びその製造方法

【課題】漏洩電流発生を最小化すると同時にオン電流(On current)を増加させ得る二重ゲート電極構造を含む半導体装置及びその製造方法が提供される。

【解決手段】本発明による半導体装置は、基板に配置されるゲート電極と、前記ゲート電極の両端に各々隣接するように前記基板に配置される第1不純物注入領域及び第2不純物注入領域と、前記第1不純物注入領域と前記第2不純物注入領域との間に配置されるチャンネル領域を含み、前記ゲート電極は前記第1不純物注入領域に隣接する第1サブゲート電極と前記第2不純物注入領域に隣接する第2サブゲート電極と、を含み、前記第1サブゲート電極と前記第2サブゲート電極とは前記チャンネル領域の上に配置される。この半導体装置では1つのチャンネル領域が2つのサブゲートによって独立的に制御されて漏洩電流発生を最小化できる。

(もっと読む)

半導体装置およびその製造方法

【課題】FMONOSメモリセルとCMOSトランジスタが共存する半導体装置において、トランジスタの駆動電流を高めるとともにFMONOSメモリセルとしての機能を確保する半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、主表面上に形成された、チャネルを有するMONOS型メモリセルと、主表面上に形成されたnチャネル型トランジスタと、主表面上に形成されたpチャネル型トランジスタとを備える半導体装置である。上記MONOS型メモリセル、nチャネル型トランジスタおよびpチャネル型トランジスタの上面に接するように窒化膜CS1、CS2が形成されている。上記窒化膜CS1、CS2はMONOS型メモリセル、nチャネル型トランジスタおよびpチャネル型トランジスタのチャネルに応力を付加する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の電気的性能および信頼性を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGは、金属膜6aと金属膜6a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極であり、金属膜6aの上端部には、金属膜6aの一部が酸化することで金属酸化物部分17が形成されている。スプリットゲート型の不揮発性メモリの制御ゲート電極は、金属膜4aと金属膜4a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極である。

(もっと読む)

バイト、ページおよびブロックに書き込むことができ、セルアレイ中で干渉を受けず分割が良好な特性を備え、新規のデコーダ設計とレイアウトの整合ユニットと技術を使用する単体式複合型不揮発メモリ

【課題】

バイト、ページおよびブロックで書き込むことができる新単体式複合型不揮発メモリを提供する。

【解決手段】

不揮発メモリアレイは、シングルトランジスタフラッシュメモリセルおよびダブルトランジスタEEPROMメモリセルを備え、同じ基板上に整合することができ、該不揮発メモリセルは低いカップリング係数の浮遊ゲートを備えて、メモリセル体積を減少でき、該浮遊ゲートをトンネル絶縁層の上に配置し、該浮遊ゲートは該ソース領域の辺縁および該ドレイン領域の辺縁に揃って、且つ該ソース領域辺縁および該ドレイン領域辺縁の幅に画定される幅を備え、該浮遊ゲートと該制御ゲートは50%より小さい相対的に小さなカップリング係数を備えて、該不揮発メモリセルを縮小できるようにし、該不揮発メモリセルのプログラムはチャネル熱電子方式で達成し、消去は高電圧でFNトンネル方式で達成する。

(もっと読む)

多層接続構造及びその製造方法

【課題】3次元積層ICデバイスにおいて、相互接続領域のコンタクトレベルのスタックへの電気接続形成工程を簡略化する製造方法を提供する。

【解決手段】各コンタクトレベルは導電層と絶縁層とを有する。コンタクト開口を作り出すために、第1のコンタクトレベルを露出させるように上部層の一部が除去される。N個のマスクを用いて、最大2N個のコンタクトレベルまでコンタクト開口がエッチングされる。各マスクは、コンタクト開口のうちの実効的に半数をエッチングするために使用される。Nが3であるとき、第1のマスクにより1つのコンタクトレベルがエッチングされ、第2のマスクにより2つのコンタクトレベルがエッチングされ、第3のマスクにより4つのコンタクトレベルがエッチングされる。コンタクト開口の側壁に誘電体層が形成され得る。コンタクト開口内に導電体が形成され、前記誘電体層が該導電体を前記側壁から電気的に絶縁する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】選択ゲート電極が浮遊ゲート電極の横に位置している不揮発型記憶素子において、浮遊ゲート電極と半導体基板の間の容量に対する、制御ゲート電極と浮遊ゲート電極の間の容量の比を大きくする。

【解決手段】平面視において、制御ゲート電極130のうち選択ゲート電極170側の端部は、浮遊ゲート電極120の外側に位置した拡張部133となっている。拡張部133の下端は、浮遊ゲート電極120の上面よりも半導体基板100の近くに位置している。また拡張部133と浮遊ゲート電極120の間にも第1絶縁膜132が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリおよび容量素子を有する半導体装置の性能を向上させる。

【解決手段】同一の半導体基板1上に、不揮発性メモリのメモリセルMCと容量素子とが形成されている。メモリセルMCは、半導体基板の上部に絶縁膜3を介して形成された制御ゲート電極CGと、半導体基板1の上部に形成されて制御ゲート電極CGと隣合うメモリゲート電極MGと、メモリゲート電極MGと半導体基板1との間および制御ゲート電極CGとメモリゲート電極MGとの間に形成されて内部に電荷蓄積部を有する絶縁膜5とを有している。容量素子は、制御ゲート電極CGと同層のシリコン膜で形成された下部電極と、絶縁膜5と同層の絶縁膜で形成された容量絶縁膜と、メモリゲート電極MGと同層のシリコン膜で形成された上部電極とを有している。そして、上部電極の不純物濃度は、メモリゲート電極MGの不純物濃度よりも高くなっている。

(もっと読む)

121 - 140 / 2,403

[ Back to top ]