Fターム[5F101BE07]の内容

不揮発性半導体メモリ (42,765) | 周辺技術 (5,862) | 消去 (2,505) | 電気消去消去回路 (2,403)

Fターム[5F101BE07]に分類される特許

101 - 120 / 2,403

半導体装置及びその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタ及びその作製方法を提供する。または、該トランジスタを含む信頼性の高い半導体装置及びその作製方法を提供する。

【解決手段】チャネル形成領域と、該チャネル形成領域を挟むように設けられ、チャネル形成領域よりも低抵抗な領域であるソース領域及びドレイン領域と、を含み、チャネル形成領域、ソース領域及びドレイン領域はそれぞれ結晶性領域を含む酸化物半導体層を有する半導体装置を提供する。

(もっと読む)

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼でき、非常に小型の3次元集積回路メモリ用の構造を低い製造コストで提供する。

【解決手段】3次元アレイは第1の端部と第2の端部を含む2つの端部を有し、第1の端部と第2の端部の一方はビット線BLに接続され、第1の端部と第2の端部の他方はソース線CSLに接続される不揮発性メモリセルのNANDストリングのスタック1412、1413、1414と、ビット線BL及びソース線SLの一方をメモリセルのストリング1412、1413、1414に接続させるダイオード1492を有する。

(もっと読む)

半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供する

ことを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウ

ム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて

、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化

物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以

下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有

し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でス

パッタリングを行う。

(もっと読む)

半導体装置

【課題】消去特性と消去ディスターブ特性との双方を向上することが可能な、MONOS型メモリセルなどの半導体装置を提供する。

【解決手段】半導体基板SUBの主表面に形成される第1のゲート電極CGと、主表面上において第1のゲート電極CGと隣接するように形成された第2のゲート電極MGと、第2のゲート電極MGと半導体基板SUBとに挟まれた領域から、第1のゲート電極CGと第2のゲート電極MGとに挟まれた領域に連なるように延びる絶縁膜ONOと、第1および第2のゲート電極CG,MGの真下のチャネル領域を挟むように、主表面に形成される1対のソース/ドレイン領域NR1,NR2とを備える。上記ソース領域NR1は、第1のソース領域N11および第2のソース領域N12を含んでいる。上記第2のソース領域N12は第1のソース領域N11よりも主表面から深い領域に形成されている。上記第1のソース領域N11と第2のソース領域N12とに含まれる不純物の材質が異なっている。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

アプリケーション回路及び半導体デバイスの動作方法

【課題】バッテリレス電子タイマに適用される半導体デバイス、及びその動作方法とアプリケーション回路を提供する。

【解決手段】半導体デバイス600は、第1導電型半導体基板と、ゲート誘電層と、フローティングゲート606と、第2導電型ウェル608と、第1導電型ウェル610と、第2導電型ソース拡散層612と、第2導電型ドレイン拡散層614と、第2導電型制御ゲート拡散層616と、を含む。制御ゲート拡散層616、ソース拡散層612及びドレイン614の間の漏れ電流が二重のウェル領域上に印加されるバイアスを調節することにより減少される。

(もっと読む)

記憶装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な記憶装置、及び該記憶装置を有する半導体装置を提供する。

【解決手段】第1の入力端子、及び第1の入力端子の入力信号の反転信号が入力される第2の入力端子、並びに第1の信号が出力される第1の出力端子、及び第1の信号の反転信号が出力される第2の出力端子、を有するレベルシフタと、第1の信号が入力される第3の入力端子、及び第1の信号の反転信号が入力される第4の入力端子、並びに第3の出力端子を有する第1のバッファと、第1の信号の反転信号が入力される第5の入力端子、及び第1の信号が入力される第6の入力端子、並びに第4の出力端子を有する第2のバッファと、を有し、第1のバッファの第3の出力端子から出力される信号が、レベルシフタの第1の入力端子に入力され、第2のバッファの第4の出力端子から出力される信号が、レベルシフタの第2の入力端子に入力される。

(もっと読む)

半導体装置の製造方法

【目的】幅寸法が異なるワード線に対する書き込み電圧の設定の適正化を図ることが可能な半導体装置の製造方法を提供することを目的とする。

【構成】実施形態の半導体装置の製造方法は、線幅の異なる複数のワード線の組が繰り返し配置された半導体記憶装置における全ページのそれぞれの書き込み電圧を取得する工程と、すべての組における前記複数のワード線のうちの第1のワード線に対応するページの書き込み電圧の第1の平均値を演算する工程と、すべての組における前記複数のワード線のうちの、前記第1のワード線と隣り合う第2のワード線に対応するページの書き込み電圧の第2の平均値を演算する工程と、各組の第1のワード線に対応するページに対する書き込み電圧を前記第1の平均値に設定し、各組の第2のワード線に対応するページに対する書き込み電圧を前記第2の平均値に設定する工程と、を備えた。

(もっと読む)

固集積フラッシュメモリーセルストリング、セル素子、及びこの製造方法

【課題】優れた縮小化特性を有し、閾値電圧の散布を減らすことができるフラッシュメモリーセルストリング及びこの製造方法を提供する。

【解決手段】本発明は、フラッシュメモリーセルストリング及びこの製造方法に関する。前記フラッシュメモリーセルストリングは、多数のセル素子及び前記セル素子の端部に連結されるスイッチング素子を含む。前記セル素子は、半導体基板と、半導体基板に順次に積層される透過絶縁膜と、電荷貯蔵ノードと、コントロール絶縁膜と、制御電極とを備え、ソース/ドレーンが形成されないことを特徴とする。前記スイッチング素子は、セル素子に連結される側にソースまたはドレーンを含まないし、セル素子に連結されない側にソースまたはドレーンを含むが制御電極と重なり、又はまたは重ならないことを特徴とする。

(もっと読む)

半導体装置の駆動方法

【課題】半導体装置の駆動方法を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のトランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電位を保持させることで行う。メモリセルの読み出しは、ビット線にプリチャージ電位を供給した後ビット線への電位の供給を止め、ビット線の電位がプリチャージ電位に保たれるか、または電位が下がるか、により行う。

(もっと読む)

半導体記憶装置

【課題】データの読み出し速度を向上する。

【解決手段】半導体記憶装置1は、メモリセルアレー1aと、コラム線1bと、第1および第2のデータ線1d,1eと、データの読み出し時には、コラム線1bに第1および第2のデータ線1d,1eの一方を選択して接続し、データの書き込み時には、コラム線1bに第1および第2のデータ線1d,1eを接続するスイッチ1cと、第1および第2のデータ線1d,1eに接続された読み出し回路1fと、第1および第2のデータ線1d,1eに接続された書き込み回路1gと、を有する。

(もっと読む)

記憶回路

【課題】短時間の電源停止により消費電力を抑えることができ、電源再開時において誤動作を引き起こすことなく初期化することのできる信号処理装置の記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性記憶部に記憶していたデータ信号を、不揮発性記憶部に保持する。不揮発性記憶部では、オフ電流が極めて小さいトランジスタを用いることによって、容量素子に保持されたデータ信号は長期間にわたり保持する。こうして、不揮発性記憶部は電源の供給が停止した間も論理状態を保持する。また電源停止時に容量素子で保持されたデータ信号は、電源再開時にはリセット回路を導通状態とすることで、誤動作を引き起こすことのない電位にする。

(もっと読む)

半導体装置およびその製造方法

【課題】選択用トランジスタのゲート電極と記憶用トランジスタのゲート電極との間の耐圧を確保し、かつ閾値電圧の変動が抑制されたMONOS型メモリセルを提供する。

【解決手段】主表面SBSを有する半導体基板SUBと、主表面SBS上に形成された第1のゲート電極CGと、主表面SBS上において第1のゲート電極CGと隣接するように形成された第2のゲート電極MGと、第2のゲート電極MGと半導体基板SUBとに挟まれた領域から、第1のゲート電極CGと第2のゲート電極MGとに挟まれた領域に連なるように延びる第1の絶縁膜ONOとを備える半導体装置である。上記第2のゲート電極MGの最上面MGSは第1のゲート電極CGの最上面CGSより低くなっている。上記第2のゲート電極MGの最上面MGSは主表面SBSに沿うように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性半導体装置の高集積化を図ることのできる技術を提供する。

【解決手段】スイッチ用nMIS(Qs)のスイッチゲート電極SGと、スイッチ用nMIS(Qs)にワード線に対して交差する方向に沿って隣接するメモリ用nMIS(Qm)のメモリゲート電極MGとの間に、スイッチ用nMIS(Qs)のソース/ドレイン領域SDHとして機能し、同時にメモリ用nMIS(Qm)のドレイン領域Dとして機能する半導体領域を形成し、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)側のソース/ドレイン領域SDHを構成する半導体領域の形状と、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)と反対側(ビット線側)のソース/ドレイン領域SDLを構成する半導体領域の形状とを非対称とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】消去動作の実行単位を小さくすると共に正確な読出動作を実現可能な不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、複数のメモリストリング、複数のメモリブロック、複数のソース線、及び制御回路を有する。複数のメモリストリングは、積層された複数のメモリトランジスタを含む。複数のメモリブロックは、複数のメモリストリングを含む。複数のソース線は、複数のメモリストリングそれぞれに接続される。制御回路は、複数のソース線に供給する信号を制御する。複数のメモリストリングは、各々、半導体層、電荷蓄積層、及び導電層を有する。制御回路は、メモリトランジスタに対する動作の種類に基づいて、複数のソース線を電気的に共通接続するか否かを切り替える。

(もっと読む)

不揮発性半導体記憶装置

【課題】誤書込みを抑制した不揮発性半導体記憶装置を提供する。

【解決手段】制御回路は、書込み動作時、複数のビット線中の書込み禁止ビット線の電圧を第1電圧まで上げた後、書込み禁止ビット線をフローティング状態とする。続いて、制御回路は、書込み禁止ビット線以外の書込みビット線の電圧を第2電圧まで上げ、これに伴うカップリングにより書込み禁止ビット線の電圧を上げる。これにより、制御回路は、書込み禁止ビット線に対応するメモリストリング内のメモリトランジスタに対して書込み動作を禁止する。一方、制御回路は、書込みビット線に対応するメモリストリング内のメモリトランジスタに対して書込み動作を実行する。

(もっと読む)

半導体記憶装置

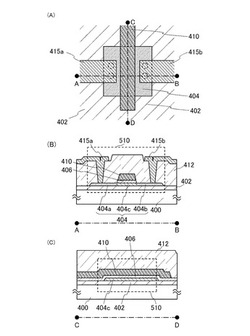

【課題】電荷蓄積層及び制御ゲートを有する半導体記憶装置のバックバイアス効果による影響を低減させることにより集積度を向上させ、占有面積を増加させずに浮遊ゲートと制御ゲートとの容量の比をより一層増大させるとともに、製造プロセスに起因するセル特性のばらつきが抑制された半導体記憶装置を提供する。

【解決手段】半導体基板と、少なくとも1つの島状半導体層110、該島状半導体層110の側壁の周囲の全部又は一部に形成された電荷蓄積層513及び制御ゲート523から構成される少なくとも1つのメモリセルとを有する半導体記憶装置であって、前記メモリセルの島状半導体層110が不純物拡散層により前記半導体基板から電気的に絶縁されてなる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】ワイドギャップ半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

記憶装置

【課題】電力が供給されない状況でも記憶内容の保持が可能であり、記憶素子を構成するトランジスタをオンすることなく、記憶したデータを高速で読み出すことができる記憶装置を提供する。

【解決手段】記憶装置において、酸化物半導体層をチャネル領域として有するトランジスタ及び保持容量素子を有するメモリセルと、容量素子と、を電気的に接続させてノードを構成し、該ノードは保持容量素子を介した容量結合により保持データに応じて昇圧され、この電位を増幅回路によって読み出すことで、データの識別を行うことができる。

(もっと読む)

101 - 120 / 2,403

[ Back to top ]