Fターム[5F101BE11]の内容

不揮発性半導体メモリ (42,765) | 周辺技術 (5,862) | 電源回路 (109)

Fターム[5F101BE11]の下位に属するFターム

Fターム[5F101BE11]に分類される特許

1 - 20 / 27

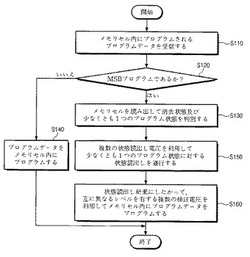

不揮発性メモリ装置、不揮発性メモリ装置のプログラム方法、不揮発性メモリ装置を含むメモリシステム

【課題】向上された信頼性を有する不揮発性メモリ装置のプログラム方法が提供される。

【解決手段】本発明のプログラム方法は、第1メモリセルトランジスターの閾値電圧がプログラム状態から移動する傾向を判別する段階と、判別結果に応答して、複数の検証電圧の中で第1検証電圧を選択する段階と、第1メモリセルトランジスターの閾値電圧が変化するように第1メモリセルトランジスターをプログラムする段階と、で構成される。プログラムする段階は第1メモリセルトランジスターの閾値電圧が十分に変化されたかを第1検証電圧を利用して検証する段階を含む。判別する段階は第1メモリセルトランジスターの閾値電圧の第1範囲からの変化を判別する段階を含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】正確に書き込み動作を行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】

複数の素子分離絶縁膜は、半導体層中に形成され、第1方向を長手方向とする。複数の素子形成領域は、素子分離絶縁膜により分離して形成される。素子形成領域にはメモリストリングが形成される。複数の素子形成領域群が素子形成領域により構成される。メモリセルアレイは、第1方向と直交する第2方向において、前記素子形成領域群の間隔が前記素子形成領域群の中の前記素子形成領域の間隔より大きくされている。制御回路は、前記メモリセルアレイに対する書き込み動作を、前記素子形成領域群ごとに実行する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、を有し、駆動回路は、

データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体集積回路内の抵抗素子の抵抗値のばらつきを抑制した半導体装置を提供する。

【解決手段】半導体装置は基板を備える。第1の絶縁膜は基板上に設けられる。第1の抵抗部は第1の絶縁膜上に設けられる。境界膜は第1の抵抗部上に設けられる。第2の抵抗部は境界膜上に設けられる。第2の絶縁膜は、第2の抵抗部上に設けられている。第1の導電部および第2の導電部は、第2の絶縁膜上に設けられ、互いに絶縁されている。第1の導電部は、第2の絶縁膜および第2の抵抗部を貫通して境界膜の表面に接触する第1のコネクト部を含む。第2の導電部は、第2の絶縁膜および第2の抵抗部を貫通して境界膜の表面に接触する第2のコネクト部を含む。第1の抵抗部は、一端において第1のコネクト部を介して第1の導電部に電気的に接続され、かつ、他端において第2のコネクト部を介して第2の導電部に電気的に接続された抵抗素子である。

(もっと読む)

フラッシュEEPROM(FLASHEEPROMMEMORY)の消去方法

【課題】電荷の蓄積を制御することによりメモリセルを消去するフラッシュEEPROMの消去方法を提供する。

【解決手段】フラッシュメモリの消去方法は、F/Nトンネリング期間において、ウェル電極と第二半導体領域に対し正極性の第一電圧バイアスを印加し、且つコントロールゲート電極に対し負極性の第二電圧バイアスを印加するステップと、F/Nトンネリング期間のあとのトラップ減少期間において、ウェル電極と第二半導体領域に対し正極性の第三電圧バイアスを印加し、且つコントロールゲート電極に対し第一ゼロ電圧バイアスを印加するステップと、トラップ減少期間のあとのトラップアシストトンネリング期間において、コントロールゲート電極に対し負極性の第四電圧バイアスを印加し、且つウェル電極と第二半導体領域に対し第二ゼロ電圧バイアスを印加するステップと、を有する。

(もっと読む)

半導体メモリ装置及びその動作方法

【課題】 最上の動作条件を設定し、それによって半導体メモリ装置を動作させることで半導体メモリ装置の動作特性を向上させることができる不揮発性メモリ装置及びその動作方法を提供する。

【解決手段】 ビットラインBLとソースラインSLとの間に連結されるチャンネル層SCを有するメモリストリングMSを含むメモリブロックと、チャンネル層SCにホットホールhを供給し、メモリストリングMSに含まれたメモリセルCの消去動作を行うように構成された動作回路グループと、チャンネル層SCにホットホールhが目標量以上に供給されれば、ブロック消去イネーブル信号BERASE_ENを出力するように構成された消去動作決定回路460と、ブロック消去イネーブル信号BERASE_ENに応答して動作回路グループが消去動作を行う時点を制御するように構成された制御回路450と、を含む。

(もっと読む)

半導体記憶装置

【課題】消去回数の増加を抑制し、書き込み速度の向上及びメモリセルの劣化を防止することが可能な半導体記憶装置を提供すること。

【解決手段】読み出しレベルに応じてデータを保持可能なセルMCが形成されたセルアレイ1と、前記セルMCに書き込まれた回数N(N:0以上の整数)をカウントし、その回数に応じて書込電圧Vpgm及び読出電圧Vcgrを前記セルに転送する制御部9と、前記書込電圧を用いてデータを書み込み、前記読出電圧を発生し、データを読み出す電圧発生回路とを具備し、書込要求があると、前記読出電圧を発生させ、前記データを読み出し、読み出された閾値電圧より高い閾値電圧に遷移させる前記書き込み電圧を前記電圧発生回路に発生させ、前記セルへの前記回数N回目(≧2)の書き込み要求が規定値に達していると、前記制御部は前記セルが保持する前記データを消去させる。

(もっと読む)

不揮発性記憶装置、集積回路装置及び電子機器

【課題】過消去ビットの発生を抑制してエンデュランス特性等を向上させることができる不揮発性記憶装置、集積回路装置及び電子機器等を提供すること。

【解決手段】不揮発性記憶装置は、電気的に書き換え及び消去可能な複数の不揮発性メモリーセルM11〜M44を有するメモリーセルアレイと、複数の不揮発性メモリーセルのうちの消去対象メモリーセルに対する消去動作の制御を行う消去制御回路ERCNとを含む。消去制御回路ERCNは、消去対象メモリーセルが多い場合には、消去対象メモリーセルに対応するビット線BL1〜BL4がフローティング状態に設定される第1の消去動作制御を行う。消去対象メモリーセルが少ない場合には、消去対象メモリーセルに対応するビット線BL1〜BL4が低電位電源電圧VSSに設定される第2の消去動作制御を行う。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位変換回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体記憶装置

【課題】メモリセルに負の閾値電圧を設定することができ、しかも安定な動作が可能な半導体記憶装置を提供する。

【解決手段】ワード線、及びビット線に接続された複数のメモリセルがマトリックス状に配置され、前記メモリセルに負の閾値電圧を設定することが可能なメモリセルアレイと、前記ワード線、及びビット線の電位を制御する制御回路と、前記制御回路は、前記ビット線のうち第1のビット線BLoに接続されたメモリセルから負の閾値電圧の読み出し動作を行なう場合、前記第1のビット線に隣接して配置された第2のビット線BLeと、前記メモリセルアレイが形成されたウェルと、前記メモリセルアレイのソース線SRCに、正の第1の電圧Vfixを供給し、選択セルのワード線に前記第1の電圧より低い正の電圧を供給する。

(もっと読む)

半導体集積回路

【課題】固定電位と入力信号を比較するカレントミラー型差動増幅器において、入力信号の立ち下り時に出力信号の遷移の遅れを改善して入力信号の立ち上がり時と立ち下がり時で出力信号の遷移時間差を少なくする。

【解決手段】カレントミラー型差動増幅器1-1 のミラートランジスタの共通ゲート端子のノードGPと定電流源回路TNCSの一端との間に、差動増幅器の出力信号OUTnをゲート入力とするトランジスタTNK1と、差動増幅回路の出力信号とは逆の論理の信号OUTpをゲート入力とするトランジスタTNK2とを直列に接続する。

(もっと読む)

抵抗素子を有する半導体装置及びその製造方法

【課題】基準電圧を調整する回路を構成する抵抗素子を有するフラッシュ記憶素子である半導体装置及びその製造方法を提供する。

【解決手段】フラッシュ記憶素子である半導体装置の製造方法は、半導体基板上にトレンチを定義する鋳型パターンMLDPを形成し、鋳型パターンMLDP上にトレンチを横切る抵抗パターンRPを形成し、抵抗パターンRP上に互いに離隔された第1及び第2導電パターン210、220を形成し、第1及び第2導電パターン210、220に各々接続する第1及び第2配線UL1,UL2を形成する段階を有し、第1及び第2導電パターンUL1,UL2は鋳型パターンMLDPの上部に各々形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】データ消去の単位となるブロックの集合である複数のコアを有し、任意のコアでのデータ書込み又は消去動作と、他の任意のコアでのデータ読出し動作との同時実行を可能とした不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装は、メモリセルアレイ401aのデータ書き込み・消去の確認読み出し動作で選択されるデータ線DLaと参照信号線REFaの電流を比較するデータ比較回路403aと、メモリセルアレイ401bの通常のデータ読み出し動作で選択されるデータ線DLbと参照信号線REFbの電流を比較するデータ比較回路403bと、参照信号線REFa、REFbにそれぞれ定電流を流すダミーカラムゲート404a、404bと、ダミーカラムゲート404a、404bを並列に駆動する一つの電流源406とを有する。

(もっと読む)

電圧調整系

【課題】上流の電圧発生手段から引き出す電流の量を制限し、これにより回路の占有面積を減らす事ができる電圧調整系を提供する。

【解決手段】電圧を調整するための回路、系、および方法が含まれる。電圧調整系に関する或る実施形態には、出力を有する電圧調整手段430と、その電圧調整手段の出力と並列に接続された複数のステージ442と、が含まれる。各ステージには、ソースフォロワー回路450と、電圧調整手段の出力とそのソースフォロワー回路の入力とのあいだに直列に接続されたサンプルアンドホールド回路446と、が含まれる。

(もっと読む)

半導体装置

【課題】回路面積の増加を抑制しつつ昇圧効率を向上出来る半導体装置を提供すること。

【解決手段】素子領域AAと、前記素子領域AA上に形成された複数のMOSトランジスタTR及び容量素子Cと、複数の前記MOSトランジスタTRが直列接続され、且つ前記MOSトランジスタTRに前記容量素子Cが接続された電圧発生回路4と、前記MOSトランジスタTRのソース及びドレインの少なくともいずれかの領域32上に形成されたコンタクトプラグCP4、CP5と、データを保持するメモリセルMTとを具備し、各々の前記素子領域AAにおいて、ゲート34と前記コンタクトプラグCP4、CP5との間の距離aは、前記直列接続において後段に位置する前記MOSトランジスタTRほど大きくされる。

(もっと読む)

半導体装置

【課題】不揮発性メモリに格納された内部回路の動作特性を設定するチューン情報を、メモリセル微細化時においても、電源投入後、正確かつ安定に読出す。

【解決手段】2つのメモリアレイ(1a、1b)各々のメモリセルに互いに相補なデータをチューン情報としてツインセルモードで格納する。ツインセル(TW1、TW2)は、互いに相補なチューンデータを格納するメモリセル(MCA1,MCA2,MCB1,MCB2)で構成され、2つのツインセルが同一チューン情報を格納する。チューン情報読出モード時、ダブルツインセルモードでメモリセルの選択およびデータ読出を行い、2つのツインセルの記憶情報を読出す。読出回路(5)により読出されたデータ(Q)に従って、対象回路の動作特性を設定する。

(もっと読む)

半導体記憶装置

【課題】チップ面積の増大を抑えてパッドから離れた回路に十分な電源を供給することが可能な半導体記憶装置を提供する。

【解決手段】メモリセルアレイは、複数のメモリセルが行及び列に配置され、行にワード線が配置され、列にビット線が配置されている。メモリセルアレイのビット線方向両側に第1、第2のセンスアンプがそれぞれ配置されている。複数のパッドが配列されたパッド列は、メモリセルアレイのビット線方向一方側に配置されている。第1のソース線及び電源配線は、半導体基板の最上層に形成され、パッド列側の第1のセンスアンプから第2のセンスアンプ側に配置されている。

(もっと読む)

不揮発性半導体記憶装置と、制御信号発生回路およびそれを用いた半導体装置

【課題】プログラム時間が短い不揮発性半導体記憶装置を提供する。

【解決手段】フラッシュメモリ4においてプログラム用の電圧を発生する正昇圧回路50および降圧回路51は、スタンバイモードSTBYではリセット電圧を発生し、プログラムパルス印加モードPPではプログラム電圧を発生し、プログラムベリファイモードPVではプログラムベリファイ電圧を発生し、モードPP,PVの各々の終了後にプログラム電圧とプログラムベリファイ電圧の間のホームポジション電圧を発生する。したがって、モードPP,PVの各々を行なう度に電源のセットアップおよびリセットを行なっていた従来に比べ、プログラム時間が短くなる。

(もっと読む)

不揮発性半導体メモリ

【課題】チップサイズの増大なく、電源電位を安定供給するレイアウトを提案する。

【解決手段】本発明の例に係る不揮発性半導体メモリは、複数のセルユニットから構成されるメモリセルアレイ12A,12Bと、メモリセルアレイ12A,12Bの第1方向の一端側に配置される電源パッド19と、メモリセルアレイ12A,12Bの第1方向の他端側に配置されるページバッファ13A−u,13B−uと、メモリセルアレイ12A,12B上に配置され、第1方向に延びる複数のビット線BL(M1)と、メモリセルアレイ12A,12B上の複数のビット線BL(M1)上に配置され、電源パッド19及びページバッファ13A−u,13B−uを接続する第1電源線Vss(M2)とを備える。

(もっと読む)

半導体集積回路装置及び半導体記憶装置のテスト方法

【課題】信頼性を向上出来る半導体集積回路装置及び半導体記憶装置のテスト方法を提供すること。

【解決手段】 複数の不揮発性メモリセルMCを有するメモリブロックを備え、該メモリセルのテストを行う半導体メモリ2と、前記半導体メモリ2の前記テストを制御するテスト制御回路3とを具備し、前記テスト回路3は、前記メモリセルのゲート電圧を変化させつつ前記メモリセルからのデータ読み出し動作を、前記メモリブロック単位で行うように前記半導体メモリを制御する制御部21と、前記半導体メモリ2において不良と判断された前記メモリセルの数を、各々の前記ゲート電圧毎にカウントするカウンタ部22とを備え、前記カウンタ部22におけるカウント数が、前記ゲート電圧を変化させた際に連続して一定の範囲内の数であった場合、前記制御部は当該メモリブロックを不良とみなす。

(もっと読む)

1 - 20 / 27

[ Back to top ]