Fターム[5F101BE14]の内容

不揮発性半導体メモリ (42,765) | 周辺技術 (5,862) | 電源回路 (109) | 昇圧、昇圧回路 (76)

Fターム[5F101BE14]に分類される特許

1 - 20 / 76

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

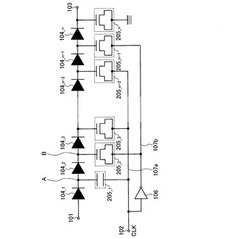

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体装置

【課題】外部からの回路構成情報の呼び出し処理を不要にして、電源投入後すぐに動作できる半導体装置を提供する。

【解決手段】半導体装置は、ワード線とデータ線とが交差する位置にそれぞれ配置された複数の不揮発メモリセル1100を有する。不揮発メモリセル1100の出力にはインバータ回路が接続され、さらに不揮発メモリセルの出力とWBL(Write Bit Line)との間に第1トランジスタM1と、第1トランジスタよりも抵抗が低い第2トランジスタM2とを備える。インバータ回路の出力とRBL(Read Bit Line)との間にはトランスファーゲートを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】容量素子が占有する回路面積の増大を抑制する。

【解決手段】メモリストリングは、複数の第1導電層、メモリゲート絶縁層、及び半導体層を有する。複数の第1導電層は、半導体基板に対して実質的に垂直方向に所定ピッチをもって配列され、メモリトランジスタのゲートとして機能する。半導体層は、複数の第1導電層と共にメモリゲート絶縁層を一方の側面で挟み、半導体基板に対して実質的に垂直方向に延び、メモリトランジスタのボディとして機能する。第1キャパシタは、複数の第2導電層を有する。複数の第2導電層は、半導体基板に対して実質的に垂直方向に所定ピッチをもって配列され、第1キャパシタの電極として機能する。制御回路は、複数の第1導電層に印加される電圧に応じて、複数の第2導電層の各々に印加する電圧を制御し、これにより第1キャパシタの容量を変化させる。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

半導体装置の駆動方法

【課題】半導体装置の駆動方法を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のトランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電位を保持させることで行う。メモリセルの読み出しは、ビット線にプリチャージ電位を供給した後ビット線への電位の供給を止め、ビット線の電位がプリチャージ電位に保たれるか、または電位が下がるか、により行う。

(もっと読む)

記憶回路

【課題】消費電力を抑えることができる記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性のメモリに相当する記憶部に記憶されていたデータを、不揮発性のメモリに相当する記憶部に設けられた容量素子によって保持する記憶回路である。不揮発性記憶部では、酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、容量素子に保持された信号は長期間にわたり保持することができる。こうして、記憶回路は電源の供給が停止している間も論理状態(データ信号)を保持することが可能である。また酸化物半導体層にチャネルが形成されるトランジスタのゲートに印加する電位を、電源電位を供給する配線と前記トランジスタのゲートとの間に設けられた昇圧回路によって高くすることで、1つの電源電位であっても誤動作なくデータ信号の保持を行うことが可能である。

(もっと読む)

半導体集積回路

【課題】電荷転送効率が高い転送トランジスタを備える半導体集積回路を提供することを目的とする。

【解決手段】実施形態に係る半導体集積回路は、ゲート電極を有し、当該ゲート電極及び一の拡散層が第1配線でダイオード接続された転送トランジスタと、クロック信号が供給されるクロック信号線とを備え、前記クロック信号線の一部である第1部分クロック信号線の少なくとも一部が前記ゲート電極上に形成されていることを特徴とする。

(もっと読む)

不揮発性メモリ装置

【課題】 パストランジスタ間の空間確保が可能な不揮発性メモリ装置を提供する

【解決手段】 不揮発性メモリ装置100が備える行デコーダ120は、パストランジスタ部123_L、123_Rを含む。パストランジスタ部123_L、123_Rは、メモリブロック110の左右に配列される。ブロック選択信号BLKWL1によって共通ゲートを形成するパストランジスタ端Pass TR 0とパストランジスタ端Pass TR 8とは、選択的に活性化される第1駆動信号ラインSI1及び第2駆動信号ラインSI2によって独立して駆動される。互に異なるブロック選択信号BLKWLによって駆動されるパストランジスタは、1つの活性領域の上に形成され得る。これにより、1つの活性領域の上に2つのパストランジスタを形成する場合、パストランジスタ部123_L、123_Rのチャンネル方向の大きさを減らすことができる。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

半導体集積回路

【課題】不揮発性メモリを搭載した半導体集積回路において、外部端子を通して不揮発性メモリの特性テストを実施し、更に、その外部端子にサージ電圧が印加された場合であっても、そのサージ電圧が不揮発性メモリに伝わることを防止する。

【解決手段】半導体集積回路は、不揮発性メモリと、不揮発性メモリに対するデータ書き込み時、書き込み電圧が印加される書き込み制御線と、書き込み制御線に接続された第1ノードと、第1スイッチ回路を介して第1ノードに接続された外部端子と、スイッチ回路を介さずに外部端子に接続された第1ESD保護回路と、動作モードに応じて第1スイッチ回路をON/OFF制御する制御回路と、を備える。動作モードは、外部端子を用いて不揮発性メモリの特性テストを行うテストモードと、外部端子を使用しないユーザモードと、を含む。テストモードにおいて、制御回路は、第1スイッチ回路をONする。ユーザモードにおいて、制御回路は、第1スイッチ回路をOFFする。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

ICカード表示システム

【課題】カード所有者がカード内に蓄積された情報を知りたい場合等に、外部のカード読取装置を用いてカード内に蓄積された情報を解読し、カード読取装置に搭載されているディスプレイ上に前記の蓄積情報を読み出さなければならないという不便さがあった。

【解決手段】ICカード本体と、ICカード本体における外部からの機械的な変形を電力に変換するセルフ電源装置と、ICカード本体の外側へ露出して表示を行うディスプレイ面を有し、セルフ電源装置で発生した電力の供給を受けてディスプレイ面に情報を表示する表示装置とを備えるICカード表示システムが提供される。

(もっと読む)

不揮発性メモリ装置

【課題】一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供することによって、読出しマージン減少による信頼性の下落を防止できる不揮発性メモリ装置が提供される。

【解決手段】本発明の実施形態による不揮発性メモリ装置は、基板と直交する方向に積層された複数のメモリセルを含むメモリセルアレイと、ワードラインを通じて前記メモリセルアレイに連結された行選択回路と、前記ワードラインに提供される電圧を発生する電圧発生回路と、を含み、前記電圧発生回路は、目標電圧レベルまで段階的に増加させる方式に前記電圧を発生する。本発明の実施形態による不揮発性メモリ装置は、一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供できる。したがって、読出しマージン減少による信頼性の下落が防止され得る。

(もっと読む)

半導体記憶装置及びその高電圧制御方法

【課題】チャージポンプ等の高電圧生成部の回路面積を削減する。

【解決手段】半導体記憶装置は、ワードライン及びビットラインが接続されマトリクス状に配置された複数のメモリセル21と、ワードラインを駆動する複数のワードラインドライバ23a及び23b、電源電圧を昇圧して高電圧を生成するチャージポンプ11と、複数のメモリセル21のうちアクセスに関係のある箇所には高電圧が印加され、アクセスに関係のない箇所には電源電圧が印加されるように制御するX方向高電圧制御回路31及びY方向高電圧制御回路32とを備える。

(もっと読む)

半導体記憶システム

【課題】 複数のチップを実装した場合において、複数のチップ間で通信する通信線を設けることなく、ピーク電流を抑制可能な半導体記憶システムを提供する。

【解決手段】 半導体記憶システムによれば、電源配線81は、第1の半導体記憶装置71aと第2の半導体記憶装置71bに共通接続され、第1、第2の半導体記憶装置に電源を供給する。電圧検知回路74a,74b,74cは、第1、第2の半導体記憶装置のそれぞれに設けられ、電源配線の電源電圧を検知する。制御回路7は、第1、第2の半導体記憶装置のそれぞれに設けられ、電圧検知回路により電源電圧の低下が検知された場合、電源電圧が復帰するまで、第1、又は第2の半導体記憶装置の動作を、次の動作に遷移させない。

(もっと読む)

半導体装置

【課題】半導体装置を高集積化する。

【解決手段】本実施形態の半導体装置は、絶縁体内に設けられ、半導体集積回路を含んでいる半導体基板70と、絶縁体の開口部POPを介してその上面が露出するパッド90と、パッド90下方において半導体基板70のキャパシタ領域91内に設けられる複数のキャパシタ1と、を具備し、キャパシタ1は、所定の被覆率を満たすように、パッド90下方のキャパシタ領域91内に設けられ、キャパシタ1の2つの電極にそれぞれ接続されるコンタクト18A,18Gは、開口部POPと上下に重ならない位置に設けられている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の小型化を図ること。

【解決手段】第1の領域IにフラッシュメモリセルFLを形成する工程と、第2の領域IIにキャパシタQの第1の電極11aを形成する工程と、第2の絶縁膜14として第1の酸化シリコン膜14a、窒化シリコン膜14b、及び第2の酸化シリコン膜14cをこの順に形成する工程と、第1の電極11aの一部領域CRにおける窒化シリコン膜14bと第2の酸化シリコン膜14cとを除去する工程と、第3の領域IIIHにおける第1の絶縁膜10と第2の絶縁膜14とをウエットエッチングする工程と、キャパシタQの第2の電極30aを形成する工程と、一部領域CRにおける第1の酸化シリコン膜14aをエッチングして除去する工程とを有する半導体装置の製造方法による。

(もっと読む)

不揮発性半導体記憶装置

【課題】各メモリセルの書込消去特性を極力一定にできる不揮発性半導体記憶装置を提供する。

【解決手段】複数のメモリセルトランジスタMTは、活性領域Saが素子分離溝2によって互いに分離している。これらのメモリセルトランジスタMTは、それぞれ、活性領域Saの上面上または上方にトンネル絶縁膜3を介して電荷蓄積機能を有する電荷トラップ膜4を備えている。積層絶縁膜Bは、トンネル絶縁膜3および電荷トラップ膜4を少なくとも含んで構成され、トンネル絶縁膜3が素子分離溝2の内面に沿って形成されると共に電荷トラップ膜4がトンネル絶縁膜3の上面に沿って積層されており、素子分離溝2内の全領域に埋込まれている。

(もっと読む)

半導体記憶装置

【課題】書き込み/消去の繰り返しによる信頼性の低下を抑制することが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ウェル上にトンネル絶縁膜を介して形成された浮遊ゲートに蓄積する電荷量を制御することにより電気的にデータを書き換え可能な複数のメモリセルを、有するメモリセルアレイと、ウェルに印加するための出力電圧を出力する出力端子と、入力電圧を昇圧して設定された電圧を出力端子に出力する第1のポンプ回路と、入力電圧を昇圧して設定された電圧を出力端子に出力し、第1のポンプ回路よりも高い電圧を出力可能な第2のポンプ回路と、第1のポンプ回路または第2のポンプ回路の少なくとも何れか一方を昇圧動作させるためのアシスト信号を出力するポンプ切替検知回路と、出力電圧の目標電圧を設定するための設定値に基づいて、第1のポンプ回路および第2のポンプ回路の目標電圧を設定する消去パルス制御回路と、を備える。

(もっと読む)

1 - 20 / 76

[ Back to top ]