Fターム[5F101BH13]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | エッチング (993)

Fターム[5F101BH13]の下位に属するFターム

ドライエッチング(方向性エッチング) (440)

ウェットエッチング(異方性エッチング) (424)

Fターム[5F101BH13]に分類される特許

121 - 129 / 129

半導体装置の製造方法

【課題】 制御用電極と電荷蓄積素子の他に、アシストゲート電極を備えるフラッシュメモリ製造時において、アシストゲートの断線を抑える。

【解決手段】 半導体基板表面に、第1電極を、所定の間隔をおいて形成し、第1電極に挟まれた領域上に第2電極用の材料膜として第2導電膜を形成する。次に、第2導電膜上に絶縁膜を形成し、この絶縁膜上に、第3電極用の材料膜として第3導電膜を形成する。次に、第3導電膜をパターニングして、第3電極を形成する。このとき、第1の電極上に第3導電膜を所定の膜厚分残す条件でパターニングを行う。次に、第3電極と残存する第3導電膜をマスクとして、絶縁膜を除去し、更に、第3電極と残存する第3導電膜と絶縁膜とをマスクとして、第2導電膜をパターニングし、同時に、第1電極上に残した第3導電膜を完全にエッチングする。

(もっと読む)

微粒子含有体及び微粒子含有体の製造方法並びに記憶素子、半導体装置及び電子機器

【課題】良好な特性が得られる微粒子含有体と、比較的少ない手間で良好な特性の微粒子含有体を製造できる微粒子含有体の製造方法を提供すること。

【解決手段】シリコン基板100の表面に、膜厚が約50nmのシリコン酸化膜110を熱酸化によって形成する。シリコン酸化膜110中に、約30keVの注入エネルギーで、負イオン注入法によって銀を注入する。銀が注入されたシリコン酸化膜110を、200℃よりも高く、かつ、銀の融点未満の温度で熱処理して、銀微粒子を形成する。酸化雰囲気中で熱処理をして、微粒子の表面部分を酸化して、被覆層としての酸化銀140を形成する。ナノメートルサイズの複数の微粒子130および被覆層140を、少ない工程で形成する。

(もっと読む)

半導電性金属酸化物薄膜の強誘電性メモリトランジスタ

【課題】シンプルな製造プロセスによる新規なトランジスタ構造を提供する。

【解決手段】本発明によるトランジスタは、半導電性金属酸化物チャネル層(51)と、半導電性金属酸化物チャネル層(51)に提供されたソース領域(64)およびドレイン領域(65)と、ソース領域(64)とドレイン領域(65)との間、かつ半導電性金属酸化物層(51)の上のゲート構造とを備える。その半導電性金属酸化物が、インジウム酸化物と、ルテニウム酸化物と、タングステン酸化物と、モリブデン酸化物と、チタン酸化物と、鉄酸化物と、スズ酸化物と、亜鉛酸化物と、CeO2と、Ga2O3と、SrTiO3と、LaFeO3と、CrxTiyO3とからなる群から選択される。

(もっと読む)

NAND型不揮発性半導体記憶装置及びその製造方法

【課題】 シャント部付近のWLのオープンを抑制し、安定した歩留りを得ることが可能なNAND型不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成された複数のゲートが、前記半導体基板に形成されたソース及びドレインを共有して、直列に接続された複数のNAND列を具備し、各前記NAND列の両端に配置されるセレクトゲート10と、前記セレクトゲート間に配置された電荷蓄積領域であり、前記セレクトゲートにより制御される制御ゲートを構成する複数のワードライン9と、隣接する前記NAND列間の、所定位置で分断された前記セレクトゲート10間に形成され、前記半導体基板と上層配線とのコンタクトとなるシャント部11を備え、分断された前記セレクトゲートは、夫々隣接する前記セレクトゲートと短絡されている。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】 本発明は、シャロートレンチアイソレーション(shallow trench isolation:STI)工程が適用されるフラッシュメモリ素子の信頼性を向上させ且つ縮小化を図ることが可能なフラッシュメモリ素子の製造方法を提供することを目的としている。

【解決手段】 半導体基板に突出構造の素子隔離膜を形成する段階と、傾斜イオン注入工程を行い、突出構造の素子隔離膜を含んだ全体構造上にイオン注入層を形成する段階と、前記イオン注入層を除去して前記突出構造の素子隔離膜をニップル構造の素子隔離膜に作る段階と、酸化工程でトンネル酸化膜を形成する段階と、前記ニップル構造の素子隔離膜の間に孤立形態のフローティングゲートを形成する段階とを含む構成としたことを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、信頼性の高く、且つしきい値電圧の変化量を高めることが可能な半導体不揮発性記憶素子を有する半導体装置の作製方法を提供する。また、信頼性の高い半導体不揮発性記憶素子を有する半導体装置を、大面積基板を用いて製造する方法を提供する。

【解決手段】本発明は、固溶限界を超えるシリコンを有する固溶体をターゲットとしてスパッタリングを行い、固溶体の主成分である金属元素の導電層と、シリコン粒子とからなる導電膜を成膜した後、金属元素の導電層を除去してシリコン粒子を露出する。また、当該シリコン粒子をフローティングゲート電極とする半導体不揮発性記憶素子を有する半導体装置を作製する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の信頼性の劣化を抑制しつつ、トレンチ内の内壁酸化膜に多量の窒素を導入する。

【解決手段】シリコン基板1の素子分離領域に形成したトレンチ2の内壁を酸化して内壁酸化膜3を形成する。当該内壁酸化膜3に対しては、熱窒化処理とラジカル窒化処理との2つの窒化処理が行われる。熱窒化処理によって内壁酸化膜3とシリコン基板1との界面近傍に第1窒化層3aが形成され、ラジカル窒化法によって内壁酸化膜3の表面に第2窒化層3bが形成される。前記熱窒化処理においては、活性領域に形成される半導体素子の信頼性が生じない程度に、導入する窒素の量を抑制する。

(もっと読む)

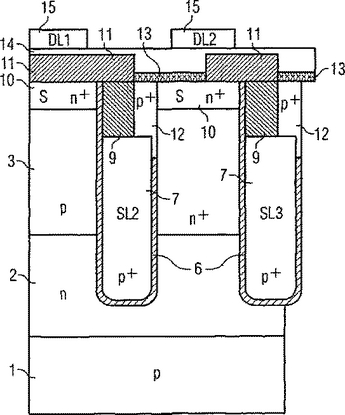

ビット線構造およびその製造方法

本発明は、表面ビット線(DLx)および埋め込みビット線(SLx)を備えたビット線構造に関するものである。これに関して、埋め込みビット線(SLx)は、トレンチ絶縁層(6)を備えたトレンチに形成されており、トレンチの上部に設けられた被覆接続層(12)と自動調心電極層(13)とを介して形成された接触部とともに、ドープ領域(10)に接続されている。  (もっと読む)

(もっと読む)

半導体装置の配線構造体及びその形成方法

【課題】 半導体装置の配線構造体およびその形成方法を提供する。

【解決手段】 この半導体装置は半導体基板100上に配置された層間絶縁膜、前記層間絶縁膜を貫通する第1コンタクト構造体181および第2コンタクト構造体182、前記層間絶縁膜上に配置されて前記第1コンタクト構造体と前記第2コンタクト構造体に連結される金属配線220を具備する。この際、前記第1コンタクト構造体は順次に積層された第1プラグおよび第2プラグ200を含み、前記第2コンタクト構造体は前記第2プラグを含む。

(もっと読む)

121 - 129 / 129

[ Back to top ]