Fターム[5F101BH13]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | エッチング (993)

Fターム[5F101BH13]の下位に属するFターム

ドライエッチング(方向性エッチング) (440)

ウェットエッチング(異方性エッチング) (424)

Fターム[5F101BH13]に分類される特許

41 - 60 / 129

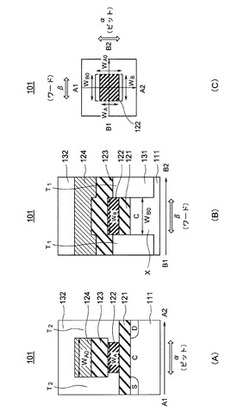

半導体記憶装置及びその製造方法

【課題】電荷蓄積膜を備える半導体記憶装置に関し、電荷蓄積膜の電荷保持特性を向上させる。

【解決手段】ビット線とワード線とを有する半導体記憶装置(101)は、基板(111)と、前記基板上に形成された第1のゲート絶縁膜(121)と、前記第1のゲート絶縁膜上に形成された電荷蓄積膜(122)と、前記電荷蓄積膜上に形成された第2のゲート絶縁膜(123)と、前記第2のゲート絶縁膜上に形成されたゲート電極(124)とを備え、前記電荷蓄積膜のビット線方向の幅が、前記ゲート電極のビット線方向の幅よりも狭くなっている、又は、前記電荷蓄積膜のワード線方向の幅が、前記第1のゲート絶縁膜下の前記基板内に形成されるチャネル領域のチャネル幅よりも狭くなっている。

(もっと読む)

半導体装置

【課題】チャネル長を、トランジスタごとに自由に設計が可能な半導体装置を提供する。

【解決手段】複数の半導体柱2が立設された半導体基板1と、半導体柱2の外周面に設けられたゲート絶縁膜7と、半導体柱2の外周面を覆うゲート電極8と、半導体柱2の上側に設けられた第1不純物拡散領域3と、半導体柱2の下側に設けられた第2不純物拡散領域4と、を備え、第1不純物拡散領域3の厚さが半導体柱2ごとに異なっていることを特徴とする半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、半導体装置の製造方法等に関し、特にプラズマダメージを受けたゲート絶縁膜のダメージ層を除去し、ゲート絶縁膜の信頼性を向上させることのできる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、MONOS型メモリトランジスタ領域101及びトランジスタ領域100を同一の半導体基板に有する場合、MONOS型メモリトランジスタ領域の半導体基板上にトンネル酸化膜7を形成し、そのトンネル酸化膜7上及びトランジスタ領域のゲート絶縁膜5上に窒化シリコン膜8を形成し、その上に酸化シリコン膜9を形成する。MONOS型メモリトランジスタ領域にマスク膜10を形成し、マスク膜10を用いて酸化シリコン膜9を除去し、窒化シリコン膜8をドライエッチングにて除去し、トランジスタ領域100のゲート絶縁膜5の上層部分をウェットエッチングにより除去することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】素子分離絶縁膜としてSOG膜を用いる場合に、熱処理でクラックが発生するのを防止できる構成を提供する。

【解決手段】シリコン基板1にゲート絶縁膜4、多結晶シリコン膜5、加工用絶縁膜を形成し、その後トレンチ1aを形成する。トレンチ1a内にシリコン酸化膜8を形成し、ポリシラザンからなる塗布膜を多結晶シリコン膜5の中間高さまで充填する。クラック防止用のシリコン窒化膜9を形成したのち、さらに塗布膜を形成する。熱処理を行うと塗布膜はシリコン酸化膜2、10に転換するが、このとき熱収縮応力により上層のシリコン酸化膜10にクラックが発生することがあるが、シリコン窒化膜9で阻止できる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】隣接したメモリセル間の干渉を抑制できるようにする。

【解決手段】素子分離絶縁膜4の空洞部の形成領域Rが、浮遊ゲート電極FGaと、浮遊ゲート電極FGc、FGdの直下方に位置する活性領域Saとの間に対向した領域内に設けられるため、当該浮遊ゲート電極FGaと素子分離領域Sbを挟んで対向する活性領域Saとの間の結合容量を低減できる。

(もっと読む)

半導体装置の製造方法

【課題】多結晶シリコン膜上に成膜されたシリコンナイトライド膜を除去する際に、多結晶シリコン膜にシリコンダストが付着することを防止する。

【解決手段】 本発明の半導体装置の製造方法は、半導体基板1上にゲート絶縁膜4、多結晶シリコン膜5、親水性を有する膜22、シリコンナイトライド膜23およびシリコン酸化膜24を積層形成し、シリコン酸化膜24とシリコンナイトライド膜23と親水性を有する膜22を加工し、シリコン酸化膜をマスクにして多結晶シリコン膜5を加工し、シリコン酸化膜をマスクにしてゲート絶縁膜4およびシリコン基板1を加工して素子分離溝20を形成し、素子分離溝20内に素子分離絶縁膜21を埋め込み、ウエットエッチングによりシリコンナイトライド膜23を除去することを特徴とする。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】TEG上のパッド部の浸食を防止し、また、実デバイスのパッド部の半田のぬれ性や半田形成後のシェア強度の向上を図る。

【解決手段】半導体ウエハのチップ領域CAの第3層配線M3およびスクライブ領域SAの第3層配線M3を、それぞれ、TiN膜M3a、Al合金膜M3bおよびTiN膜M3cで構成し、チップ領域CAの再配線49上の第2パッド部PAD2を洗浄し、もしくはその上部に無電界メッキ法でAu膜53aを形成する。さらに、Au膜53a形成後、リテンション検査を行い、その後、さらに、Au膜53bを形成した後、半田バンプ電極55を形成する。その結果、TiN膜M3cによってTEGであるスクライブ領域SAの第3層配線M3の第1パッド部PAD1のメッキ液等による浸食を防止でき、また、Au膜53a、53bによって第2パッド部PAD2の半田のぬれ性や半田形成後のシェア強度の向上を図ることができる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】製造が容易な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置1において、シリコン基板11上に積層体ML1、ML2、ML3をこの順に形成する。積層体ML1には下部選択ゲートLSGを設け、積層体ML3には上部選択ゲートUSGを設ける。また、積層体MLにはZ方向に延びる貫通ホール17を形成し、その内部にシリコンピラーSPを埋設する。下部選択ゲートLSGとシリコンピラーSPとの間、及び上部選択ゲートUSGとシリコンピラーSPとの間には、ゲート絶縁膜GDを設ける。そして、このゲート絶縁膜GDを、ボロンを含有したシリコン窒化物により形成する。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜を介して隣接し、それぞれ低い抵抗値を有する複数のシリサイド層を備え、かつ複数のシリサイド層間の耐電圧特性の劣化および短絡を抑えた半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板上に、絶縁膜を介して前記半導体基板の表面に略平行な方向に隣接する複数のSi系パターン部を形成する工程と、前記複数のSi系パターン部および前記絶縁膜上に、前記複数のSi系パターン部に接するように金属膜を形成する工程と、熱処理により前記複数のSi系パターン部と前記金属膜とをシリサイド反応させ、前記複数のSi系パターン部の全部または上側の一部をそれぞれシリサイド層に加工する工程と、前記複数のシリサイド層に平坦化処理を施し、前記絶縁膜上に形成されたシリサイド層を除去する工程と、を含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセル間の干渉を抑制できる不揮発性半導体記憶装置を提供する。

【解決手段】NAND型メモリ1において、半導体基板11の表面上に、トンネル絶縁層12、電荷蓄積層13、電荷ブロック層14を設け、その上に、チャネル長方向に沿ってそれぞれ複数の制御ゲート電極15及びセル間絶縁膜16を交互に設ける。そして、電荷ブロック層14におけるセル間絶縁膜16の直下域に相当する部分14bに塩素を導入し、部分14bの誘電率を電荷ブロック層14における制御ゲート電極15の直下域に相当する部分14aの誘電率よりも低くする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極をパターニングするときに、選択ゲートトランジスタのゲート電極脇のシリコン基板が掘られることを防止する製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板2のメモリセル部上および選択ゲート部上に電極材膜6を形成する工程と、電極材膜6およびハードマスク材膜7、8のうちのセル部に対応する部分を覆う第1のマスク材膜を作成する工程と、選択ゲート部のハードマスク材膜7、8および第1のマスク材膜をマスクとして選択ゲート部の電極材膜6を加工する工程と、電極材膜6、ハードマスク材膜7、8等のうちの選択ゲート部に対応する部分を覆う第2のマスク材膜11を作成する工程と、メモリセル部のハードマスク材膜7、8および第2のマスク材膜11をマスクとして電極材膜6、ブロック膜5およびシリコン窒化膜4を加工する工程とを備えてなる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】個々のメモリセルの電荷蓄積量が多い不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】シリコン基板11上に、それぞれ複数の絶縁膜12及び電極膜13を交互に積層して積層体14を形成する。次に、積層体14を積層方向に貫通する貫通孔15を形成する。このとき、貫通孔15における電極膜13内に位置する部分の側面15aを、貫通孔15の中心軸15cを含む断面において、貫通孔15の内側から見て凹状に湾曲させる。その後、貫通孔15の側面上に電荷蓄積層26を形成し、貫通孔15の内部に半導体ピラー17を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】MONOS型不揮発性記憶装置を含む、高い性能を有する半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、MONOS型不揮発性記憶セルの第1のトランジスタと、記憶セルを制御または駆動するための第2のトランジスタを含む。第1のトランジスタは、ソースドレイン領域12,13,18,19と,ゲート絶縁層22a’と、ゲート電荷蓄積層22b’と、第2のゲート絶縁層22c’と、ゲート導電層14’と、絶縁層16,17、とを有する。ゲート絶縁層22a’は、ソースドレイン領域の一部12,13の上に形成された下層60と、下層60の一部である中心部の上に形成された上層61とを有する。第2のトランジスタの第2のソースドレイン領域12,13,18,19を形成するために用いられたレジストを洗浄除去するときに、下層60と上層61とに区別された。

(もっと読む)

半導体装置およびその製造方法

【課題】歪みの少ないゲート電極を有するEEPROMやNANDフラッシュメモリ等の半導体装置およびその製造方を提供する。

【解決手段】半導体基板11と、半導体基板11の主面に、第1ゲート絶縁膜12を介して形成された第1ゲート電極13と、第1ゲート電極13上に第2ゲート絶縁膜16を介して形成された第2ゲート電極17と、第2ゲート電極17上に形成されるとともに、中央部が外周部より厚く、且つ第2ゲート電極17内に2段凸状に突出したシリサイド膜18と、第1ゲート電極13と、第2ゲート電極17と、シリサイド膜18の側壁にそれぞれ形成された酸化膜21と、第1ゲート電極13および第2ゲート電極17を挟むようにゲート長方向に沿って形成されたソースドレイン不純物層19と、を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】溝部に埋め込まれている絶縁膜とフローティングゲートによる段差部の発生を抑制することにより信頼性の低下を抑制できる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置は、シリコン基板1上に形成されたLOCOS酸化膜2と、LOCOS酸化膜の相互間に位置するシリコン基板上に形成されたトンネル酸化膜3と、トンネル酸化膜及びLOCOS酸化膜上に形成されたフローティングゲート4と、LOCOS酸化膜上に形成され、フローティングゲートの相互間に位置する溝部8と、溝部内に埋め込まれ、溝部上に形成された層間絶縁膜5と、層間絶縁膜及びフローティングゲートの上に形成された誘電体膜6と、誘電体膜上に形成されたコントロールゲート7と、を具備し、層間絶縁膜5の表面はフローティングゲート4の上面より高く形成され、層間絶縁膜の表面にテーパー形状が形成されていることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】スタック構造のゲート電極をドライエッチングによりパターニングする際に、エッチングの終点を確実に検出し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板16上のメモリセルアレイ領域12に形成された複数のフラッシュメモリセル34であって、半導体基板16上にトンネル絶縁膜20を介して形成されたフローティングゲート22Rと、フローティングゲート22R上にONO膜24を介して形成されたコントロールゲート26Rとをそれぞれ有する複数のフラッシュメモリセル34と、半導体基板16上のパッド領域14に形成された複数のダミーセル38であって、半導体基板16上にトンネル絶縁膜20を介して形成され、フローティングゲート22Dと、フローティングゲート22D上にONO膜24を介して形成されたコントロールゲート26Dとをそれぞれ有する複数のダミーセル38とを有している。

(もっと読む)

第1および第2の材料のラインの交互配列を有するフローティングゲートの形成方法

【課題】実施容易なフローティングゲートの製造方法を提供する。

【解決手段】少なくとも2つの重合体を備え、かつ、基板3に垂直のラメラ構造を有するダイブロック共重合体層が、基板に形成された第1のゲート絶縁体4に堆積される。そして、ダイブロック共重合体層の重合体のうちの1つは、除去され、並列の溝が共重合体層に形成される。溝は、第1の金属または半導体材料6により充填され、共重合体層の残りは除去される。第2の誘電材料7が堆積され、第2のゲート絶縁体が形成される。そして、フローティングゲートの第2のゲート絶縁体は、それぞれ第1(6)および第2(7)の材料の、並列の第1および第2のラインの交互配列を備えることになり、第2の材料7は、第1の材料のラインを封入することになる。

(もっと読む)

半導体装置およびその製造方法

【課題】メモリセル内においてチャネル方向で分離し、且つ隣接するメモリセル間で分離する電荷蓄積層を有する半導体装置およびその製造方法を提供すること。

【解決手段】本発明は、溝部12が延伸して設けられた半導体基板10と、溝部の側面に設けられた第1絶縁膜14と、溝部に埋め込まれるように設けられた、第1絶縁膜と異なる材料からなる第2絶縁膜16と、半導体基板上方に設けられた、溝部に交差して延伸するワードライン18と、ワードライン幅方向における中央部下に設けられ、溝部でワードライン延伸方向に分離する、第1絶縁膜と異なる材料からなるゲート絶縁膜28と、ワードライン幅方向における両端部下にゲート絶縁膜を挟むように設けられ、溝部でワードライン延伸方向に分離する電荷蓄積層22と、を具備する半導体装置とその製造方法である。

(もっと読む)

半導体装置の作製方法

【課題】より高集積化され、薄型化及び小型化された半導体装置を作製することを目的の一とする。また、半導体装置において、高性能化、低消費電力化を目的の一とする。

【解決手段】剥離層を用いて基板から剥離された半導体素子層を、他基板に形成され、平坦化された無機絶縁層に覆われた半導体素子層上に積層する。上層の半導体素子層を基板より剥離後、剥離層を除去し半導体素子層下に形成される無機絶縁膜を露出する。平坦化された無機絶縁層及び無機絶縁膜を密着させて接合する。また、半導体素子層の有する半導体層は半導体基板より分離され、作製基板に転置された単結晶半導体層である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 MONOS型メモリセル等のメモリセル当たりに2つの記憶サイトを有する不揮発性半導体記憶装置に好適で、簡単な製造工程により半導体基板表面へのダメージを抑制して記憶サイトを分離可能な製造方法を提供する。

【解決手段】 半導体基板1表面にゲート酸化膜2とゲート電極膜3を堆積し、ゲート電極膜3をパターニングしてゲート電極4を形成し、ゲート酸化膜2を等方性エッチングして、ゲート電極4の周縁部下側に位置するゲート酸化膜2を横方向からエッチング除去し、電荷保持膜5,6を堆積し、ゲート電極4の周縁部下側のゲート酸化膜2がエッチング除去された後の間隙部2aを電荷保持膜5,6により充填し、ゲート電極4をマスクにして不純物注入してゲート電極4の両側にソース及びドレイン領域となる不純物拡散領域7を形成し、電荷保持膜5,6を異方性エッチングでエッチバックする。

(もっと読む)

41 - 60 / 129

[ Back to top ]