Fターム[5F101BH13]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | エッチング (993)

Fターム[5F101BH13]の下位に属するFターム

ドライエッチング(方向性エッチング) (440)

ウェットエッチング(異方性エッチング) (424)

Fターム[5F101BH13]に分類される特許

61 - 80 / 129

不揮発性半導体記憶装置

【課題】電荷トラップの溜まりを防止して書き換え回数を増加させる。

【解決手段】メモリセルMCは、半導体基板10と、この半導体基板上に形成された第1のゲート絶縁層11と、半導体基板10上に第1のゲート絶縁層11を介して形成された浮遊ゲート12と、この浮遊ゲート12上に形成された第2のゲート絶縁層13と、浮遊ゲート12上に第2のゲート絶縁層13を介して形成された制御ゲート14とを有する。メモリセルアレイは、このメモリセルMCを、複数マトリクス状に配列することにより構成されている。第1のゲート絶縁層11は第1の空洞層となっている。

(もっと読む)

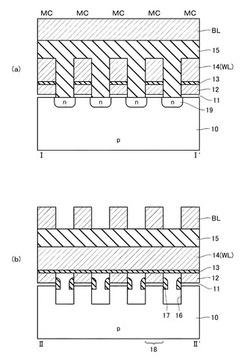

半導体記憶装置及びその製造方法

【課題】メモリセルトランジスタの制御ゲート層相互間及び選択トランジスタの制御ゲート層相互間の距離を十分に小さくして、メモリセルの高集積化を図る半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体基板の表面に平行な第1の方向でそれぞれ2個の電荷蓄積層15とゲート層19とが交互にかつ一列に配列されるように複数のメモリセルが配置され、選択トランジスタの拡散層24が半導体基板の表面に平行で第1の方向と交差する第2の方向に延長されてソース線が構成され、メモリセルトランジスタの拡散層22が半導体基板の表面に平行な第2の方向に延長されてビット線が構成され、メモリセルトランジスタの制御ゲート層17は第1の方向で隣り合う2個の電荷蓄積層15上にゲート間絶縁膜を介して形成されている。

(もっと読む)

不揮発性半導体メモリ及びデータプログラム/消去方法

【課題】電荷トラップ型の不揮発性半導体メモリにおいて、消費電流を低減すること。

【解決手段】不揮発性半導体メモリは、半導体基板1、第1ゲート電極WG、第2ゲート電極CG、電荷トラップ膜22、及びトンネル絶縁膜23を備える。第1ゲート電極WGは、半導体基板1の表面上に第1ゲート絶縁膜10を介して形成される。第2ゲート電極CGは、半導体基板1の表面上に第2ゲート絶縁膜20を介して形成され、第1ゲート電極WGと絶縁膜20を介して隣接する。電荷トラップ膜22は、半導体基板1と第1ゲート電極WGと第2ゲート電極CGとに囲まれたトラップ領域RT中に少なくとも形成される。トンネル絶縁膜23は、電荷トラップ膜22と第2ゲート電極CGとの間に形成される。プログラムあるいは消去において、FNトンネル方式により、第2ゲート電極CGから電荷トラップ膜22へトンネル絶縁膜23を通して電子が注入される

(もっと読む)

半導体装置の製造方法

【課題】所望のエッチングレートでシリコンリッチ膜をエッチングすることが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板10上に、トンネル絶縁膜14、電荷蓄積層16、トップ絶縁膜18からなるONO膜20が形成されている半導体装置の製造方法は、ワードライン22上に、層間絶縁膜24、紫外線吸収膜26、反射防止膜28、キャップ層30を形成する工程と、シリコンリッチ膜である紫外線吸収膜26の紫外線に対する消衰係数を測定する工程と、消衰係数に対応した酸素ガス流量を用いたエッチング条件により、シリコンリッチ膜である紫外線吸収膜26をエッチングする工程と、を有する。

(もっと読む)

半導体素子のコンタクトプラグ製造方法

【課題】ナンドフラッシュメモリ等のソース/ドレインコンタクトプラグを形成する半導体素子のコンタクトプラグ製造方法を提供する。

【解決手段】選択ラインSSLとワードラインWL0,WL1間の露出された半導体基板102に接合領域114a、114bを形成する段階と、選択ラインSSLとワードラインWL0,WL1上に第1の保護膜120を形成する段階と、第1の保護膜120上に絶縁層122を形成する段階と、選択ラインSSL間の第1の保護膜120が露出されるように選択ラインSSL間の絶縁層122にコンタクトホールAを形成する段階と、コンタクトホール側壁に露出された第1の保護膜上に第2の保護膜124を形成する段階と、コンタクトホールA底面の第1の保護膜120を除去する段階、及びコンタクトホールAに導電物質を形成して接合領域114a、114bと連結されるコンタクトプラグを形成する段階とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】仮想接地型フラッシュメモリにおいて、製造が容易で、メモリセルの高集積化、微細化が可能な半導体装置およびその製造方法を提供すること。

【解決手段】本発明は、半導体基板10内に延伸するように設けられたビットライン12と、半導体基板10上に設けられた電荷蓄積層16と、電荷蓄積層16上にビットライン12に交差して延伸するように設けられたワードライン22と、ワードライン22直下の半導体基板10内であり、且つ、ビットライン12間の領域であるチャネル領域24と、を具備し、チャネル領域24上に設けられた電荷蓄積層16のワードライン22幅方向の幅Wが、ワードライン22延伸方向のチャネル領域24の端部Eからチャネル領域24の中央部に向かうに連れて狭くなる半導体装置である。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】コンタクトプラグ間にブリッジが発生するのを防止し、ビット線不良の防止に有効なフラッシュメモリ素子の製造方法を提供する。

【解決手段】半導体基板100上に形成された第1及び第2の層間絶縁膜104,114をエッチングして、セル領域の接合領域を露出させる第1及び第2のコンタクトホール106,116を形成する。このコンタクトホールの内部に第1及び第2の層間絶縁膜の界面よりも低くコンタクトプラグ110,118aを形成する。コンタクトプラグ上部のコンタクトホールの側壁にスペーサ120aを形成する。それによって、例えば導電性残留物層112及び第1及び第2の層間絶縁膜界面に発生したオープンパスのためにドレインコンタクトプラグ間で連結するブリッジを防止する。また、ドレインコンタクトプラグと接続されるビット線にて漏洩電流を誘発するなどの不良を防止し、工程の歩留まり及び素子の信頼性を向上させる。

(もっと読む)

不揮発性半導体記憶装置

【課題】トランジスタ閾値ばらつきの発生を防止し、書き込み速度を高速にする。

【解決手段】メモリセルトランジスタ1の浮遊ゲート電極104a上方の制御ゲート電極106aの膜厚Hcell、選択トランジスタ2の上部ゲート電極106bの膜厚Hsg、浮遊ゲート電極104aの上面と素子分離領域107の上面の高さの差Hebに、Hsg×8/9>Hcell≧Hsg×7/9−Heb×11/9という関係を有するように制御ゲート電極106aの膜厚を上部ゲート電極106bより薄くした不揮発性半導体記憶装置。

(もっと読む)

フラッシュメモリ素子の素子分離膜形成方法

【課題】本発明は、フラッシュメモリ素子の素子分離膜形成方法に関するものであり、PSZ系列の物質を用いて素子分離膜を形成する場合、PSZ膜の蒸着前にトレンチにライナ形態で窒化膜を蒸着した後、エッチング比を用いたエッチング工程を通じてフローティングゲート用導電膜の上部側壁に酸化膜が残留することを防止することにより、後続の誘電体膜蒸着後に誘電体膜厚が増加する現象を除去し、フローティングゲートと誘電体膜との接触面積を増加させ、これを通じてフローティングゲートとコントロールゲートと間のカップリング比(Coupling Ratio)を向上させることができるフラッシュメモリ素子の製造方法に関するものである。 (もっと読む)

半導体素子

【課題】フローティングゲート構造を有し、駆動電圧を低減可能な半導体素子を提供する。

【解決手段】半導体素子10は、n型Siからなる基板1上に形成したSiO2層4上に、電荷蓄積層5,6を順次積層したフローティングゲート構造からなる。電荷蓄積層5は、アンドープのSiからなる量子ドット51a〜51cと、それを被覆する酸化層52とからなる。電荷蓄積層6は、n+Siからなる量子ドット61a〜61cと、それを被覆する酸化層62とからなる。そして、量子ドット61a〜61c中に元来的に存在する電子は、パッド12,13からゲート電極9に印加される電圧に応じて、トンネル接合を介して量子ドット61a〜61cと量子ドット51a〜51cとの間を移動し、量子ドット51a〜51cおよび/または量子ドット61a〜61c中に分布する。この分布状態は、電流ISDによって検出される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル間の容量結合を低減して浮遊ゲート間干渉を抑制することができる不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体基板10、半導体基板10上に形成された第1の絶縁膜11、半導体基板10上に第1の絶縁膜11を介して形成された浮遊ゲート12、この浮遊ゲート12上に形成された第2の絶縁膜13及び浮遊ゲート上に第2の絶縁膜13を介して形成された制御ゲート14を有する複数のメモリセルMCと、半導体基板10に形成されゲート幅方向に隣接するメモリセルMC間を分離するゲート長方向に延びる素子分離絶縁膜17と、素子分離絶縁膜17の上で且つゲート幅方向に隣接する浮遊ゲート12間に形成された空隙部22とを有する。

(もっと読む)

半導体素子の微細パターン形成方法

【課題】工程数を増やすことなく、安価に微細パターンを形成する方法を提供する。

【解決手段】半導体基板上にエッチング対象膜102、ハードマスク膜104及び第1の補助パターンを形成し、第1の補助パターンにシリレーション工程を行う。シリレーションされた第1の補助パターン106aを含む上記ハードマスク膜上に絶縁膜108を形成し、上記シリレーションされた第1の補助パターンの間の絶縁膜108上に第2の補助パターンを形成する。上記絶縁膜が上記第2の補助パターンの下部にのみ残留するようにエッチング工程を行い、上記シリレーションされた第1の補助パターン及び第2の補助パターンをエッチングマスクとして用いるエッチング工程で上記ハードマスク膜をエッチングしてハードマスクパターンを形成する。ハードマスクパターンを用いて上記エッチング対象膜をエッチングする。

(もっと読む)

半導体装置の作製方法

【課題】大面積基板に、高性能な半導体素子、及び集積回路を高スループットで生産性よく作製することを目的とする。

【解決手段】単結晶半導体基板(ボンドウエハー)より単結晶半導体膜を転置する際、単結晶半導体基板を選択的にエッチング(溝加工ともいう)し、作製する半導体素子の大きさに複数に分割された複数の単結晶半導体層を、異種基板(ベース基板)に転置する。従って、ベース基板には、複数の島状の単結晶半導体層(SOI層)を形成することができる。

(もっと読む)

不揮発性メモリ素子の製造方法

【課題】セルの書き込みしきい値電圧の分布を均一にできる不揮発性メモリ素子の製造方法を提供すること。

【解決手段】ゲート導電膜202、ゲート絶縁膜201、及び基板200の一部をエッチングしてトレンチを形成し、該トレンチを埋め込むように素子分離膜を形成する段階と、所定の深さに素子分離膜を後退させる段階と、後退した素子分離膜203Aによって形成される段差に沿って、バッファ膜204Aを形成する段階と、バッファ膜の内側壁に、バッファ膜に対して高いエッチング選択比を有する物質でスペーサスペーサ205Aを形成する段階と、スペーサを用いて、後退した素子分離膜203Aの一部をエッチングし、素子分離膜203A内に溝を形成する段階と、スペーサ205A及びバッファ膜204Aを除去し、バッファ膜204Aが除去された基板200上の段差に沿って誘電体膜を形成し、誘電体膜上にコントロールゲートを形成する段階とを含む。

(もっと読む)

半導体記憶装置の製造方法

【課題】フローティングゲートを有するスプリットゲート型不揮発性半導体記憶装置において、コントロールゲートの側壁に、シリサイド・ショートを防止できるのに十分な高さの側壁絶縁膜を形成することができる製造方法を提供する。

【解決手段】半導体記憶装置の製造方法は、半導体基板1に形成したPウエル4上にゲート絶縁膜2を介してフローティングゲート用の導電体層16を形成する工程と、導電体層16上にTEOS−NSG等の第1のシリコン酸化膜から構成される第1のスペーサ10と、第1のスペーサ10と隣接し第1のシリコン酸化膜10よりもエッチングレートが遅い第2の高温シリコン酸化膜から構成される第2のスペーサ11と、を形成する工程と、第1及び第2のスペーサ10,11をマスクにして導電体層16を選択的に除去する工程と、第1のスペーサ10を除去して導電体層16の一部を露出させる工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】共通ソース線による半導体基板に対するリークを防止する。

【解決手段】ドレイン側領域の素子分離絶縁膜4の上面高さを、ソース側の領域A2の素子分離絶縁膜4の上面高さH2に比較して低く構成している。ドレインコンタクトDCのドレイン領域2aに対する接触性を保持することができ、ソース側ではローカルソース線LSL1がソース領域2bに対して接触する面積をソース領域2b上のシリコン窒化膜12の残留領域分だけ狭く構成できる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】窒化シリコン膜の成膜工程において、ポリメタルゲートの一部を構成する高融点金属の酸化物による基板の汚染を低減する半導体集積回路装置の製造技術を提供する。

【解決手段】タングステン膜を含むゲート電極7A、7B、7C上に窒化シリコン膜11を形成する際、CVD装置のチャンバ内をタングステンの酸化物が還元される雰囲気にし、チャンバ内にアンモニアを供給し続けながら、ウエハ1を600℃以上の温度で昇温する。次に、チャンバ内にアンモニアとモノシランとを供給し、これらのガスを反応させることによって窒化シリコン膜11を堆積する。次に、モノシランの供給を止め、チャンバ内にアンモニアのみを供給し続けながらウエハ1を400℃まで降温した後、チャンバ内を窒素で置換し、ウエハをアンロードする。

(もっと読む)

半導体装置の作製方法

【課題】ゲート絶縁層の膜厚が薄くなった部分、すなわち段差部による半導体素子特性への影響を低減し、半導体素子の信頼性を向上させることを目的とする。

【解決手段】絶縁表面上に半導体層を形成し、半導体層の端部をウェット酸化して第1の絶縁層を形成し、半導体層上および第1の絶縁層上に第2の絶縁層を形成し、第2の絶縁層を介して、半導体層上および第1の絶縁層上にゲート電極を形成する。

(もっと読む)

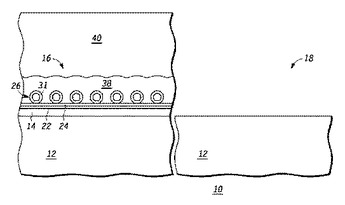

選択領域からナノクラスターを除去する方法

半導体素子を製造する方法は、不揮発性メモリ用の第1部分(16)と第1部分(16)を除く第2部分(18)とを有する半導体層(12)を備えた基板(12)を提供することを含む。半導体層上には第1の誘電体層(14)が形成される。第1の誘電体層上でプラズマ窒化が行なわれる。第1部分上には第1の複数のナノクラスター(20)が、第2部分上には第2の複数のナノクラスター(28)が形成される。第2の複数のナノクラスターは除去され、半導体層上に第2の誘電体層(38)が形成され、第2の誘電体層上に導電層(40)が形成される。  (もっと読む)

(もっと読む)

半導体素子及びその形成方法

【課題】下部領域にコンタクトを通じて電気的に連結される配線を形成する方法を提供する。

【解決手段】本発明の配線の形成方法は、複数の第1領域と、前記第1領域の間に各々配置された複数の第2領域とを有する基板上に絶縁膜を形成し、前記絶縁膜上に前記絶縁膜を貫通する第1コンタクトを通じて各々対応する前記第1領域に電気的に連結される複数の第1配線を形成し、前記第1配線の側面にスペーサを形成し、隣り合う前記スペーサの間の前記絶縁膜を除去して隣り合う前記第1コンタクトの間に対応する前記第2領域を露出する複数のコンタクトホールを形成し、対応する前記コンタクトホールを埋める複数の第2コンタクトを形成して対応する前記第2コンタクトに電気的に連結される複数の第2配線を形成することを特徴とする。

(もっと読む)

61 - 80 / 129

[ Back to top ]