Fターム[5F101BH16]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | 熱処理 (725)

Fターム[5F101BH16]に分類される特許

341 - 360 / 725

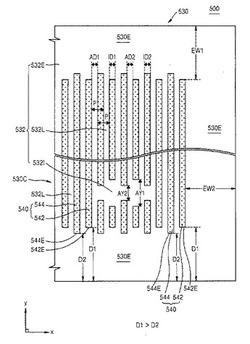

半導体素子及び半導体素子のパターン形成方法

【課題】多様な幅を有するパターンを同時に形成しつつ、一部領域ではダブルパターニング技術によりパターン密度を倍加させる半導体素子のパターン形成工程及び該工程を容易に適用可能な構造の半導体素子を提供する。

【解決手段】半導体素子は、第1方向に相互平行に延びている複数のラインパターンを含む。複数のラインパターンのうちから選択される複数の第1ラインパターンは、第2方向に沿って交互に選択されて両側で各々隣接している2つのラインパターンの両端部のうち、素子領域の第1端部にさらに近い各端部に比べて、第1端部からさらに遠く位置する第1端部を有する。複数のラインパターンのうちから選択される複数の第2ラインパターンは、第2方向に沿って交互に選択され、両側で各々隣接している2つのラインパターンの両端部のうち、第1端部にさらに近い各端部より、第1端部からさらに近く位置する第2端部を有する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】不揮発性メモリの記憶保持特性の向上を図ることができる技術を提供することにある。特に、第1電位障壁膜となる酸化シリコン膜をプラズマ成膜法で形成した場合であっても、酸化シリコン膜の膜質を改善して不揮発性メモリの記憶保持特性の向上を図ることができる不揮発性半導体記憶装置の製造技術を提供する。

【解決手段】第1電位障壁膜EV1の主要構成要素である酸化シリコン膜OX1をプラズマ成膜法により形成した後、高温のプラズマ窒化処理と、一酸化窒素を含む雰囲気中での加熱処理とを組み合わせて実施することにより、酸化シリコン膜OX1の表面に酸窒化シリコン膜SOXを形成し、かつ、酸化シリコン膜OX1と半導体基板1Sの界面に窒素N2を偏析させる。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリセルの特性を向上することが可能な半導体装置を提供する。

【解決手段】半導体装置の不揮発性メモリセルは、アクティブエリア1AA上に設けられたトンネル絶縁膜2と、トンネル絶縁膜上に設けられた浮遊ゲート電極3と、浮遊ゲート電極の上方に設けられた制御ゲート電極10と、浮遊ゲート電極と制御ゲート電極との間に設けられた電極間絶縁膜9とを含み、不揮発性メモリセルのチャネル幅方向の断面において、アクティブエリアの上面のチャネル幅方向の寸法は、トンネル絶縁膜の下面のチャネル幅方向の寸法以下であり、かつ、トンネル絶縁膜の上面のチャネル幅方向の寸法は、浮遊ゲート電極の下面のチャネル幅方向の寸法未満である。

(もっと読む)

半導体装置及びその製造方法

【課題】電荷消去特性及び電荷保持特性に優れた半導体装置を提供する。

【解決手段】半導体領域101と、半導体領域の表面に形成されたトンネル絶縁膜102と、トンネル絶縁膜の表面に形成された電荷蓄積絶縁膜103と、電荷蓄積絶縁膜の表面に形成されたブロック絶縁膜104と、ブロック絶縁膜の表面に形成された制御ゲート電極105と、を具備する半導体装置であって、トンネル絶縁膜は、半導体領域の表面に形成され、シリコン及び酸素を含有する第1の領域102aと、第1の領域の表面に形成され、シリコン及び窒素を含有する第2の領域102bと、電荷蓄積絶縁膜の裏面に形成され、シリコン及び酸素を含有する第3の領域102dと、第2の領域と第3の領域との間に形成され、シリコン、窒素及び酸素を含有し、第2の領域の窒素濃度よりも低い窒素濃度を有し、第3の領域の酸素濃度よりも低い酸素濃度を有する第4の領域102cと、を含む。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】セルトランジスタの動作速度が速く、しきい値の変動が小さい不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】シリコン基板11上にそれぞれ複数のシリコン酸化膜12及びシリコン膜13を交互に積層して積層体14を形成し、積層体14にトレンチ15を形成し、トレンチ15の内面上にアルミナ膜16、シリコン窒化膜17、シリコン酸化膜18をこの順に形成し、シリコン酸化膜18上にチャネルシリコン結晶膜20を形成する。次に、酸素ガス雰囲気中で熱処理を行い、シリコン酸化膜18とチャネルシリコン結晶膜20との界面にシリコン酸化物層21aを形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層に新たな機能を有する素子を設けた半導体装置を提供する。

【解決手段】半導体基板上に形成された第1配線層150、及び半導体素子200を備える。第1配線層150は、絶縁層156と、絶縁層156の表面に埋め込まれた第1配線154とを備える。半導体素子200は、半導体層220、ゲート絶縁膜160、及びゲート電極210を備える。半導体層220は、第1配線層150上に位置する。ゲート絶縁膜160は、半導体層220の上又は下に位置する。ゲート電極210は、ゲート絶縁膜160を介して半導体層220の反対側に位置する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの特性が良好な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置1において、シリコン基板11上にトンネル絶縁層12、電荷蓄積層13及び電荷ブロック層14をこの順に形成し、電荷ブロック層14上に複数の制御ゲート電極15を設ける。電荷ブロック層14は、比誘電率がシリコン窒化物の比誘電率よりも高い金属酸化物により形成し、制御ゲート電極15は、金属、金属シリサイド又はドーパントを含有するシリコンにより形成する。又は、電荷ブロック層14は、シリコン酸化物又はシリコン酸窒化物により形成し、制御ゲート電極15は、金属又は金属シリサイドにより形成する。そして、電荷ブロック層14と各制御ゲート電極15との間に、シリコン窒化物からなるキャップ層20を形成する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 本発明は、MONOS型のメモリセルを備えた不揮発性半導体記憶装置において、キャパシタ素子の単位面積当たりのキャパシタ容量を増加させ、キャパシタ素子の面積を低減することを目的とする。

【解決手段】 キャパシタ素子において、周辺トランジスタのゲート電極の多結晶シリコン膜2を中間電極とし、ゲート絶縁膜1とメモリセルトランジスタのブロック絶縁膜10の両方をキャパシタ絶縁膜とすることにより、キャパシタ素子の単位面積当たりのキャパシタ容量を増加させキャパシタ素子の面積を低減している。

(もっと読む)

酸化膜の作成方法及び半導体装置の製造方法

【課題】低温の酸化処理により酸化膜を形成する。

【解決手段】酸化膜の作成方法は、主鎖にSi−N結合を有する高分子化合物を含む第1の膜16と主鎖にSi−O結合を有する高分子化合物を含む第2の膜15とを積層する工程と、前記第1の膜16及び前記第2の膜15を水蒸気又は水性の雰囲気中で加熱処理し、前記第1の膜16及び前記第2の膜15を酸化膜18に変化させる工程と、を具備する。

(もっと読む)

不揮発性記憶素子、その製造方法及び不揮発性記憶装置

【課題】電気的性能及び耐プロセス性能が優れた不揮発性記憶素子、その製造方法及び不揮発性記憶装置を提供する。

【解決手段】セリウムと、3価を取り得る金属元素であってセリウムとは異なる金属元素と、を含む蛍石型構造の酸化物を含み、印加される電圧及び通電される電流の少なくともいずれかによって互いに異なる抵抗を有する複数の状態の間を遷移可能な記録層を備えたことを特徴とする不揮発性記憶素子が提供される。また、上記の不揮発性記憶素子と、前記不揮発性記憶素子の前記記録層への電圧の印加、及び、前記記録層への電流の通電、の少なくともいずれかによって、前記記録層を前記互いに異なる抵抗を有する複数の状態の間を遷移させて情報を記録する駆動部と、を備えたことを特徴とする不揮発性記憶装置が提供される。

(もっと読む)

不揮発性半導体記憶装置

【課題】高集積化され且つデータ保持特性低下を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置100は、チャネルとなる半導体基板11と、半導体基板11の表面からトンネル絶縁層12及びブロック絶縁層14を介して形成された制御ゲート電極となる導電層15と、トンネル絶縁層12とブロック絶縁層14との間に形成された複数の電荷蓄積層13とを備える。複数の電荷蓄積層13は、トンネル絶縁層12の表面に沿って互いに離間して形成されている。トンネル絶縁層12は、各々の電荷蓄積層13の形成された位置で半導体基板11側に突出するように形成されている。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 隣接するゲート電極間に配置されたシールド電極の電位を安定的に保持し、シールド電極によって近接効果を軽減することが可能な不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】 本発明では、半導体基板1上に互いに隣接して配置された浮遊ゲート11と制御ゲート16とを有するゲート電極G1、G2間に、ゲート側壁絶縁膜22を介してシールド電極25を配置している。そして、このシールド電極25は、少なくとも一部が金属とシリコンからなるシリサイド層で構成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】 メモリセルにおけるショートチャネル効果の抑制と誤書き込みの防止の両方を実現し、不揮発性半導体記憶装置の高性能・低コスト化をはかる。

【解決手段】 半導体基板101上に複数の不揮発性メモリセルを配置して構成される不揮発性半導体記憶装置であって、メモリセルは、基板101の表面部に離間して設けられたソース・ドレイン領域120と、ソース・ドレイン領域120の直下の基板101内に設けられ、基板101よりも誘電率が低い埋め込み絶縁膜151と、ソース・ドレイン領域120の間に形成されるチャネル領域上に設けられた第1ゲート絶縁膜102と、第1ゲート絶縁膜102上に設けられた電荷蓄積層103と、電荷蓄積層103上に設けられた第2ゲート絶縁膜104と、第2ゲート絶縁膜104上に設けられた制御ゲート電極105とを備えた。

(もっと読む)

半導体装置

【課題】コンタクト抵抗が低い半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の半導体基板と、埋め込み酸化膜と、第2導電型の半導体層と、を備えるSOI基板に作られ、前記埋め込み酸化膜は、自己に穿設された、前記半導体基板と前記半導体層とを連通する、第1の開口を有し、前記半導体基板は、その表面部分に埋め込み状態に形成され、前記第1の開口内の前記半導体層の埋設部と互いに電気的に接続している、第2導電型の接続層を有し、前記半導体層及び前記埋め込み酸化膜を貫通して、前記接続層の表面部分に至る第2の開口内に埋め込まれて、側面において前記半導体層と電気的に接続し、底面において前記接続層と電気的に接続する、コンタクト電極と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】素子分離絶縁膜としてSOG膜を用いる場合に、熱処理でクラックが発生するのを防止できる構成を提供する。

【解決手段】シリコン基板1にゲート絶縁膜4、多結晶シリコン膜5、加工用絶縁膜を形成し、その後トレンチ1aを形成する。トレンチ1a内にシリコン酸化膜8を形成し、ポリシラザンからなる塗布膜を多結晶シリコン膜5の中間高さまで充填する。クラック防止用のシリコン窒化膜9を形成したのち、さらに塗布膜を形成する。熱処理を行うと塗布膜はシリコン酸化膜2、10に転換するが、このとき熱収縮応力により上層のシリコン酸化膜10にクラックが発生することがあるが、シリコン窒化膜9で阻止できる。

(もっと読む)

不揮発性半導体装置及び不揮発性半導体装置の製造方法

【課題】ONO膜とシリサイド膜との短絡を起こさないようにし、ONO膜での電荷の不安定や電解分布の不均一、ONO膜の膜質低下などを防止する。

【解決手段】不揮発性半導体記憶装置はワードゲート22とコントロールゲート24と電荷蓄積層14とを具備する。ワードゲート22は半導体基板10のチャネル領域上方に絶縁層12を介して設けられている。コントロールゲート24はワードゲート22の側方に設けられている。電荷蓄積層14はチャネル領域とコントロールゲート24との間、及び、ワードゲート22とコントロールゲート24との間にONO膜で設けられている。コントロールゲート24は、シリサイド層24aと、非シリサイド層24b、24cとを備える。シリサイド層24aはニッケルを含むシリサイドで設けられている。非シリサイド層24b、24cはシリサイド層24aと電荷蓄積層14との間に設けられている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】転位による結晶欠陥不良を防止できるようにする。

【解決手段】周辺回路領域Pにおいて、O3−TEOS膜4cがソース/ドレイン領域2cとSOG膜4bとの間に形成されている。ソース/ドレイン領域2cに導入された不純物イオンの活性化の処理の時点でSOG膜4bに引っ張り応力が発生するものの、O3−TEOS膜4cが介在しているため結晶欠陥が不純物拡散領域2a、2bに発生することを抑制でき転位の発生を抑制できる。

(もっと読む)

半導体記憶素子、半導体記憶素子の製造方法

【課題】従来のSiNを用いた電荷蓄積膜に比べ、高効率に電荷を蓄積および消去でき、かつ、蓄積した電荷を長時間保持する半導体記憶素子、半導体記憶素子の製造方法を得る。

【解決手段】この半導体記憶素子は、半導体基板に設けられたソース領域およびドレイン領域と、ソース領域およびドレイン領域との間の半導体基板上に設けられたトンネル絶縁膜と、トンネル絶縁膜上に設けられた電荷蓄積膜と、電荷蓄積膜上に設けられたブロック絶縁膜と、ブロック絶縁膜上に設けられたゲート電極と、電荷蓄積層とブロック絶縁膜との界面付近に設けられた気体分子を含む領域とを具備する。

(もっと読む)

シリコン酸化膜の形成方法および不揮発性半導体記憶装置の製造方法

【課題】低温で良好な絶縁膜であるシリコン酸化膜を形成する。

【解決手段】シリコン基板1上にトレンチ1a、1bを形成し、シラザン結合を有するポリマーを有機溶媒に溶かした塗布剤を塗布して塗布膜を形成する。塗布膜に含まれる有機溶媒を気化させてポリマー膜を形成する。ポリマー膜に90℃以下の温度で紫外線を照射し、そのポリマー膜を50℃以上80℃未満の温度の純水または水溶液中に浸漬することによってシリコン酸化膜3に転換する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】制御ゲート電極膜のシリサイド膜を後工程で形成する際に、選択ゲートトランジスタの下部電極部のシリサイド化の進行を抑制できる装置及び製造方法の提供。

【解決手段】NANDフラッシュメモリ装置において、メモリセルトランジスタのゲート電極MGは、シリコン基板1上のゲート絶縁膜4を介して、浮遊ゲート電極部51、電極間絶縁膜6、制御ゲート電極部71を積層した構成である。制御ゲート電極部71は多結晶シリコン膜の成膜後にシリサイド化する。選択ゲートトランジスタのゲート電極SGは、下部電極部5、電極間絶縁膜6、中間電極部7、電極間絶縁膜8、上部電極部9が順次積層された構成である。多結晶シリコン膜からなる上部電極部9がシリサイド化される際、開口部6a、8aを介して中間電極部7および下部電極部5にシリサイド反応が進行するので、ゲート絶縁膜4に達する前にシリサイド反応の進行を停止できる。

(もっと読む)

341 - 360 / 725

[ Back to top ]