Fターム[5F101BH23]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | 多層配線技術 (77)

Fターム[5F101BH23]に分類される特許

1 - 20 / 77

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの制御性を向上した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、構造体と、複数の半導体層と、メモリ膜と、接続部材と、導電部材と、を備える。前記構造体は、メモリ領域と非メモリ領域とを有する基板の前記メモリ領域の上に設けられる。前記構造体は、前記基板の主面に対して垂直な第1軸に沿って積層され複数の電極膜を含む。前記半導体層は、前記構造体を前記第1軸に沿って貫通する。前記メモリ膜は、前記複数の電極膜と前記半導体層との間に設けられる。前記接続部材は、前記基板と前記半導体層との間に設けられる。前記接続部材は、隣り合う2つの前記半導体層のそれぞれの端部と接続される。前記導電部材は、前記基板と前記接続部材との間で、前記メモリ領域から前記非メモリ領域に延在して設けられる。前記導電部材は、前記非メモリ領域の上に設けられた凹部を有する。前記凹部内には、第1シリサイド部が設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】高品質な配線を有する半導体装置を提供する。

【解決手段】第1の領域100及び第2の領域200に設けられた第1の絶縁層10と、第1の領域に設けられた第1の絶縁層上に形成された第2の絶縁層11aと、第2の領域200に設けられた第1の絶縁層上に形成され、第2の絶縁層と略同一の高さを有する第3の絶縁層11cと、第1の領域に設けられた第1の絶縁層上及び第2の絶縁層の両方の側壁に形成された第1の配線層13aと、第2の領域に設けられた第1の絶縁層上、及び第3の絶縁層の上面及び側壁上に形成された第2の配線層13bと、第1の絶縁層、第2の絶縁層、第1の配線層、及び第2の配線層を覆う第4の絶縁層15と、第1の領域に設けられた第4の絶縁層内に形成され、第1の配線層に接続された第1のコンタクトプラグ17aと、第2の領域に設けられた第4の絶縁層内に形成され、第2の配線層に接続された第2のコンタクトプラグ17bと、を備える。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】生産性の高い不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施形態は、基板の主面に対して垂直な第1軸に沿って積層された複数の電極膜と、複数の電極膜を第1軸に沿って貫通する複数の半導体層と、複数の電極膜と半導体層との間に設けられたメモリ膜と、を含む不揮発性半導体記憶装置の製造方法であって、複数の電極膜となる複数の第1膜と複数の第2膜とを交互に積層して、第1積層体を形成する工程と、第1軸に沿い複数の第1膜を支持する支持部を形成する工程と、第1積層体を第1軸に沿って貫通する第1の孔を形成し、第1の孔を介して第2膜を除去し、複数の第1膜どうしの間に間隙が形成された第2積層体を形成する工程と、第2積層体の複数の第1膜を第1軸に沿って貫通する貫通孔を形成する工程と、複数の貫通孔の中に、メモリ膜及び半導体層を埋め込む工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の低抵抗化を図る。

【解決手段】本実施形態の半導体装置は、半導体基板10を覆う第1の層間絶縁膜上に設けられる配線60と、配線60の上面上に設けられるキャップ層68と、配線60と第2の層間絶縁膜との間に設けられるバリア膜62と、を含む。配線60は高融点導電層を含み、配線60の配線幅W1は、キャップ層68の幅W2よりも小さい。バリア膜62は、高融点導電層60が含む元素の化合物からなり、配線60を覆う層間絶縁膜69,70に起因する不純物が配線60内に拡散するのを抑制する。

(もっと読む)

半導体装置の製造方法及びコンピュータ記録媒体

【課題】効率良く多段の良好な形状の階段状の構造を形成することのできる半導体装置の製造方法及びコンピュータ記録媒体を提供する。

【解決手段】第1の誘電率の第1の膜と、第1の誘電率とは異なる第2の誘電率の第2の膜とが交互に積層された多層膜と、多層膜の上層に位置しエッチングマスクとして機能するフォトレジスト層とを有する基板をエッチングして、階段状の構造を形成する半導体装置の製造方法であって、フォトレジスト層をマスクとして第1の膜をプラズマエッチングする第1工程と、水素含有プラズマにフォトレジスト層を晒す第2工程と、フォトレジスト層をトリミングする第3工程と、第3工程によってトリミングしたフォトレジスト層及び第1工程でプラズマエッチングした第1の膜をマスクとして第2の膜をエッチングする第4工程とを有し、第1工程乃至第4工程を繰り返して行うことにより、多層膜を階段状の構造とする。

(もっと読む)

積層した接続レベルを有する集積回路装置用マスク数の低減法

【課題】3D積層メモリ装置は、各接続レベル毎に別個のマスクが使用されるので必要なマスク数は多くなるが、パターンを工夫して必要マスク数を減らす。

【解決手段】3次元積層集積回路装置は配線領域に接続レベルの積層部を有する。接続レベルの積層部で2のN乗個のレベルまで含む配線接続領域を形成するためのN個のエッチングマスクの組だけが必要とされる。幾つかの例によれば、2のX−1乗(2X−1)個の接続レベルは、連続番号Xのエッチングマスクでエッチングされ、1つのマスクがX=1であり、他の1つのマスクがX=2であり、X=Nまで付与される。当該方法は接続レベルでの形成領域に整合した配線接続領域を形成する。

(もっと読む)

半導体記憶装置及びその高電圧制御方法

【課題】チャージポンプ等の高電圧生成部の回路面積を削減する。

【解決手段】半導体記憶装置は、ワードライン及びビットラインが接続されマトリクス状に配置された複数のメモリセル21と、ワードラインを駆動する複数のワードラインドライバ23a及び23b、電源電圧を昇圧して高電圧を生成するチャージポンプ11と、複数のメモリセル21のうちアクセスに関係のある箇所には高電圧が印加され、アクセスに関係のない箇所には電源電圧が印加されるように制御するX方向高電圧制御回路31及びY方向高電圧制御回路32とを備える。

(もっと読む)

半導体装置の製造方法

【課題】フローティングゲートへの帯電電荷を、別途工程を追加することなく除去できる半導体装置の製造方法を提供する。

【解決手段】半導体基板10の一主面11に少なくともフローティングゲート25を含む電極層22を形成し、電極層22上に層間絶縁膜40を形成し、層間絶縁膜に電極層22を露出するビアホール42と、半導体基板の一主面を露出するビアホール48を形成し、ビアホール42を介して電極層22と電気的に接続され、ビアホール48を介して半導体基板10と電気的に接続される配線層60を形成し、配線層60をパターニングして少なくとも電極層22のみに接続されている配線62を形成する。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】1つの実施形態は、絶縁膜に形成された溝に導電物質を容易に埋め込むことができる半導体装置の製造方法、及びそのような製造方法に適した半導体装置を提供する。

【解決手段】1つの実施形態によれば、コンタクトプラグを形成し、コンタクトプラグを覆うエッチングストッパー膜を形成し、エッチングストッパー膜を覆う絶縁膜を形成し、絶縁膜及びエッチングストッパー膜にコンタクトプラグの表面を露出する溝を形成し、エッチングストッパー膜のエッチングレートに対し絶縁膜のエッチングレートの方が高くなる条件で、コンタクトプラグとコンタクトプラグの周辺とを含む領域を選択的にエッチバックし、エッチバックを行った後に溝に導電物質を埋め込んでラインパターンを形成する。

(もっと読む)

ストリング選択線及びビット線の改善されたコンタクトレイアウトを有する3次元メモリアレイ

【課題】インターコネクト及びコンタクト用の実装面積が小さい3次元集積回路メモリ用の構造を低製造コストで提供する。

【解決手段】3次元メモリデバイスは、絶縁材料21,22,23,24で分離され、復号化回路を介してセンスアンプに結合可能なビット線BLnとして導電材料の複数の帯片の形状をしている。導電材料帯片11,12,13,14は、スタック横面に側面を有する。ワード線WLn,WLn+1の複数の導電線16,17は行デコーダに結合でき、複数のスタック上で直交して延びる。導電線は、スタックの表面に共形である。記憶素子は、スタック上の半導体材料帯片の側面と導電線の間の交点の界面領域の多層アレイに設けられる。3次元メモリは、複数層に対する2つの最小線幅のマスクで作られる。半導体材料帯片の端部に階段構造が含まれる。半導体材料帯片に平行な金属層上と、ワード線に平行な上部金属層上にSSLインターコネクトを含む。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多層配線構造を使って、キャパシタンスが大きく、かつキャパシタンス値が安定なキャパシタ素子を半導体基板上に集積化する。

【解決手段】多層配線構造18は、少なくとも第1層目の層間絶縁膜16と、第1層目の層間絶縁膜中に埋設された第1配線層と、を含み、第1配線層は、第1の電源に接続され前記第1の層間絶縁膜中に埋設された第1の配線パタ―ン15C1と、第2の電源に接続され前記第1の層間絶縁膜中に埋設された第2の配線パタ―ン15C2と、を含み、第1の配線パタ―ンと前記第2の配線パタ―ンとは容量結合して第1のキャパシタを形成し、第1の配線パタ―ンは積層配線パタ―ン13C上に形成されて、前記第4の電極パターン13Gと容量結合して第2のキャパシタを形成し、第4の電極パターンは第2の配線パタ―ンに電気的に接続されている。

(もっと読む)

階段型構造の形成方法及びこれを利用した不揮発性メモリー素子の製造方法

【課題】本発明は、不揮発性メモリー素子の製造方法を提供し、不揮発性メモリー素子において階段形態のゲートを具現できるパターニング方法を提供する。

【解決手段】本発明は階段型構造を形成する方法及びこれを利用した不揮発性メモリー素子の製造方法に関し、複数個の薄膜をプレート形状に積層し、前記複数個の薄膜のうち最上層の薄膜上にマスクを形成し、前記マスクを利用したエッチングを使用して前記最上層の薄膜をパターニングし、前記マスクを順次的に拡大し、そして前記順次的拡大されたマスクを利用したエッチングを使用して余り薄膜を順次的にパターニングすることを含み、前記複数個の薄膜を前記プレート形状から階段形態に形成するパターニング方法を利用して階段型構造を有するコントロールゲートを含む不揮発性メモリー素子を製造できる。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】安定した動作を実行可能な不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】メモリストリングMSは、メモリ柱状半導体層36と、メモリ柱状半導体層36の側面を取り囲むように形成された電荷蓄積層を含むメモリゲート絶縁層35と、メモリゲート絶縁層35を取り囲むように形成された4層のワード線導電層31a〜31dと、ワード線導電層31a〜31dの上部を保護する2層の保護層33a、33bとを備える。ワード線導電層31a〜31dは、その端部の位置が異なるように階段状に形成された階段部STを構成する。下から2段目のステップST2は、その上面を2層の保護層33a、33bにて覆われ、下から1段目のステップST1は、その上面を1層の保護層33aにて覆われている。

(もっと読む)

不揮発性半導体記憶装置

【課題】複数の絶縁膜及び電極膜が交互に積層された信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置において、メモリアレイ領域にメモリ積層体を設け、周辺回路領域にダミー積層体を設け、ダミー積層体にダミーホール31a,31bを形成し、その内部に絶縁部材を埋め込む。そして、絶縁部材内に複数本のコンタクト35a,35b,35c,35d,35eを形成する。コンタクト35a,35bはMOSFET40のソース層36に、コンタクト35c,35dはドレイン層37に、コンタクト35eはゲート電極38に接続される。そして、1つのダミーホール内に配置された複数本のコンタクトは、同じ電位が印加されるコンタクトとするか、ダミーホールの長手方向に延びる中心線41a,41c、41d、41f、41h、41j、41k、41lから外れた位置に配置する。

(もっと読む)

半導体装置及びその製造方法

【課題】深さの異なる複数のコンタクトホールの底部径のばらつきを抑制する半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、複数の導電層WL1〜WL4が階段状に加工された階段構造部を有する積層体と、階段構造部を覆って設けられた層間絶縁層43と、層間絶縁層43を貫通し、それぞれが対応する各段の導電層WL1〜WL4に達して形成された複数のコンタクトホール61〜64の内部に設けられたコンタクト電極60とを備え、複数のコンタクトホール61〜64の底部の孔径は略同じであり、下段側の導電層に達するコンタクトホールは、上段側の導電層に達するコンタクトホールよりも深く、上端部の孔径が大きい。

(もっと読む)

不揮発性半導体記憶装置

【課題】正確な読み出しを実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリトランジスタMTr1〜8が直列に接続された複数のメモリストリングMSと、メモリストリングMSの一端に一端を接続されたドレイン選択トランジスタSDTrと、複数のドレイン側選択トランジスタSDTrの他端に共通接続されたローカルビット線LBLと、ローカルビット線LBLに一端を接続されたスイッチ回路SWと、複数のスイッチ回路SWの他端に共通接続されたグローバルビット線GBLとを備える。メモリストリングMSは、柱状部を含むU字状半導体層と、柱状部の側面を取り囲むように形成された電荷蓄積層と、電荷蓄積層を取り囲むように形成されたワード線導電層とを備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリホールの直径が均一な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】シリコン基板10上にバックゲート電極13を形成し、バックゲート電極13の上面に凹部23を形成し、凹部23内に犠牲材を埋め込んだ後、絶縁膜14及び電極膜15を交互に積層して積層体11を形成する。次に、積層体11の中央部21にメモリホール24を形成し、その後、酸化処理を施す。これにより、メモリホール24の内面を起点として、電極膜15における絶縁膜14に接する部分が酸化され、その結果、中央部21において電極膜15が薄くなり、絶縁膜14が厚くなる。次に、積層体11の端部22において、電極膜15毎にステップ30を形成し、端部22を埋め込むように層間絶縁膜40を形成し、層間絶縁膜40中にステップ30に到達するようにプラグホール41を形成する。

(もっと読む)

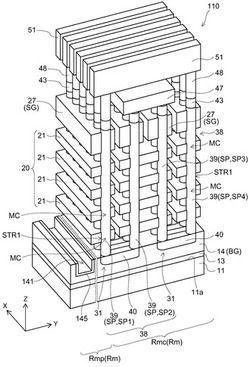

不揮発性半導体記憶装置及びその製造方法

【課題】回路部の上部にメモリ部を形成し、回路部が高温にさらされても回路部の配線層やコンタクトが劣化しない不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板11と、メモリ部MUと、半導体基板とメモリ部との間の回路部CUと、を備える。メモリ部は、半導体基板の主面11aに垂直な第1方向に交互に積層された複数の電極膜WLと複数の絶縁膜14とを有する積層構造体MLと、積層構造体を第1方向に貫通する半導体ピラーSPと、電極膜と半導体ピラーとの交差部に対応して設けられた記憶部43と、を有す。回路部は、それぞれ第1、第2導電型のソース/ドレイン領域を有する第1、第2トランジスタ51n、51pと、シリサイドを含む第1配線W1と、ソース/ドレイン領域と同じ導電型のポリシリコンからなるコンタクトプラグC1、C2と、を有す。

(もっと読む)

積層メモリ素子

【課題】高集積化が容易な積層メモリ素子を提供する。

【解決手段】本願発明の積層メモリ素子は、基板と、基板上に互いに積層された、少なくとも1層のメモリ層をそれぞれ含む複数のメモリグループと、該複数のメモリグループのうち、複数の隣接した2つのメモリグループ間に介在する複数のXデコーダ層と、前記複数の隣接した2つのメモリグループ間に、複数のXデコーダ層と交互に介在される複数のYデコーダ層と、を具備する積層メモリ素子である。

(もっと読む)

不揮発性半導体メモリ装置の消去方法

【課題】保持特性に優れた不揮発性半導体メモリ装置の消去方法を提供することである。

【解決手段】ソース・ドレイン領域2、3が離間して形成された半導体基板1と、半導体基板1上に形成された第1の絶縁層7と、第1の絶縁層7上の第1の領域10に形成された第1のゲート電極5と、第1の絶縁層7上の第2の領域11、12に形成された電荷蓄積層8と、電荷蓄積層8上に形成された第2の絶縁層9と、第2の絶縁層9上に形成された第2のゲート電極4、6と、を有する不揮発性半導体メモリ装置の消去方法は次のステップを有する。ソース・ドレイン領域から電荷蓄積層にホットホールを注入するステップ。電荷蓄積層の第1のゲート電極側の領域にチャネルホットエレクトロンを注入するステップ。

(もっと読む)

1 - 20 / 77

[ Back to top ]