Fターム[5F102GC07]の内容

接合型電界効果トランジスタ (42,929) | ゲート配置 (2,808) | 縦型FETの表面ゲート (111)

Fターム[5F102GC07]に分類される特許

1 - 20 / 111

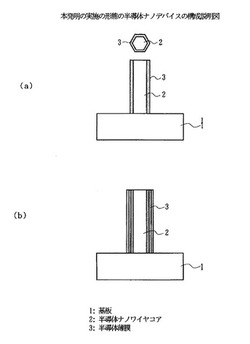

半導体ナノデバイス

【課題】 半導体ナノデバイスに関し、基板上における臨界膜厚を超えた厚さの歪のある半導体薄膜を形成してデバイス領域とする。

【解決手段】 長径が1μm未満の半導体ナノワイヤコアと、前記半導体ナノワイヤコアの側壁に形成され、前記半導体ナノワイヤコアの構成材料との歪εが1%以上異なる半導体材料からなり、且つ、膜厚t〔nm〕と歪ε〔%〕とが、

−0.720+0.0988ε−1.2<t≦−0.705+0.227ε−1.2

の関係を満たす少なくとも一層の半導体薄膜との接合界面或いは前記半導体薄膜同士の接合界面を機能領域とする。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】GaNを用いた窒化物半導体装置において、電流が流れる経路に、再結晶成長などによる界面が存在することがない状態で、十分な耐圧が得られるようにする。

【解決手段】GaNからなるチャネル層(第2半導体層)101と、チャネル層101の一方の面であるN極性面に形成された第1障壁層(第1半導体層)102と、チャネル層101の他方の面であるIII族極性面に形成された第2障壁層(第3半導体層)103とを備える。第1障壁層102および第2障壁層103は、例えば、AlGaNから構成されている。また、ドレイン電極(第1電極)104が、第1障壁層102の上に形成され、ゲート電極105が、ドレイン電極104に対向して第2障壁層103の上に形成されている。ソース電極(第2電極)106は、ゲート電極105と離間して第2障壁層103の上に形成されている。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】GaNを用いた縦型の電界効果トランジスタにおいて、素子の作製にコストの上昇を招くことなく、ドレイン電流密度を大きくできるようにする。

【解決手段】GaNからなるチャネル層101と、GaNより大きなバンドギャップエネルギーを有してアルミニウムを含む窒化物半導体から構成されてチャネル層101の一方の面に形成された障壁層102を備える。ここで、チャネル層101の一方の面は、N極性面とされ、他方の面はIII族極性面とされていればよい。また、チャネル層101の他方の面に形成されたドレイン電極103と、ドレイン電極103に対向して障壁層102の上に形成されたゲート電極104と、ゲート電極104と離間して障壁層102の上に形成されたソース電極105とを備える。

(もっと読む)

窒化物電子デバイス、窒化物電子デバイスを作製する方法

【課題】リーク特性のばらつき幅を低減可能な、窒化物電子デバイスを作製する方法を提供する。

【解決手段】テトラメチルアンモニウムヒドロキシドを含む第1溶液を用いた処理を行って半導体積層53bに第1処理面65fを処理装置10dで形成する。第1溶液による処理温度は、摂氏50度以上摂氏100度以下である。第1溶液の濃度は5パーセント以上であり、50パーセント以下である。第1処理工程に引き続き第2処理工程を行う。第2処理工程では、テトラメチルアンモニウムヒドロキシド処理の後に、フッ化水素酸及び過酸化水素を含む第2溶液を用いた処理を半導体積層53bに行って半導体積層53bに第2処理面65gを処理装置10eで形成する。第2処理工程の後において、半導体積層53bの処理面65gのドナー性不純物の濃度は5×1017cm−3以下である。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】高濃度接合リークが発生することを抑制する。

【解決手段】第2ゲート領域8が備えられるトレンチ6の先端部においてJFET構造が形成されないように凹部13を形成する構造において、凹部13の底面と側面との境界部となるコーナ部にp型層16を形成するようにする。これにより、p型層16とp+型の第1ゲート領域3もしくは第2ゲート領域8とが同じ導電型となり、これらの間において高濃度接合が構成されないようにできる。したがって、ドレイン電位が第1ゲート領域3上に表出して、ゲート−ドレイン間耐圧を低下させてしまうことを防止でき、高濃度接合リーク(ゲートリークやドレインリーク)が発生することを防止することができる。

(もっと読む)

パワーモジュールおよび電力変換回路

【課題】電力変換回路の性能を高める。

【解決手段】ユニット10は、半導体スイッチ素子1,2と、ダイオード3,4とを備える。ダイオード3は、半導体スイッチ素子2がオン状態である時に逆バイアスされ、半導体スイッチ素子2がオフ状態である時に導通する。ダイオード4は、半導体スイッチ素子1がオン状態である時に逆バイアスされ、半導体スイッチ素子1がオフ状態である時に導通する。ダイオード3,4は、窒化ガリウム(GaN)ダイオードまたはダイヤモンドダイオードである。ユニット10を備えるパワーモジュールは、コンバータ、インバータ等の電力変換回路に適用される。

(もっと読む)

半導体装置及びその駆動方法

【課題】順方向電圧降下の平均値を低減し、整流素子の低損失化を実現する半導体装置とその駆動方法を提供する。

【解決手段】アノード電極9とカソード電極3との間に、p型層7と、i層1と、n型層2とを順に形成したダイオード構造の半導体装置において、アノード電極9側に、p型層7と並列に第2n型層8を形成し、順方向バイアス中に、アノード電極9側をp型層7と第2n型層8のいずれかに切り替えるゲート駆動回路10を備えた半導体装置。ゲート電極5は、p型層7と第2p型層6と第2n型層8に接するトレンチ構造4とし、トレンチ内部に絶縁膜4aと電極とを備えたものとすることができる。このゲート電極5は、ゲート駆動回路10から印加するゲート電圧に応じてp型及びn型のチャネルをトレンチ表面に形成する。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】窒化物半導体を用いたノーマリーオフ動作の電界効果型トランジスタにおいて、閾値電圧が制御でき、十分な素子特性が得られるようにする。

【解決手段】c軸方向に結晶成長された窒化物半導体から構成されて主表面が極性面とされた第1領域121,第1領域121より厚く形成された第2領域122,および、第1領域121と第2領域122との間に形成されて主表面が半極性面とされた第3領域123を備える半導体層101を備える。また、窒化物半導体装置は、第1領域121における半導体層101の上に形成されたドレイン電極102と、第2領域122における半導体層101の上に形成されたソース電極103と、第3領域123における半導体層101の上に形成されたゲート電極104とを備える。

(もっと読む)

窒化物半導体素子の製造方法

【課題】ドレインリーク電流を低減することが可能な窒化物半導体素子の製造方法を提供する。

【解決手段】ヘテロ電界効果トランジスタ1の製造方法は、ドリフト層20aを支持基板10上にエピタキシャル成長させる工程と、水素ガスをキャリアガスとして用いて、p型半導体層である電流ブロック層20bをドリフト層20a上に1000℃以上でエピタキシャル成長させる工程と、窒素ガス、アルゴンガス、ヘリウムガス及びネオンガスからなる群より選ばれる少なくとも一種のガスをキャリアガスとして用いて、コンタクト層20cを電流ブロック層20b上にエピタキシャル成長させる工程と、を備える。

(もっと読む)

半導体装置

【課題】 オン抵抗の増大を抑制しつつ、耐圧の低下を抑制する技術を提供する。

【解決手段】 ノーマリオフ型の半導体装置100は、ヘテロ接合を構成する半導体層16と、第1リセス部8と、第1リセス部8よりも浅い第2リセス部4と、ゲート部5を備えている。半導体層16は、第1半導体層12と、第1半導体層12上に設けられているとともに第1半導体層12よりもバンドギャップが広い第2半導体層14を有している。第2リセス部4は、第2半導体層14を貫通していない。第2リセス部4の下方に位置する第2チャネル部C2は、第1リセス部8の下方に位置する第1チャネル部C1よりも電流経路20の上流側に配置されている上流側第2チャネル部C2uを有する。

(もっと読む)

p型のIII族窒化物半導体層を含む半導体装置とその製造方法

【課題】p型のIII族窒化物半導体層を含む積層構造を利用して複数個の半導体装置を製造し、エッチング等して個々の半導体装置に分割すると、個々の半導体装置の側面に露出するp型のIII族窒化物半導体層の表面に沿ってリ−ク電流が流れてしまう。

【解決手段】p型のIII族窒化物半導体層8を含む積層構造の表面または裏面からp型のIII族窒化物半導体層8に達しない深さまでエッチングまたはダイシングし、残った厚みをへき開して個々の半導体装置に分割する。半導体装置の側面に露出するp型のIII族窒化物半導体層8の表面はへき開面となり、結晶欠陥が少なく、側面に沿ってリ−ク電流が流れることを防止する。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制する。

【解決手段】トレンチ6の先端部に形成されたn-型チャネル層7がトレンチ6の長辺に位置する部分よりも膜厚が厚くなるため、そのトレンチ6の先端部においてJFET構造が構成されないようにする。例えば、トレンチ6の先端部をp+型領域20にて埋め尽くすようにする。これにより、トレンチ6の先端部のJFET構造の閾値がトレンチ6の長辺に位置する部分のJFET構造の閾値からずれることによる影響を受けることがない。したがって、ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制できる構造のSiC半導体装置とすることが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度を得ながら、かつ、縦方向耐圧およびゲート電極端における耐圧の両方の耐圧性能を確実に得ることができる、半導体装置およびその製造方法を提供する。

【解決手段】 n型ドリフト層および該n型ドリフト層上に位置するp型層を含むGaN系積層体に、開口部が設けられ、開口部を覆うように位置する、チャネルを含む再成長層と、再成長層に沿って該再成長層上に位置するゲート電極とを備え、開口部はn型ドリフト層に届いており、ゲート電極の端は、平面的に見てp型層から外れた部分がないように位置していることを特徴とする。

(もっと読む)

ブール成長された炭化ケイ素ドリフト層を使用してパワー半導体デバイスを形成する方法、およびそれによって形成されるパワー半導体デバイス

【課題】炭化ケイ素の好ましい電気特性にもかかわらず、その中においてより厚い電圧サポート領域を有する炭化ケイ素パワーデバイスの必要性が引き続き存在している。

【解決手段】高電圧炭化ケイ素パワーデバイスを形成する方法は、法外に高いコストのエピタキシャル成長された炭化ケイ素層の代わりに、高純度炭化ケイ素ウエハ材料から得られる高純度炭化ケイ素ドリフト層を利用している。本方法は、約100μmより厚い厚みを有するドリフト層を使用して10kVを超えるブロッキング電圧をサポートすることができる少数キャリアパワーデバイスと多数キャリアパワーデバイスの両方を形成することを含んでいる。これらのドリフト層は、その中に約2×1015cm−3未満である正味n型ドーパント濃度を有するブール成長炭化ケイ素ドリフト層として形成される。このn型ドーパント濃度は、中性子変換ドーピング(NTD)技法を使用して実現することができる。

(もっと読む)

半導体素子およびその製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

III族窒化物半導体装置

【課題】p型III族窒化物半導体62の上面からn型III族窒化物半導体64に到達する溝が形成されている場合、p型III族窒化物半導体の側面62aが露出する。p型III族窒化物半導体の露出面62aはn型化しやすく、露出面に沿ってリーク電流が流れやすい。

【解決手段】p型III族窒化物半導体62中に存在する正孔を露出面62aに誘導する正孔誘導手段を設ける。例えば、露出面62aを被覆する絶縁膜66に負電荷蓄積領域68を設ける。負電荷蓄積領域68が、p型III族窒化物半導体中に存在する正孔を露出面62aに誘導し、露出面がn型化して露出面に沿ってリーク電流が流れることを防止する。

(もっと読む)

半導体装置およびその製造方法

【課題】 開口部が設けられ、当該開口部に二次元電子ガスで形成されるチャネルを備える縦型半導体装置の耐圧性能を向上させることを目的とする。

【解決手段】 GaN系積層体15は、n−型GaNドリフト層4/p型GaNバリア層6/n+型GaNコンタクト層7、を有し、開口部28は表層からn−型GaNドリフト層4内にまで届いていて、開口部の壁面および底部を覆うように位置する、電子走行層22および電子供給層26を含む再成長層27と、開口部の周囲に位置するソース電極Sと、開口部の再成長層上に位置するゲート電極Gと、開口部の底部に位置する底部絶縁膜37とを備えることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】開口部にチャネルを備える縦型半導体装置において、高周波特性を向上することができる半導体装置およびその製造方法を提供する。

【解決手段】 n型GaN系ドリフト層4/p型GaN系バリア層6/n型GaN系コンタクト層7、を有し、開口部28は表層からn型GaN系ドリフト層内にまで届いており、該開口部を覆うように位置する電子走行層22および電子供給層26を含む再成長層27と、ソース電極Sと、ドレイン電極Dと、再成長層上に位置するゲート電極Gとを備え、ソース電極を一方の電極とし、またドレイン電極を他方の電極としてコンデンサを構成するとみて、該コンデンサの容量を低下させる容量低下構造を備えることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 開口部が設けられ、当該開口部に二次元電子ガスで形成されるチャネルを備える縦型半導体装置の耐圧性能を向上させることを目的とする。

【解決手段】開口部28が設けられたGaN系積層体15を備える縦型の半導体装置であって、n型GaN系ドリフト層4/p型GaN系バリア層6/n型GaN系コンタクト層7、を備え、開口部を覆うように電子走行層22および電子供給層26を含む再成長層27と、ソース電極Sと、再成長層上に位置するゲート電極Gとを備え、ゲート電極Gは、p型GaNバリア層の厚み範囲に対応する部分を覆い、かつ開口部の底部から離れた位置の壁面内で終端している。

(もっと読む)

1 - 20 / 111

[ Back to top ]