Fターム[5F102GL20]の内容

接合型電界効果トランジスタ (42,929) | チャネル層(主電流が流れる半導体層) (3,041) | δ(デルタ)ドープ、プレーナ・ドープ (38)

Fターム[5F102GL20]に分類される特許

1 - 20 / 38

トランジスタ用エピタキシャルウェハの製造方法

【課題】成長時間を短縮してスループットを向上することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】基板2上に、電子供給層6,10及びチャネル層8を有する高電子移動度トランジスタ構造層3を形成する工程と、高電子移動度トランジスタ構造層3上に、コレクタ層14、ベース層15、エミッタ層16及びノンアロイ層18を有するヘテロバイポーラトランジスタ構造層4を形成する工程と、を有するトランジスタ用エピタキシャルウェハの製造方法において、ヘテロバイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下で、かつ、一定の成長温度で成長するようにした。

(もっと読む)

III−V族化合物半導体エピタキシャルウエハ

【課題】充分な選択比を備え、また、除去が比較的容易なエッチングストッパ層を得る。

【解決手段】GaAs基板10上に設けられた高電子移動度トランジスタ構造20と、高電子移動度トランジスタ構造20の上に設けられたヘテロ接合バイポーラトランジスタ構造40と、を備え、高電子移動度トランジスタ構造20とヘテロ接合バイポーラトランジスタ構造40との間には、As濃度が1.0×1016atoms/cc以上1.0×1021atoms/cc以下のInGaAsP層からなるエッチングストッパ層30を備える。

(もっと読む)

III−V族化合物半導体エピタキシャルウェハ

【課題】オン抵抗の低いストッパー層を有するIII−V族化合物半導体エピタキシャルウェハを提供する。

【解決手段】単結晶基板8上に、GaAs層、AlGaAs層からなるバッファ層9、n型不純物を含有するAlGaAs層又はInGaP層若しくはSiプレナードープ層からなる電子供給層10、InGaAs層からなるチャネル層12、ノンドープ又は低濃度n型不純物を含有するGaAs層又はAlGaAs層からなるショットキー層14、ノンドープ又は低濃度n型不純物を含有するInGaP層からなるストッパー層15、n型不純物を含有するGaAs層からなるキャップ層16を積層したHEMT構造18を有するIII−V族化合物半導体エピタキシャルウェハ17において、ストッパー層15におけるInGaP中のAsが占めるV族原子分率が15%以下であるものである。

(もっと読む)

化合物半導体装置

【課題】プレーナドープの高性能性を保持したまま特性変動を抑制できる化合物半導体装置を提供する。

【解決手段】化合物半導体からなるHEMT構造の化合物半導体装置において、チャネル層へ電子を供給する電子供給層14,16,18が、n型不純物のプレーナドープ層で形成されており、同一の電子供給層におけるプレーナドープ層15,17が2分割以上に分割されている。

(もっと読む)

III−V族化合物半導体エピタキシャルウェハ及びその製造方法

【課題】オン抵抗やリーク電流を低減したIII−V族化合物半導体エピタキシャルウェハを提供する。

【解決手段】単結晶基板上に、少なくとも、GaAs層、AlGaAs層からなるバッファ層、InGaAs層からなるチャネル層、n型不純物を含有するAlGaAs層又はInGaP層若しくはSiプレナードープ層からなる電子供給層、ノンドープ又は低濃度n型不純物を含有するAlGaAs層からなるショットキー層、Se又はTeをドーパントとしたn型不純物を含有するInxGa(1-x)As層(但し0<x<1)からなるコンタクト層を積層したHEMT構造を有するIII−V族化合物半導体エピタキシャルウェハにおいて、その表面清浄度検査におけるHaze値が500ppm以下であるものである。

(もっと読む)

化合物半導体エピタキシャルウェハの製造方法と、トランジスタ用エピタキシャルウェハ

【課題】基板面内のコンタクト抵抗を低く抑えることを可能とした化合物半導体エピタキシャルウェハの製造方法と、トランジスタ用エピタキシャルウェハを提供する。

【解決手段】基板1上に有機金属原料化学気相成長法で化合物半導体層を形成する気相エピタキシャル成長装置10によってn型不純物がドーピングされたn型コンタクト層を成長させる際に、原料ガスが供給される上流側に設けられた第1ヒータ16のヒータ温度を500℃以上とし、第1ヒータ16より下流側に設けられた他のヒータ17,18のヒータ温度を第1ヒータ16のヒータ温度よりも低く、かつ、350℃以上500℃以下に調整する。

(もっと読む)

III−V族化合物半導体エピタキシャルウェハ及びその製造方法

【課題】コンタクト層に不純物として供給するTe、Seのメモリーの影響を小さくしつつ、コンタクト抵抗を低減し、かつ、特性変動や信頼性低下を抑制しつつ、電子供給層の不純物濃度を高め、オン抵抗を低減したIII−V族化合物半導体エピタキシャルウェハを提供する。

【解決手段】単結晶基板11上に、GaAs層、AlGaAs層からなるバッファ層12a,12b、n型不純物を含有するAlGaAs層13,17又はInGaP層若しくはSiプレナードープ層からなる電子供給層、InxGa(1-x)As層からなるチャネル層15、アンドープ又は低濃度n型不純物を含有するAlGaAs層からなるショットキー層18、n型不純物を含有するInxGa(1-x)As層からなるコンタクト層20a、20bを積層したHEMT構造を有し、チャネル層のxを0.3≦x≦0.35とし、コンタクト層のxを0.55≦x≦0.60としたものである。

(もっと読む)

電界効果トランジスタ

【課題】チャネル層をInAsから構成するヘテロ構造の電界効果トランジスタで、高速で安定した動作ができるようにする。

【解決手段】第1障壁層102に形成されてAlGaSbに対して浅いアクセプタとなる不純物が導入された第1不純物導入領域110と、第2障壁層104に形成されてAlGaSbに対して浅いアクセプタとなる不純物が導入された第2不純物導入領域111とを備える。また、第1不純物導入領域110および第2不純物導入領域111は、チャネル層103の電子に不純物散乱を生じさせない範囲でチャネル層103より離間して形成されている。

(もっと読む)

化合物半導体エピタキシャルウエハ及び高周波半導体装置

【課題】HEMTのチャンネル抵抗を小さくできる構造を有する化合物半導体エピタキシャルウエハ及び高周波半導体装置を提供する。

【解決手段】半絶縁性半導体基板10と、結晶成長性を良好にするためのバッファ層11と、一様にドープされた領域内にデルタドープされた領域を有する第1の電子供給層12と、電子のポテンシャル障壁を形成する第1のスペーサ層13と、2次元電子を発生させるチャネル層14と、電子のポテンシャル障壁を形成する第2のスペーサ層15と、一様にドープされた領域内にデルタドープされた領域を有する第2の電子供給層16と、オーミックコンタクトをとるためのキャップ層17と、を順次積層して形成してなることを特徴とする。

(もっと読む)

トランジスタ素子

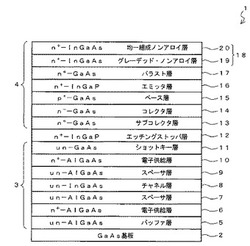

【課題】GaAs基板上にHEMT、HBTを順次積層してなるトランジスタ素子において、HEMTの移動度の低下を抑制することが可能なトランジスタ素子を提供する。

【解決手段】GaAs基板2上に高電子移動度トランジスタ(HEMT)3が形成され、HEMT3上にヘテロバイポーラトランジスタ(HBT)4が形成されたトランジスタ素子において、HEMT3がアンドープInGaAsPからなるバリア層10を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】トランジスタ中の電子移動度を向上させる上、デバイスの性能を向上させる高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタは、基板110と、基板110上に形成したバッファ層120と、複数のInGaAs薄膜と複数のInAs薄膜とを交互に積層して形成した超格子構造を含み、バッファ層120上に形成したチャネル層130と、チャネル層130上に形成したスペーサ層140と、スペーサ層140上に形成したショットキー層160と、ショットキー層160上に形成したキャップ層170とを備える。

(もっと読む)

高電子移動度トランジスタの構造、その構造を含んだデバイス及びその製造方法

【課題】MMICのSPDTスイッチなど、半導体デバイスとして用いるのに適したMOS−PHEMTの構造及びその製造方法を開示する。

【解決手段】MOS−PHEMT構造は、Al2O3、HfO2、La2O3及びZrO2からなる群から選ばれる材料からなるゲート誘電体層107を有することを特徴とし、これにより、このMOS−PHEMTの構造を含む、高周波スイッチデバイスなどの半導体構造が、直流電流の損失及び挿入損失の低下を防ぎ、隔絶性を向上させることができる。

(もっと読む)

電界効果トランジスタ、および、その製造方法

【課題】従来よりもゲート寸法が縮小され、高周波性能の高い電界効果トランジスタを、均一なゲート寸法でかつ低コストで提供すること。

【解決手段】ゲート電極を形成するための開口部を設ける工程において、投影露光装置を用いて、レジストを露光して前記開口部を作成する際に、露光されるレジストにおいて、該露光により形成される半導体基板上での開口部の幅が、レチクルおよび露光装置の縮小比によって規定されるウエハー上での光束寸法よりも小さな幅として形成されるように、ソース電極およびドレイン電極の厚さを、それぞれ所定の値に設定する。

(もっと読む)

p型半導体デバイス

半導体デバイスが、第1の閉じ込め層(32)上に活性層(31)を備える。活性層(31)は厚さ20nm未満のα−Sn層を備える。第1の閉じ込め層(32)は、α−Snより広いバンドギャップの材料から形成され、α−Snとこの材料間のバンドギャップオフセットは活性層への電荷キャリアの閉じ込めを可能にし、活性層は量子井戸として作用する。類似の第2の閉じ込め層(34)が活性層(31)上に形成されてもよい。半導体デバイスはp−FETであってもよい。このような半導体デバイスの製造方法もまた説明されている。  (もっと読む)

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】電極の接触抵抗の低減を図るようにした高周波特性の良い電界効果トランジスタ及びその製造方法を提供すること。

【解決手段】III−V族化合物半導体薄膜をエピタキシャル結晶成長させてなる多層膜半導体構造を有しており、多層膜半導体構造は、基板1と、基板1上に形成されたバッファ層2と、バッファ層2上に形成された電子走行層3と、電子走行層3上に形成されたスペーサ層4と、スペーサ層4上に形成された電子供給層5と、電子供給層5上に形成されたバリア層6と、バリア層6上に形成された高電子濃度キャップ層7とを備え、さらに、高電子濃度キャップ層7上に形成されたソース電極101及びドレイン電極103と、バリア層6の表面に形成されたゲート電極102とを備えている。

(もっと読む)

量子井戸デバイスにおける平行伝導を改善する装置及び方法

平行伝導を改善する量子井戸デバイスを提供する方法及び装置の実施形態が主に記載される。その他の実施形態についても、記載及び特許請求される。 (もっと読む)

小型化可能な量子井戸デバイスおよびその製造方法

【課題】小型化可能な、量子井戸デバイスおよびその製造方法を提供する。

【解決手段】量子井戸QWデバイスは、基板1を覆う量子井戸領域QW、量子井戸領域の一部を覆うゲート領域G、ゲート領域に隣接するソース領域Sおよびドレイン領域Dを含む。量子井戸領域は、第1バンドギャップを有する半導体材料を含むバッファ構造2と、バッファ構造2を覆い、第2バンドギャップを有する半導体材料を含むチャネル構造3と、チャネル構造3と接する第3バンドギャップを有するアンドープの半導体材料を含むバリア構造4とを含み、第1バンドギャップと第3バンドギャップは、第2バンドギャップより広い。ソース領域Sとドレイン領域Dは、それぞれゲート領域Gに対してセルフアラインであり、第4バンドギャップを有する半導体材料を含み、第4バンドギャップは第2バンドギャップより広い。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極の周囲に形成される空洞と保護膜に形成されるホールとの境界部分の開口を封止しやすい構造を実現する。

【解決手段】半導体装置を、ゲート電極3と、高さが低い部分6Aと高さが高い部分6Bとを有する階段状の空間6をゲート電極3の周囲に有する保護膜4と、高さが低い部分6Aに接するように保護膜4に形成されたホール5とを備えるものとする。

(もっと読む)

化合物半導体装置とその製造方法

【課題】絶縁膜をマスクとしてキャップ層をリセスエッチングするが、庇状絶縁膜は残らない化合物半導体装置とその製造方法を提供する。

【解決手段】ソース電極、ドレイン電極を覆って、キャップ層上に形成した第1の絶縁膜上に電子線レジスト層を形成し、リセス形成用開口を高ドーズ量で、庇除去用開口を低ドーズ量で、電子線露光し、低溶解度現像液で現像してリセス形成用開口を形成し、キャップ層を選択的にウェットエッチングして、リセス形成用開口より幅広のリセスRCを形成する。露出している第1の絶縁膜をエッチングして庇を消滅させた後、第1の絶縁膜を覆って、露出した半導体表面上に第2の絶縁膜を形成し、第2の絶縁膜の上にゲート電極用開口を有するレジストパターンを形成し、第2の絶縁膜をエッチングし、ゲート電極形成用金属層を形成し、リフトオフしてゲート電極を形成する。

(もっと読む)

1 - 20 / 38

[ Back to top ]