Fターム[5F102GR06]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 半導体基体内に付加領域を設けたもの (876)

Fターム[5F102GR06]の下位に属するFターム

不純物領域 (317)

絶縁領域(高抵抗領域を含む) (273)

エッチングストッパとなる層 (162)

Fターム[5F102GR06]に分類される特許

61 - 80 / 124

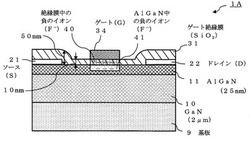

窒化物系半導体電界効果トランジスタ

【課題】ノーマリオフ動作を達成し、十分なチャネル電流が得られ、かつ、しきい値電圧制御が容易な窒化物系半導体ヘテロ接合電界効果トランジスタを提供する。

【解決手段】GaN層10とAlGaN層11のヘテロ接合界面をチャネルとする電界効果トランジスタにおいて、負の電荷を有する第三の層40をゲート電極34下のゲート絶縁膜31中に設けるとともに、ヘテロ接合を形成する窒化物半導体内にフッ素イオンF−等の負のイオン41を注入する。第三の層40はCl−等の負のイオンが注入される。ゲート絶縁膜31中およびAlGaN層11中に適量の負のイオンを注入することにより、しきい値電圧が上がりノーマリオフ動作を確実に達成するとともに、十分なチャネル電流が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】窒化物半導体デバイス層がエッチングされないようにしながら、窒化物半導体デバイス層を基板から剥離することができるようにする。

【解決手段】半導体装置の製造方法を、基板12上に、エッチング犠牲層13を形成する工程と、エッチング犠牲層13上に、エッチングストッパ層2を形成する工程と、エッチングストッパ層2上に、窒化物半導体デバイス層1を形成する工程と、エッチング犠牲層13を、光電気化学エッチングによって除去する工程とを含むものとし、エッチングストッパ層2を、窒化物半導体デバイス層1に正孔が蓄積することを防止する層とする。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、導電性バッファ層を用いることなく、煩雑なプロセスも必要なく、非常に高い深さ精度のドライエッチングも必要なく、また、結晶性を劣化させずに、効率良くホールを引き抜くことができるようにする。

【解決手段】半導体装置を、同一基板1上に形成され、(0001)面及び(000−1)面を有する窒化物半導体層4と、基板1と窒化物半導体層4との間に部分的に設けられた(0001)面形成層2と、(0001)面を有する窒化物半導体層4上に設けられたソース電極5、ドレイン電極6及びゲート電極7と、(000−1)面を有する窒化物半導体層4上に設けられたホール引き抜き電極8とを備えるものとする。

(もっと読む)

半導体装置

【課題】インパクトイオン化現象によって発生した電子・正孔を効率よく吸収することが可能で正常な動作特性と高い信頼性を実現する半導体装置を提供する。

【解決手段】半導体装置20は、基板21に対して順次積層されたバッファ層22、下地化合物半導体層23f(下地化合物半導体層23)、インパクトイオン制御層24、下地化合物半導体層23s(下地化合物半導体層23)、チャネル画定化合物半導体層26f(チャネル画定化合物半導体層26)、チャネル画定化合物半導体層26s(チャネル画定化合物半導体層26)、AlGaN(窒化アルミニウムガリウム)層28、GaN(窒化ガリウム)層29を備えている。インパクトイオン制御層24は、下地化合物半導体層23の積層範囲(積層範囲の厚さTst)内に積層されてインパクトイオン化現象の発生位置を制御する。

(もっと読む)

横型接合型電界効果トランジスタ

【課題】漏れ電流の発生を防止すると共に、十分な耐圧を実現することが可能な横型接合型電界効果トランジスタを提供する。

【解決手段】この発明に従った横型JFET10では、バッファ層11は、SiC基板1の主表面上に位置し、p型不純物を含む。チャネル層12は、バッファ層11上に位置し、バッファ層11におけるp型不純物の濃度より高い濃度のn型不純物を含む。n型のソース領域15およびドレイン領域16は、チャネル層12の表面層において互いに間隔を隔てて形成され、p型のゲート領域17は、チャネル層12の表面層においてソース領域15およびドレイン領域16の間に位置する。バリア領域13は、チャネル層12とバッファ層11との境界領域において、ゲート領域17の下に位置する領域に配置され、バッファ層11におけるp型不純物の濃度より高い濃度のp型不純物を含む。

(もっと読む)

逆拡散抑制構造

エンハンスメントモードGaNトランジスタが提供される。当該トランジスタは、基板と、遷移層と、III族窒化物材料を有するバッファ層と、III族窒化物材料を有するバリア層と、ドレイン及びソースのコンタクトと、アクセプタ型ドーパント元素を含有するゲートと、前記ゲートと前記バッファ層との間の、III族窒化物材料を有する拡散バリアとを有する。  (もっと読む)

(もっと読む)

電界効果トランジスタ

【課題】電流コラプスを抑制することができる電界効果トランジスタを提供する。

【解決手段】ソース電極105、ドレイン電極107およびゲート電極106を備えるHEMT100であって、第1の窒化物半導体からなる第1の半導体層103と、第1の半導体層103上に設けられた、第1の窒化物半導体よりもバンドギャップの大きな第2の窒化物半導体からなる第2の半導体層104とを備え、第1の半導体層103および第2の半導体層104のヘテロ接合によりチャネルが形成され、第1の半導体層103における、ドレイン電極107とゲート電極106との間の下方で、かつ、ヘテロ接合界面から所定の距離おいた領域には、低移動度領域108が設けられ、低移動度領域108は、第1の半導体層103における該低移動度領域108の周囲の領域よりも電子移動度の小さな領域である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】オフ時のリーク電流を低減することができ、好ましくは高い閾値電圧を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】i−GaN層5(電子走行層)と、i−GaN層5(電子走行層)上方に形成されたn−GaN層7(化合物半導体層)と、n−GaN層7(化合物半導体層)上方に形成されたソース電極21s、ドレイン電極21d及びゲート電極21gと、が設けられている。そして、n−GaN層7(化合物半導体層)のソース電極21sとドレイン電極21dとの間の領域内でゲート電極21gから離間した部分にリセス部7a(凹部)が形成されている。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプスを抑制することができる電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタとしてのHEMT100は、第1の窒化物半導体からなる第1の窒化物半導体層103と、第1の窒化物半導体層103の上に形成されて、第1の窒化物半導体よりもバンドギャップの大きな第2の窒化物半導体からなる第2の窒化物半導体層104とを備え、第1の窒化物半導体層103は、貫通転位密度が積層方向に増大する領域を有している。

(もっと読む)

窒化物半導体装置

【課題】チャネル層よりも下側の界面に溜まったキャリアによる高周波成分の損失を低減した窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、第1の窒化物半導体層13と、第1の窒化物半導体層13の上に形成され、第1の窒化物半導体層13と比べてバンドギャップが大きい第2の窒化物半導体層14と、第2の窒化物半導体層14の上に形成された、ソース電極21、ドレイン電極22及びゲート電極23と、第1の窒化物半導体層13よりも下側に形成された高抵抗層11と、高抵抗層11の下側に接して形成された導電層32と、導電層32の下側に形成された下部絶縁層35と、導電層32と電気的に接続されたバイアス端子31とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】半絶縁性SiC基板を用いずとも良好な高周波数特性を得ることができる半導体装置及びその製造方法を提供する。

【解決手段】導電性SiC基板1上に化合物半導体領域2が形成されている。化合物半導体領域2には、順次積層されたバッファ層2a、電子走行層2b、電子供給層2c及び表面層2dが含まれている。化合物半導体領域2には、活性領域を画定する素子分離領域3が設けられている。そして、活性領域と整合するようにして、導電性SiC基板1に開口部1aが形成されている。表面層2dには、電子供給層2cを露出する2個の開口部が形成されており、開口部の各々に、オーミック電極がソース電極4又はドレイン電極5として形成されている。更に、開口部10aを介して表面層2dと接するゲート電極6がシリコン窒化膜10上に形成されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】安価な基板を用いて製造することができ、良好な特性を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】p型GaN層2と、p型GaN層2上に形成され、空乏化されたn型GaN層3と、n型GaN層3上に形成された厚さが30μm以上のアンドープのGaN層4と、が設けられている。更に、GaN層4上に形成された活性層5と、活性層5上に形成された電極層6と、が設けられている。これらの積層体は、サファイア基板を用いて形成されたものであり、積層体の形成後にサファイア基板が分離されている。

(もっと読む)

半導体装置、ウエハ構造体および半導体装置の製造方法

【課題】放熱効率を向上し且つ歩留りや信頼性の低下を防止することが可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】裏面に凹部DP1が形成されたシリコン基板101と、シリコン基板101における裏面と反対側の上面上に成長されたp型半導体層103と、p型半導体層103の上方または側方に互いに離間して形成されたソース電極108sおよびドレイン電極108dと、を含むMOSFETと、を備える。p型半導体層103は、シリコン基板101に対して格子定数および熱膨張係数のうち少なくとも1つが異なる。凹部DP1は、シリコン基板101の厚み方向から見て少なくともソース電極108sおよびドレイン電極108dで挟まれた領域を内包する領域に形成されている。

(もっと読む)

半導体装置

【課題】ノーマリオフ特性が実現され、飽和電流値低下が生じず、ゲート電圧に対するドレイン・ソース間電流特性が良好なHEMTを実現する半導体装置を提供する。

【解決手段】第1半導体層131と、第1半導体層131の主面135上に積層され、第1半導体層131の主面135側に2DEG層137を生じさせる第2半導体層133と、第1半導体層131及び第2半導体層133と比して電子親和力χが大きい半導体材料からなり、2DEG層137と電気的に接続された第3半導体層139と、第2半導体層133及び第3半導体層139上に設けられた絶縁膜157と、第3半導体層139にオーミック接続される第1電極151と、第2半導体層133及び第3半導体層139上に絶縁膜157を介して設けられた第2電極153と、第1電極151との間に第2電極153を介在させ、2DEG層137と電気的に接続された第3電極155とを備える。

(もっと読む)

テラヘルツ光検出装置とその検出方法

【課題】極低温を必要することなく、小規模の装置で、非常に微弱なテラヘルツ光の強度を明確に検出でき、かつその周波数を正確に測定することができるテラヘルツ光検出装置とその検出方法を提供する。

【解決手段】表面から一定の位置に2次元電子ガス13が形成された半導体チップ12と、半導体チップの表面に密着して設けられたカーボンナノチューブ14、導電性のソース電極15、ドレイン電極16及びゲート電極17とを備える。カーボンナノチューブ14は、半導体チップの表面に沿って延び、かつその両端部がソース電極とドレイン電極に接続され、ゲート電極17は、カーボンナノチューブの側面から一定の間隔を隔てて位置する。さらに、ソース電極とドレイン電極の間に所定の電圧を印加しその間のSD電流を検出するSD電流検出回路18と、ソース電極とゲート電極の間に可変電圧を印加しその間のゲート電圧を検出するゲート電圧印加回路19と、半導体チップに可変磁場を印加する磁場発生装置20とを備える。

(もっと読む)

高周波用半導体素子形成用のエピタキシャル基板および高周波用半導体素子形成用エピタキシャル基板の作製方法

【課題】コストメリットがあり、かつ、特性の優れた高周波動作用の半導体素子を実現できるエピタキシャル基板を提供する。

【解決手段】導電性を有するSiCまたはSiからなる基材の上に、絶縁性を有する第1のIII族窒化物からなる下地層をMOCVD法によって、表面に実質的に非周期的な凹凸構造を有するようにエピタキシャル形成し、下地層の上に、GaNからなるチャネル層をエピタキシャル形成し、チャネル層の上に、AlxGa1-xN(0<x<1)からなる障壁層をエピタキシャル形成する。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性及びチャネル移動度が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化物系化合物半導体からなる電界効果トランジスタであって、基板上に形成された所定の導電型を有する半導体層と、エピタキシャル成長によって前記半導体層とソース電極およびドレイン電極のそれぞれとの間に形成された、前記所定の導電型とは反対の導電型を有するコンタクト層と、エピタキシャル成長によって前記ドレイン電極側のコンタクト層と前記半導体層との間にゲート絶縁膜を介してゲート電極と重畳するように形成された、前記所定の導電型とは反対の導電型を有するとともに該コンタクト層よりもキャリア濃度が低い電界緩和層と、を備える。

(もっと読む)

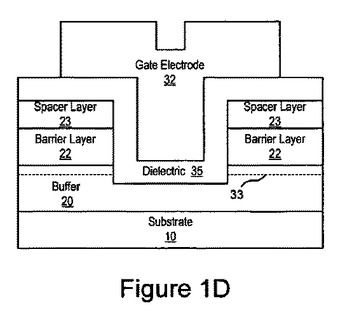

常時オフ半導体デバイスおよびその作製方法

常時オフ半導体デバイスが提供される。III族窒化物バッファ層が提供される。III族窒化物バリア層がIII族窒化物バッファ層上に設けられる。非伝導性スペーサ層がIII族窒化物バリア層上に設けられる。III族窒化物バリア層およびスペーサ層がエッチングされてトレンチを形成する。トレンチはバリア層を貫いて延びてバッファ層の一部を露出させる。誘電体層がスペーサ層上およびトレンチ内に形成され、ゲート電極が誘電体層上に形成される。半導体デバイスの形成に関連する方法も提供される。  (もっと読む)

(もっと読む)

GaN系化合物半導体からなる双方向スイッチング素子

【課題】1つのデバイスによってノーマリオフ型で、低損失の双方向スイッチ機能を有するデバイスを実現する。

【解決手段】本発明の双方向スイッチング素子は、一の導電型を有する動作層と、前記動作層上に形成された第1の電極及び第2の電極と、前記動作層内であって、前記第1の電極に接して形成された反対導電型を有する第1のコンタクト層と、前記動作層内であって、前記第2の電極に接して形成された反対導電型を有する第2のコンタクト層と、前記動作層上で、絶縁膜を介して、第1の電極と第2の電極間の中心線に対して略対称に形成された少なくとも1つのゲート電極と、前記ゲートに対応する部分の動作層に形成されたチャネル部と、前記第1のn形半導体層と前記第2のn形半導体層の間に少なくとも1つ形成され、前記第1のコンタクト層及び前記第2のコンタクト層よりも低い不純物濃度の反対導電型を有する電界緩和層とを備える。

(もっと読む)

窒化物系化合物半導体装置

【課題】ゲートリーク電流の増大、及び電流コラプス現象によるオン抵抗の増大を抑制できる窒化物系化合物半導体装置を提供する。

【解決手段】III族窒化物系化合物半導体からなる半導体層2と、半導体層2上に配置されたソース電極3及びドレイン電極4と、半導体層2上にソース電極3とドレイン電極4との間に配置された絶縁膜6と、絶縁膜6に設けられた開口部で半導体層2に接する有機半導体層7と、開口部の有機半導体層7上に配置されたゲート電極5とを備える。

(もっと読む)

61 - 80 / 124

[ Back to top ]