Fターム[5F102GR06]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 半導体基体内に付加領域を設けたもの (876)

Fターム[5F102GR06]の下位に属するFターム

不純物領域 (317)

絶縁領域(高抵抗領域を含む) (273)

エッチングストッパとなる層 (162)

Fターム[5F102GR06]に分類される特許

21 - 40 / 124

半導体装置およびその製造方法

【課題】本発明は、SBD、HEMT等のデバイスに逆方向電圧をかけたときの電極端部に生じる電界集中を緩和して電流コラプス、及び長期信頼性の問題を解決した半導体装置を提供する。

【解決手段】窒化物化合物半導体層を有する電子走行層11と、前記電子走行層11に形成された窒化物化合物半導体からなる電子供給層12と、前記電子供給層12上に形成された第1電極13と、前記電子供給層12上に前記第1電極13と離間して形成された第2電極14と、前記電子走行層11および前記電子供給層12を挟んで前記第1電極13に対向して形成された、前記第1電極13と同電位の第1導電体14と、前記電子走行層11および前記電子供給層12を挟んで前記第2電極14に対向して形成された、前記第2電極14と同電位の第2導電体16とを有する半導体装置1を提供する。

(もっと読む)

半導体素子および半導体素子の作製方法

【課題】ノーマリーオフ動作型の半導体素子を複雑な工程を経ることなく作製する方法を提供する。

【解決手段】半導体素子の作製方法が、下地基板の上に、少なくともGaを含む、Inx1Aly1Gaz1N(x1+y1+z1=1)なる組成の第1のIII族窒化物からなるチャネル層を形成する工程と、チャネル層の上に、少なくともAlを含む、Inx2Aly2Gaz2N(x2+y2+z2=1)なる組成の第2のIII族窒化物からなる障壁層を形成する工程と、障壁層の表面の、ソース電極およびドレイン電極の形成予定個所に対し、ソース電極およびドレイン電極を形成する工程と、障壁層の表面の、ゲート電極の形成予定個所に対し、アルゴンプラズマ処理または酸素プラズマ処理を施す工程と、プラズマ処理工程を経たゲート電極の形成予定個所にゲート電極を形成する工程と、を備えるようにする。

(もっと読む)

半導体積層体とこれを含むHFETおよびそれらの製造方法

【課題】半導体積層体に含まれるチャネル層下の化合物半導体層を不純物ドーピングでp型化することなく、その半導体積層体を含むHFETのリーク電流の低減や耐電圧の向上などを可能とする。

【解決手段】半導体積層体は、基板(11)上において順次堆積された第1、第2および第3の化合物半導体層(13、14、15)を少なくとも含み、その第1化合物半導体層(13)の少なくとも部分的層(16)は非晶質に改質されており、第2化合物半導体層(14)は第1化合物半導体層(13)に比べて小さなバンドギャップを有して光吸収層として作用し得る。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させ、かつ、チップサイズの増加を抑制した、窒化物系半導体装置を提供することができる、窒化物系半導体装置を提供することを目的とする。

【解決手段】ショットキー電極30が、ソース電極24とドレイン電極26とが対向する領域の、ソース電極24とドレイン電極26とが対向する方向と略直交する方向にゲート電極28と並んで形成されている。ショットキー電極30は、AlGaN層20とショットキー接合されており、ソース電極24に電気的に接続されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】容量増加による高周波特性の劣化及び裏面電極に起因する絶縁破壊を抑止し、チップ面積を増加させることなく、インパクトイオン化により生成したホールを容易且つ確実に引き抜いて排出することを可能として、高耐圧性及び高信頼性を実現する化合物半導体装置及びその製造方法を提供する。

【解決手段】絶縁性又は半絶縁性の基板1の表面に電子走行層3、電子供給層4が形成され、電子供給層4内には局所的なp型領域7が形成されており、基板1の裏面にp型領域7の一部を露出させる開口1aが形成され、開口1aを導電材料で埋め込みp型領域7とオーミック接続された裏面電極8を備え、AlGaN/GaN・HEMTが構成される。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】電流コラプスを抑制し、高出力動作可能な窒化物半導体装置を提供する。

【解決手段】ショットキ接触する電極(ゲート電極16)16とオーミック接触する電極(ソース電極17a、ドレイン電極17b)との間のIII−V族窒化物半導体層14表面に、ECRスパッタリング法により珪素膜15を形成する。ショットキ接触する電極16とIII−V族窒化物半導体層14との間に、珪素膜15を形成してもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置が有する保護膜や層間絶縁膜にかかる電界を抑制し、半導体装置の絶縁破壊耐圧を向上する。

【解決手段】半導体装置は、基板1と、基板の上方に形成されたキャリア走行層4と、キャリア走行層の上に形成された化合物半導体層5,6,7と、化合物半導体層の上に形成されたソース電極10と、基板の裏面から基板を貫通し、キャリア走行層の内部まで形成された第1の溝12と、第1の溝の内部に形成されたドレイン電極14と、ソース電極10と第1の溝12との間に位置し、化合物半導体層の上に形成されたゲート電極11と、ソース電極の斜め下方であってソース電極と第1の溝との間に位置し、基板の裏面から基板を貫通し、キャリア走行層4の内部まで形成された第2の溝13と、を備える。

(もっと読む)

シングルゲートまたはマルチゲートフィールドプレート製造

【課題】電界効果型トランジスタの表面に、誘電性材料の堆積/成長させ、誘電性材料をエッチングし、および、メタルを蒸着させる、連続的なステップを用いる、シングルゲートまたはマルチゲートプレートの製造プロセスの提供。

【解決手段】本製造プロセスは、誘電性材料の堆積/成長が、典型的には、非常によく制御できるプロセスなので、フィールドプレート動作を厳しく制御できる。さらに、デバイス表面に堆積された誘電性材料は、デバイスの真性領域から除去される必要はない。このため、乾式または湿式のエッチングプロセスで受けるダメージの少ない材料を用いることなく、フィールドプレートされたデバイスを、実現することができる。マルチゲートフィールドプレートを使うと、マルチ接続を使用するので、ゲート抵抗を減らすこともでき、こうして、大周辺デバイスおよび/またはサブミクロンゲートデバイスの性能を向上することができる。

(もっと読む)

半導体装置

【課題】本発明は、外部ノイズ等の過大電流に起因するHEMTの損傷、破壊若しくは発火を防止することができる半導体装置を提供する。

【解決手段】半導体装置1は、第1の半導体層31と、第2の半導体層32と、二次元キャリアガス層33と、ソース電極41と、ドレイン電極42と、ゲート電極5と、二次元キャリアガス層33上においてゲート電極5とドレイン電極42との間に配設された補助電極6と、を備え、二次元キャリアガス層33のゲート電極5とソース電極6との間のチャネル抵抗R1に比べて、二次元キャリアガス層33のゲート電極5と補助電極6との間のチャネル抵抗R2が高く設定されている。

(もっと読む)

化合物半導体装置

【課題】ゲート電極の端部でのバイアス電界集中が緩和され、且つ動作時のオン抵抗の増大が抑制された化合物半導体装置を提供する。

【解決手段】キャリア供給層22、及びキャリア供給層22との界面近傍において二次元キャリアガス層23が形成されるキャリア走行層21を有する化合物半導体層20と、化合物半導体層20の主面200上に配置されたソース電極3及びドレイン電極4と、ソース電極3とドレイン電極4間で主面200上に配置されたゲート電極5と、ゲート電極5とドレイン電極4間で主面200上方に配置されたフィールドプレート6と、フィールドプレート直下の二次元キャリアガス層が形成される領域内に配置された、上方にフィールドプレート若しくはゲート電極が配置されていない二次元キャリアガス層が形成される領域よりも導電率が低い低導電性領域210とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】III-V族窒化物半導体を有する半導体装置において、熱による出力低下を低減する。

【解決手段】半導体装置は、基板101上に設けられ、III-V族窒化物半導体からなるバッファ層102と、バッファ層102上に設けられ、III-V族窒化物半導体からなる第1の半導体層103と、第1の半導体層103上に設けられ、III-V族窒化物半導体からなる第2の半導体層104と、基板101の裏面上に設けられ、接地に接続された裏面電極111と、第2の半導体層104上に互いに離間して設けられたソース電極132及びドレイン電極134と、第2の半導体層104上に設けられたゲート電極136とと、第2の半導体層104、第1の半導体層103、及びバッファ層102を貫通し、少なくとも基板101に達し、ソース電極132と裏面電極111とを電気的に接続させるプラグ109とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】ドレイン電流コラプスを抑制すること。

【解決手段】窒化物半導体層19上に形成されたソース電極20、ゲート電極24およびドレイン電極22と、前記窒化物半導体層上に接して形成された窒化シリコン膜26と、前記ゲート電極と前記ドレイン電極との間の前記窒化シリコン膜の上面に接して設けられた有機絶縁膜32と、を含む半導体装置。

(もっと読む)

半導体装置

【課題】作製プロセスに起因する特性劣化を生ぜず、ボンディングパッドの電位変化による特性変化を受け難い小型化した半導体装置を提供する。

【解決手段】半導体装置10は、アクティブ領域12と、アクティブ領域12を覆う第1の絶縁層13と、第1の絶縁層13上に形成されるフローティング導体14と、第1の絶縁層13上およびフローティング導体14上に形成される第2の絶縁層15と、第2の絶縁層17上に形成されたボンディングパッド18と、アクティブ領域12とボンディングパッド18を電気的に接続する導通ビア19,20と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】ドレイン電流コラプスを抑制すること。

【解決手段】窒化物半導体層19上に、ソース電極20、ゲート電極24およびドレイン電極22をそれぞれ形成する工程と、前記窒化物半導体層上に窒化シリコン膜26を形成する工程と、前記ゲート電極と前記ドレイン電極との間の前記窒化シリコン膜の上面をフッ酸を含む溶液を用い処理する工程と、を含む半導体装置の製造方法。

(もっと読む)

電界効果トランジスタ

【課題】III族窒化物半導体からなる電界効果トランジスタにおける高電圧スイッチング時の電流コラプスを効果的に抑制できるようにする。

【解決手段】第1の半導体層103は、少なくともゲート電極106におけるドレイン電極107側の端部の下側の領域において、炭素濃度が1×1017cm−3未満である低炭素濃度領域を有し、基板101の上面から第1の半導体層103及び第2の半導体層104を含むドレイン電極までの半導体層の厚さをd1(μm)とし、低炭素濃度領域の厚さをd2(μm)とし、動作耐圧をVm(V)としたとき、Vm/(110・d1)≦d2<Vm/(110・d1)+0.5の関係を満たし、且つ、緩和状態におけるオン抵抗をRon0とし、動作電圧Vmにおけるオフ状態からオン状態に遷移した100μs後のオン抵抗をRonとしたとき、電流コラプス値の指標とするRonとRon0との比の値が、Ron/Ron0≦3である。

(もっと読む)

半導体装置

【課題】高温・高電圧で動作させた場合でも故障の発生を抑制することが可能な半導体装置を提供すること。

【解決手段】本発明は、GaNキャップ層38上のソースフィンガー12と、ソースフィンガーと交互に配置されたドレインフィンガー14と、ソースフィンガーとドレインフィンガーとの間のゲートフィンガー16と、ゲートフィンガーの上面と側面を覆う第1絶縁膜44と、ゲートフィンガーとドレインフィンガーとの間の第1絶縁膜上に設けられたフィールドプレート26と、活性領域18の外側で第1絶縁膜上にフィンガー方向と交差方向に設けられソースフィンガーとその両側のフィールドプレートとを接続するフィールドプレート配線28と、を備え、フィールドプレートと第1絶縁膜の第1段差部46とは100nm以上離れ、フィールドプレート配線と第1絶縁膜の第2段差部48とは100nm以上離れている半導体装置である。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】本発明は、ソース電極およびドレイン電極の熱耐久性を向上させて、かつ製造過程においてオーミック性に与える不安定要因を取り除き信頼性および量産性の高いGaN系HEMTを提供する。

【解決手段】GaN系HEMTは、基板と、窒化ガリウム系半導体と、融点が3000℃と高融点金属のタンタルと低融点金属のアルミニウムが前記窒化ガリウム系半導体上に積層されてなる前記ソースおよび前記ドレイン電極を備えている。前記ソース電極および前記ドレイン電極は、前記タンタルと前記アルミニウムの積層膜厚の比(前記アルミニウム膜厚/前記タンタル膜厚)を10以上にし、積層後のアニール処理温度が510℃以上、600℃未満で処理されて成る。

(もっと読む)

半導体装置

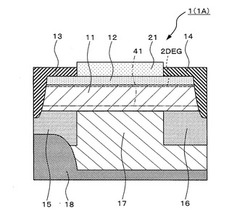

【課題】2DEGをチャンネルとして用いる半導体装置において、不純物イオンの侵入による悪影響を排除する。

【解決手段】第1の半導体層である電子走行層11上に、第2の半導体層である電子供給層12が形成されている。これらの界面(ヘテロ接合界面)における電子走行層11側に、2次元電子ガス(2DEG)層13が形成される。ソース電極14からドレイン電極15の間の2DEG層13が形成された領域がこの半導体装置10におけるチャンネル領域となる。このチャンネル領域上の絶縁層17上において、第1のフィールドプレート18が形成されている。すなわち、第1のフィールドプレート18は、2つの主電極のうちの一方から他方に達するチャンネル領域上を覆うように形成されている。

(もっと読む)

電界効果トランジスタ

【課題】クラックを低減した窒化物半導体電界効果トランジスタを実現できるようにする。

【解決手段】電界効果トランジスタは、基板101の上に形成された半導体層積層体と、半導体層積層体の上に形成されたソース電極107及びドレイン電極108と、ソース電極とドレイン電極との間に形成されたゲート電極109とを備えている。半導体層積層体は、第1の凹部102aを有する第1の窒化物半導体層102と、第1の凹部の底面上に形成された第2の窒化物半導体層105と、第1の凹部を除く領域の上及び第1の凹部の側面上に形成された第3の窒化物半導体層106とを有している。バンドギャップエネルギーの平均値が、第2の窒化物半導体層は第1の窒化物半導体層よりも大きく、第3の窒化物半導体層は第1の窒化物半導体層よりも大きく且つ第2の窒化物半導体層よりも小さい。

(もっと読む)

半導体装置

【課題】 表面保護膜中へのホットキャリアの侵入に起因する半導体装置の出力低下を抑制すること。

【解決手段】 本半導体装置100は、窒化ガリウム系半導体からなる電子走行層12と、電子走行層12上に設けられ、窒化ガリウム系半導体からなる電子供給層16と、電子供給層16上に設けられ、窒化ガリウムからなるキャップ層18と、キャップ層18上に設けられたゲート電極24と、電子供給層16上にゲート電極24を挟んで設けられたソース電極20及びドレイン電極22と、キャップ層18上に設けられた表面保護膜30と、キャップ層18と表面保護膜30との間に介在し、少なくともゲート電極24とドレイン電極22との間の領域に設けられたAlxGa1−xN(0.5≦x≦1)からなるバリア層50と、を備える。

(もっと読む)

21 - 40 / 124

[ Back to top ]