Fターム[5F102GR06]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 半導体基体内に付加領域を設けたもの (876)

Fターム[5F102GR06]の下位に属するFターム

不純物領域 (317)

絶縁領域(高抵抗領域を含む) (273)

エッチングストッパとなる層 (162)

Fターム[5F102GR06]に分類される特許

41 - 60 / 124

電界効果トランジスタ

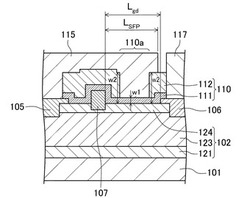

【課題】電流コラプスが小さく且つ良好な高周波特性を有する電界効果トランジスタを実現できるようにする。

【解決手段】電界効果トランジスタは、基板101の上に形成された窒化物半導体積層体102と、ソース電極105、ドレイン電極106及びゲート電極107と、窒化物半導体積層体102の上に形成された絶縁膜110と、絶縁膜110の上に接して形成され、端部がゲート電極107とドレイン電極106との間に位置するフィールドプレート115とを備えている。絶縁膜110は、第1の膜111と、第1の膜111よりも絶縁耐圧が低い第2の膜112とを含み、ゲート電極117とドレイン電極116との間に形成された薄膜部110aを有している。フィールドプレート115は、薄膜部110aを覆い且つ開口部においてソース電極と接続されている。

(もっと読む)

HFET

【課題】耐圧が高いHFET(Heterojunction−FET)を提供する。

【解決手段】ヘテロ接合16aに生じる2次元電子ガスをチャネルとするHFET10であって、第1半導体領域16と、第1半導体領域16上で第1半導体領域16とヘテロ接合している第2半導体領域18と、第2半導体領域18上に形成されたソース電極20、ドレイン電極22及びゲート電極24と、第1半導体領域16と接しており、ソース電極20と導通しているp型の第3半導体領域14を有している。ゲート電極24とドレイン電極22の間の第2半導体領域18の上面のうちの、ゲート電極24に隣接する範囲の上面は、第1表面準位密度を有する第1領域40であり、第1領域40に隣接する範囲の上面は、第1表面準位密度より低い第2表面準位密度を有する第2領域42である。第3半導体領域14は、第2領域42の下側で第1半導体領域16に接している。

(もっと読む)

テラヘルツ波受信素子

【課題】テラヘルツ波を効率よく受信し、信号/雑音比を向上したテラヘルツ波受信素子を提供する。

【解決手段】第1の波長λ1のテラヘルツ波を受信するテラヘルツ波受信素子100であ

って、2以上の半導体層(バッファ層102aおよび電子供給層104a)のヘテロ接合により形成される2次元電子チャネル層103a、ゲート幅方向にλ1/2の長さを有するゲート電極111a、ドレイン電極113aおよびソース電極112aを有する第1のFET100aと、第1のFET100aのゲート電極111aのゲート幅方向における中央部と接続され、かつ、ゲート電極111aと直交するように配置されたゲート配線114aとを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明の半導体装置は、nチャネルの高電子移動度トランジスタ(HEMT)とpチャネル電界効果トランジスタとを単一の基板上に形成した。

【解決手段】nチャネル電界効果トランジスタは、第1チャネル層7と、この第1チャネル層7にヘテロ接合し、n型の電荷を供給するn型第1障壁層6と、n型第1障壁層6に対してpn接合型の電位障壁を有するp型ゲート領域10とを備え、pチャネル電界効果トランジスタは、p型の第2チャネル層13と、pn接合型の電位障壁を有するn型ゲート領域18とを備える。各トランジスタはpn接合型のゲート領域を有するのでターンオン電圧を高くすることが可能となり、ゲート逆方向リーク電流を減少させたエンハンスメントモードでの動作を実現した。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプスが抑制された窒化物半導体を用いた電界効果トランジスタを容易に実現できるようにする。

【解決手段】電界効果トランジスタは、基板100の上に形成され、第1の窒化物半導体層122及び第2の窒化物半導体層123を有する半導体層積層体102を備えている。半導体層積層体102の上には、互いに間隔をおいてソース電極131及びドレイン電極132が形成されている。ソース電極131とドレイン電極132との間には、ソース電極131及びドレイン電極132と間隔をおいてゲート電極133が形成されている。ドレイン電極132の近傍には正孔注入部141が形成されている。正孔注入部141は、p型の第3の窒化物半導体層142及び第3の窒化物半導体層142の上に形成された正孔注入電極143を有している。ドレイン電極132と正孔注入電極142とは、電位が実質的に等しい。

(もっと読む)

デュアル・デプレションを示す高電子移動度トランジスタ及びその製造方法

【課題】デュアル・デプレションを示す高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】互いに異なる極性を有する複数の半導体層20,22を含み、ソース電極28とドレイン電極32との間にデュアル・デプレション領域が存在し、該複数の半導体層は、上部物質層26、中間物質層22、下部物質層20を含み、中間物質層の極性は、上部物質層及び下部物質層の極性と異なる高電子移動度トランジスタである。

(もっと読む)

半導体装置およびその作製法

【課題】窒化物半導体を用いたヘテロ構造電界効果トランジスタにおいて、オーミック接触抵抗を大きく低減し、同時に、ソース電極2からチャネルまでの抵抗(アクセス抵抗)を大きく低減し、その結果として、高速化および低損失化(低消費電力化)が可能となる半導体装置およびその作製法提供すること。

【解決手段】ソース電極2とドレイン電極4とに、それぞれオーミック接触し、チャネル層窒化物半導体よりも小さいバンドギャップを有する再成長窒化物半導体(2)と、前記チャネル層窒化物半導体との間を、再成長組成傾斜窒化物半導体(1)を介して接続することによって、ソース電極2とチャネルとの間、および、ドレイン電極4とチャネルとの間を、それぞれ結ぶ電路中の半導体バンドギャップの不連続が解消されていることを特徴とするヘテロ構造電界効果トランジスタを構成する。

(もっと読む)

窒化物半導体装置及び窒化物半導体装置の製造方法

【課題】基板の放熱性が高くて基板に形成される窒化物半導体層の結晶欠陥が少ない窒化物半導体装置及びその製造方法を提供する。

【解決手段】

HEMT10の製造方法は、サファイア基板11の表面にGaNの薄膜12を形成する成膜工程と、薄膜12の上端からサファイア基板11の内部に達する深さの溝を形成する溝形成工程と、溝形成工程の後に、薄膜12を種結晶としてGaN層13を成長させる成長工程と、成長工程の前又は後に、サファイアよりも熱伝導性が高い高熱伝導性材料としてのAuを溝17に充填する充填工程とを備えている。

(もっと読む)

モノリシック集積複合III−V族及びIV族半導体デバイス、並びにその製造方法

【課題】単一のダイの上にIII−V族半導体デバイスをIV族半導体デバイスと共に集積する、複合デバイスの製造方法を提供する。

【解決手段】IV族半導体基板202上にIII−V族半導体本体274a,274bを形成するステップと、III−V族半導体本体にトレンチを形成し、トレンチ内にIV族半導体本体232を形成するステップとを有する。この方法は、IV族半導体本体内に少なくとも1つのIV族半導体デバイス272を製造するステップと、III−V族半導体本体内に少なくとも1つのIII−V族半導体デバイス274を製造するステップも含む。III−V族半導体本体の上面とIV族半導体本体の上面とを平坦化して、それぞれの上面をほぼ同一平面にするステップをさらに含む。一実施形態では、トレンチの側壁に隣接する、前記IV族半導体本体の欠陥領域に、少なくとも1つの受動デバイスを製造するステップをさらに含む。

(もっと読む)

電界効果トランジスタ、電子装置、電界効果トランジスタの製造方法及び使用方法

【課題】 チップ面積を大きくし過ぎることなく、過電圧、過電力が加わっても破壊されない電界効果トランジスタを提供する。

【解決手段】 本発明の電界効果トランジスタは、

半導体層上に、ゲート電極110と、ドレイン電極109と、ソース電極108と、保護ダイオード(保護ダイオード電極)111とが配置され、

ドレイン電極109が、保護ダイオード111の周囲の一部もしくは全部を囲む状態で形成されているか、または、

ドレイン電極109は、複数であり、複数のドレイン電極109の少なくとも一対のドレイン電極間に、保護ダイオード111が配置されるように形成されていることを特徴とする。

(もっと読む)

高電子移動度トランジスタ

【課題】 HEMTにおいて、2次元電子ガス層の電気抵抗の増加が抑制された正孔排出用電極を提供すること。

【解決手段】 HEMT10は、ゲート電極34とドレイン電極32の間のヘテロ接合層27に接触する正孔選択通過膜43と、その正孔選択通過膜43に接触する正孔排出用電極46を備えている。正孔選択通過膜43は、へテロ接合層27に接触する第1部分領域42と正孔排出用電極46に接触する第2部分領域44を有している。第2部分領域42のp型不純物の濃度は、第1部分領域44のp型不純物濃度よりも濃い。

(もっと読む)

化合物半導体装置

【課題】電流コラプスを抑制しつつ所望の特性が得られる化合物半導体装置を提供する。

【解決手段】化合物半導体装置は、GaNからなる電子走行層120と、AlGaNからなる電子供給層130と、電子供給層上に設けられたソース電極150、ゲート電極160およびドレイン電極170と、少なくともソース電極とゲート電極との間およびゲート電極とドレイン電極との間に設けられたGaNからなるキャップ層140と、ゲート電極とドレイン電極との間のキャップ層に設けられたリセス部と、リセス部とドレイン電極との間のキャップ層に設けられリセス部よりも大きな厚みを有する層厚部と、を備える。

(もっと読む)

III−V族半導体装置の導電性の改善

III-V族半導体装置における導電性の改善について示した。第1の改良は、チャネル層とは幅の異なるバリア層を有することである。第2の改良は、金属/Si、Ge、またはシリコン-ゲルマニウム/III-Vスタックの熱処理により、Siおよび/またはゲルマニウムドープIII-V層に、金属-シリコン、金属-ゲルマニウム、または金属-シリコンゲルマニウム層を形成することである。次に、金属層が除去され、金属-シリコン、金属-ゲルマニウム、または金属シリコンゲルマニウム層上に、ソース/ドレイン電極が形成される。第3の改良は、III-Vチャネル層上に、IV族元素および/またはVI族元素の層を形成し、熱処理し、III-Vチャネル層に、IV族および/またはVI族化学種をドープすることである。第4の改良は、III-V装置のアクセス領域に形成された、パッシベーション層および/またはダイポール層である。  (もっと読む)

(もっと読む)

電界効果トランジスタ

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供すること。

【解決手段】この電界効果トランジスタは、略同一の第1、第2トランジスタ部11,12を備える。第1のトランジスタ部11は、ヘテロ接合を含むIII族窒化物半導体層構造、III族窒化物半導体層構造上に間隔をおいて配置されたソース電極5およびドレイン電極7、フィールドプレート91を有するゲート電極6、ドレイン電極7を被覆するように配置された絶縁体層8を有する。フィールドプレート91は、ドレイン電極7を覆うようにひさし状に延在する。第2のトランジスタ部12は、第1のトランジスタ部11と略面対称に配置されている。第1のトランジスタ部11のIII族窒化物半導体層構造、絶縁体層8およびドレイン電極7は、第2のトランジスタ部12において対応する構造または層と一体化されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度を得ながら、かつ、縦方向耐圧およびゲート電極端における耐圧の両方の耐圧性能を確実に得ることができる、半導体装置およびその製造方法を提供する。

【解決手段】 n型ドリフト層および該n型ドリフト層上に位置するp型層を含むGaN系積層体に、開口部が設けられ、開口部を覆うように位置する、チャネルを含む再成長層と、再成長層に沿って該再成長層上に位置するゲート電極とを備え、開口部はn型ドリフト層に届いており、ゲート電極の端は、平面的に見てp型層から外れた部分がないように位置していることを特徴とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】本発明は、化合物半導体素子の動作に関係なく、リーク電流を防止することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置1は、2DEG310を有する第1の化合物半導体層31と、第1の化合物半導体層31上に配設され、キャリア供給層として機能する第2の化合物半導体層32と、2DEG310上に配設された第1の電極61と、2DEG310上において第1の電極61から離間して配設された第2の電極42と、を備えた化合物半導体素子10と、化合物半導体素子10の周囲を取り囲む領域の一部において2DEG310上に配設され、この2DEG310のキャリア濃度を低減させる外周電極62を有する外周領域11とを備える。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法および使用方法

【課題】 スイッチング速度の低下やオン抵抗の増大を抑制しつつ、オフ耐圧を改善可能な半導体装置を提供する。

【解決手段】

半導体層11および12は、基板10上に形成され、第1の電極101、第2の電極102および絶縁膜14は、それぞれ、半導体層11および12上に形成され、絶縁膜14は、第1の電極101と第2の電極102との間に配置され、フィールドプレート電極17Aおよび17Bは、複数であり、かつ、絶縁膜14上に点在し、第1の電極101および第2の電極102は、半導体層11および12を介して電気的に接続されており、前記第1の電極と前記第2の電極との間の電圧印加時における電流の方向と垂直方向の各フィールドプレート電極の長さ、および、前記電流の方向と垂直方向に隣接する各フィールドプレート電極間の距離が、それぞれ、第1の電極101と第2の電極102との間の距離以下であることを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】GaN電子走行層、AlGaN電子供給層、およびGaNキャップ層が順次積層された半導体装置において、高周波数動作および高出力動作を実現することが可能な半導体装置を提供すること。

【解決手段】本発明は、基板10上に順次積層されたGaN電子走行層12、AlGaN電子供給層14、およびGaNキャップ層16と、GaNキャップ層16上に形成されたゲート電極18と、ゲート電極18の両側であって、AlGaN電子供給層14上に形成されたソース電極20およびドレイン電極22と、ゲート電極18とソース電極20との間のGaNキャップ層16に形成された第1の凹部30と、を具備し、第1の凹部30が有する底面32下におけるGaNキャップ層16の厚さは、ゲート電極18下におけるGaNキャップ層16の厚さに比べて薄い半導体装置である。

(もっと読む)

窒化物半導体デバイス

【課題】 ウエハ−プロセスで基板の上に製造された素子単位をチップ分離する際に研磨、切断などの工程を減らすことができ、基板を繰り返し使用できる窒化物半導体デバイス作製方法によって作製したデバイスを提供する。

【解決手段】 閉曲線をなす結晶成長速度の遅い欠陥の集合した欠陥集合領域Hと結晶成長速度の速い低欠陥の領域ZYの位置が予め決まっている窒化物半導体欠陥位置制御基板Sを用い、低欠陥領域ZYにデバイスの内部が、欠陥集合領域Hに境界線が来るように窒化ガリウム基板の上に窒化物半導体層(上層部B)をエピタキシャル成長させ、レーザ照射或いは機械的手段で欠陥位置制御基板Sと成長層(上層部B)を上下方向横方向に同時分離し、基板は繰り返し使用する。作製されたデバイスは端面が成長によるファセットで形成されている。

(もっと読む)

半導体素子およびその製造方法

【課題】より高いブレークダウン電圧に適した半導体素子構造およびその製造方法を提供する。

【解決手段】半導体基板構造(100)は、半導体基板(1)と、半導体基板(1)の上部にGaNタイプの層スタック(20)とを備える。GaNタイプ層スタック(20)は、少なくとも1つのバッファ層(21,22)と、第1活性層(2)と、第2活性層(3)とを備え、第1活性層と第2活性層の界面において、能動素子領域が規定可能である。半導体基板(1)は、絶縁層(12)の上に存在しており、所定のパターンに従って溝(14)を規定するようにパターン化され、そのパターンは、こうした能動素子領域の下地となる少なくとも1つの溝(14)を含み、前記溝(14)は、絶縁層(12)から、GaNタイプ層スタック(20)の少なくとも1つのバッファ層(21,22)の中まで延びて、前記少なくとも1つのバッファ層(22)の範囲で過成長しており、第1および第2活性層(2,3)は、少なくとも能動素子領域の範囲で連続している。

(もっと読む)

41 - 60 / 124

[ Back to top ]