Fターム[5F102GR11]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 非対称構造 (606)

Fターム[5F102GR11]の下位に属するFターム

S−G電極間とD−G電極間の距離が異なるもの (319)

ソースとドレインの形状、不純物濃度が異なるもの (111)

Fターム[5F102GR11]に分類される特許

161 - 176 / 176

窒素化合物半導体素子

【課題】放熱性が良好で、且つ、製造コストを抑制することができるとともに、高耐圧で高アバランシェ耐量を有する窒素化合物半導体素子を提供する。

【解決手段】p−Si基板101上にp−3C−SiC層102が形成された積層構造が形成され、その上にi−GaN層(チャネル層)103、n−AlGaN層(バリア層)104が形成されている。n−AlGaN層104上には、ソース電極201、ドレイン電極202、及びゲート電極203が形成されている。ソース電極201とドレイン電極202は、n−AlGaN層104とオーミックコンタクトを形成している。ゲート電極203は、n−AlGaN層104とショットキー接合を形成している。

(もっと読む)

シリコンカーバイド静電誘導トランジスタ

【課題】 ドリフト層(電圧保持層)10を共通化して逆並列ダイオードを内蔵したシリコンカーバイド静電誘導トランジスタ(SiC−SIT)を実現する。

【解決手段】 ソース領域11の第1側面の溝19の底面から側面に沿ってゲート領域12を形成し、第1側面(片側)からの空乏層の伸縮のみでチャネル17の幅を制御し、トランジスタ電流Itをオン/オフ制御するスイッチング素子を構成する。一方、第2側面の溝20の底面から側面に沿いソース領域11の表面に亘ってソース電極18を形成し、このソース電極18とドリフト層10との間にショットキー接合21を形成し、このショットキー接合21からドレイン領域15へ、ドリフト層10を共通化して電流Idを流すダイオードを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】低オン抵抗のスイッチ素子を低コストで実現する。

【解決手段】第一導電型の半導体基体であるN+型SiC基板2及びN−型ドレイン領域1と、N+型SiC基板2の第一主面側に、電流のオン、オフを切り替えるスイッチ機構とを有する半導体装置において、N−型ドレイン領域1中に、該N−型ドレイン領域1とはバンドギャップの異なるP+型ポリシリコンで形成され、第一主面と、該第一主面と対向する第二主面との間で伸びる柱状のヘテロ半導体領域4が、間隔を置いて並んで複数形成されている。

(もっと読む)

ソース領域下に埋込みn型およびp型領域を有するトランジスタ、およびその製造方法

本発明は、金属半導体電界効果トランジスタ(MESFET)のユニットセルを提供する。MESFETのユニットセルは、ソース、ドレイン、およびゲートを含む。ソースとドレインとの間の、n型導電チャネル層上にゲートを配設する。ソースの下に、ドレインの方に延びる端部を有するp型導電領域を設ける。このp型導電領域は、n型導電チャネル領域から間隔を置いて配置され、ソースに電気的に結合される。ソース領域の下のp型導電領域上に、ドレイン領域の方に延びるが、p型導電領域の端部を越えては延びないn型導電領域を設ける。MESFETを製造する関連した方法も、提供される。  (もっと読む)

(もっと読む)

双方向型電界効果トランジスタおよびマトリクスコンバータ

【課題】単一のデバイスで双方向に流れる電流を制御できる双方向型電界効果トランジスタおよびこれを用いたマトリクスコンバータを提供する。

【解決手段】双方向型電界効果トランジスタは、半導体基板1と、半導体基板1上に設けられ、該基板1の主面に平行なチャネルと該チャネルのコンダクタンスを制御するためのゲート電極13aとを含むゲート領域と、チャネルの第1端側に設けられた第1領域と、チャネルの第2端側に設けられた第2領域とを備え、第1領域の第1電極11aからチャネルを介して第2領域の第2電極12aへ流れる順方向電流および第2電極12aからチャネルを介して第1電極11aへ流れる逆方向電流が、ゲート電極13aに印加されるゲート電圧によって制御される。

(もっと読む)

半導体装置

【課題】基板強度を保持しつつオン抵抗を低減し得る半導体装置を提供する。

【解決手段】網目状の凸部により形成された複数の凹部を裏面に有し、第1の不純物濃度を有する半導体からなる支持体21と、前記支持体の前記裏面に対向する表面に形成され、前記第1の不純物濃度よりも低い第2の不純物濃度を有する半導体層3と、前記半導体層3に形成された半導体素子とを具備することを特徴とする。

(もっと読む)

半導体装置

【課題】 III-V族窒化物半導体層をチャネル領域とする電界効果トランジスタにおけるオン抵抗の低減とドレイン耐圧の向上とを同時に実現できるようにする。

【解決手段】 半導体装置は、窒化ガリウムからなる動作層12と、該動作層12の上に形成された窒化アルミニウムガリウムからなる障壁層13と、該障壁層13の上に互いに間隔をおいて形成されたソース電極14及びドレイン電極15と、両電極14、15の間に形成されたゲート電極とを有している。障壁層13におけるソース電極14とゲート電極16との間の領域には高濃度のn型不純物領域13aが形成されており、ソース電極14、ドレイン電極15及びゲート電極16が互いに等電位である状態において、障壁層13におけるソース電極14とゲート電極16との間の電子濃度は、ドレイン電極15とゲート電極16との間の電子濃度よりも高くなる。

(もっと読む)

パワー半導体素子

【解決手段】ノンドープGaNからなるチャネル層(1)と、チャネル層(1)の表面上に形成されたn型のAl0.2Ga0.8Nからなるバリア層(2)と、バリア層(2)上に選択的に形成されたp型のAl0.1Ga0.9Nからなる半導体層(3)と、半導体層(3)の両側のうちの一方側に位置するバリア層(2)上に形成されたドレイン電極(4)と、少なくとも半導体層(3)とドレイン電極(4)との間で半導体層(3)に隣接する位置のバリア層(2)上に形成された絶縁膜(7)と、絶縁膜(7)上に形成されたフィールドプレート電極(8)とを有するパワー半導体素子。  (もっと読む)

(もっと読む)

半導体装置

【課題】 低オン抵抗化を実現し、高速スイッチングが可能なJFETやSITなどの炭化珪素半導体装置を提供する。

【解決手段】 トレンチ溝110〜113に沿って形成したゲート領域13間のチャネルに拡がる空乏層により電流をオンオフするJFETやSITにおいて、半導体基体表面あるいはトレンチ溝113の底部に、外部より電圧が供給可能なゲートコンタクト層102とゲート電極103を設け、これとは独立し、トレンチ溝110〜112の底部で、ゲート領域13のp++コンタクト層14にオーミック接触するメタル導電部(仮想ゲート電極)101を設ける構造とした。この仮想ゲート電極101は、ゲート電極103や外部配線とは絶縁された形となる。

【効果】 ゲート抵抗を小さくし、高速スイッチング動作が可能な大電流容量の炭化珪素半導体装置を得ることができる。

(もっと読む)

半導体装置

【課題】 高温で動作可能な測温ダイオードを内蔵し、高温環境下で用いることができる炭化珪素半導体装置を提供すること。

【解決手段】 静電誘導トランジスタとして、溝部110,111を制御領域12,14に利用する構造を採る場合、制御層間距離によってノーマリオフ型とすることができる。このノーマリオフを素子間分離として用い、炭化珪素と多結晶シリコンとのヘテロ接合ダイオード114(又はpn接合ダイオード)を構成する。

また、深いp型の第3層30を接地することによっても、素子間分離を達成し、この内側のn型第4層と基体他面との間に測温ダイオードを造り込むことができる。

(もっと読む)

ソース領域の下にp型埋込み層を備えたトランジスタ及びその作製方法。

本発明は、金属半導体電界効果トランジスタ(MESFET)を提供する。このMESFETは、ソース(13)とドレイン(17)とゲート(24)とを備えている。このゲート(24)を、ソース(13)とドレイン(17)の間及びn導電型チャネル層(18)上に設ける。ドレイン(17)に向かって延びている端部を備えるp導電型領域(14)をソースの下に設ける。このp導電型領域(14)をn導電型チャネル領域(18)から隔ててソース(13)に電気的に結合させる。  (もっと読む)

(もっと読む)

半導体装置

【課題】 従来の半導体装置では、ゲート領域から注入された自由キャリア(正孔)がソース領域に取り込まれ、所望のhFEを得られ難いという問題があった。

【解決手段】 本発明の半導体装置では、ソース領域6と同電位となる固定電位絶縁電極11とゲート領域7と同電位となる可変電位絶縁電極9とを有する。そして、固定電位絶縁電極11を介してチャネル領域12を空乏層で満たし、ON動作、OFF動作状態を成す。一方、可変電位絶縁電極を利用し、自由キャリア(正孔)のポテンシャルエネルギーを積極的に可変することで、所望のhFEやスイッチング特性を得ることができる。

(もっと読む)

電界効果トランジスタ

電界効果トランジスタは、GaNチャネル層12とAlGaN電子供給層13を含む半導体層構造と、電子供給層13上に互いに離間して形成されたソース電極1およびドレイン電極3と、ソース電極1とドレイン電極3との間に形成されたゲート電極2と、電子供給層13上に形成されたSiON膜23とを有している。ゲート電極2は、ドレイン電極3側にひさし状に張り出し、かつSiON膜23上に形成されたフィールドプレート部5を有している。SiON膜23のフィールドプレート部5と電子供給層13との間に位置する部分(フィールドプレート層23a)の厚さが、ゲート電極2からドレイン電極3の方向に向かって次第に厚くなるように変化している。 (もっと読む)

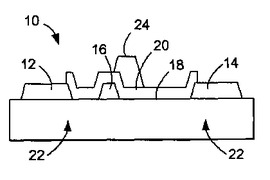

フィールドプレートを有するワイドバンドギャップトランジスタデバイス

活性層との電気的コンタクトで形成された金属のソースおよびドレインコンタクト(20,22)を有する活性半導体層を備えるトランジスタ構造。ゲートコンタクト(26)が、活性層内の電界を変調するためにソースコンタクトとドレインコンタクトとの間に形成されている。スペーサ層(24)が、活性層の上に形成されている。導電性フィールドプレート(28)がスペーサ層の上に形成され、ゲートコンタクトの端からドレインコンタクトに向かって距離Lf延びている。フィールドプレートは、ゲートコンタクトに電気的に接続されている。

(もっと読む)

(もっと読む)

シングルゲートまたはマルチゲートフィールドプレート製造

電界効果型トランジスタの表面に、誘電性材料の堆積/成長させ、誘電性材料をエッチングし、および、メタルを蒸着させる、連続的なステップを用いる、シングルゲートまたはマルチゲートプレートの製造プロセス。本製造プロセスのは、誘電性材料の堆積/成長が、典型的には、非常によく制御できるプロセスなので、フィールドプレート動作を厳しく制御できる。さらに、デバイス表面に堆積された誘電性材料は、デバイスの真性領域から除去される必要はない。このため、乾式または湿式のエッチングプロセスで受けるダメージの少ない材料を用いることなく、フィールドプレートされたデバイスを、実現することができる。マルチゲートフィールドプレートを使うと、マルチ接続を使用するので、ゲート抵抗を減らすこともでき、こうして、大周辺デバイスおよび/またはサブミクロンゲートデバイスの性能を向上することができる。  (もっと読む)

(もっと読む)

集積化電子切断回路、方法およびシステム

過渡現象遮断用の組み合わせデバイス。過渡現象が入力端子 40に印加されると、トランジスタ 44のボディ電位がデプレッションモードJFET型遮断トランジスタ 71のゲート 81を駆動するように、パストランジスタ44が配置されている。同時に、チャネル77を空乏化するために、電位差 Vdが外部ゲート 52の両端に印加される。このように、外部端子上に現れる過渡現象は、非常に急速に伝播されて、チャネル 77および85を空乏化するので、出力端子42に接続されたデバイスが故障する前に、入力端子 40を出力端子 42から効果的に分離する。一旦過渡現象がおさまると、デバイス 37はその通常の導通状態に戻る。 (もっと読む)

161 - 176 / 176

[ Back to top ]