Fターム[5F102GR11]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 非対称構造 (606)

Fターム[5F102GR11]の下位に属するFターム

S−G電極間とD−G電極間の距離が異なるもの (319)

ソースとドレインの形状、不純物濃度が異なるもの (111)

Fターム[5F102GR11]に分類される特許

61 - 80 / 176

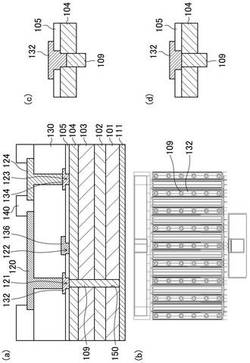

半導体装置及びその製造方法

【課題】III-V族窒化物半導体を有する半導体装置において、熱による出力低下を低減する。

【解決手段】半導体装置は、基板101上に設けられ、III-V族窒化物半導体からなるバッファ層102と、バッファ層102上に設けられ、III-V族窒化物半導体からなる第1の半導体層103と、第1の半導体層103上に設けられ、III-V族窒化物半導体からなる第2の半導体層104と、基板101の裏面上に設けられ、接地に接続された裏面電極111と、第2の半導体層104上に互いに離間して設けられたソース電極132及びドレイン電極134と、第2の半導体層104上に設けられたゲート電極136とと、第2の半導体層104、第1の半導体層103、及びバッファ層102を貫通し、少なくとも基板101に達し、ソース電極132と裏面電極111とを電気的に接続させるプラグ109とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】ドレイン電流コラプスを抑制すること。

【解決手段】窒化物半導体層19上に、ソース電極20、ゲート電極24およびドレイン電極22をそれぞれ形成する工程と、前記窒化物半導体層上に窒化シリコン膜26を形成する工程と、前記ゲート電極と前記ドレイン電極との間の前記窒化シリコン膜の上面をフッ酸を含む溶液を用い処理する工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】出力を大きくすることが可能な半導体装置を提供すること。

【解決手段】半導体基板10上に設けられ、ソースパッド12aと、ソースパッド12aと接続された一端から他端に向けて長さが小さくなる階段状の側部12cを有するソースフィンガー12bと、を含むソース電極12と、ドレインパッド14aと、ドレインパッド14aと接続された一端から他端に向けて長さが小さくなり、側部12cと対向する側部14cを有するドレインフィンガー14bと、を含むドレイン電極14と、ソースフィンガー12bの段差12dと、ドレインフィンガー14bの段差14dとの間に屈曲部16cを有し、ソースフィンガー12a及びドレインフィンガー14aに沿って屈曲するゲート電極16と、を具備し、側部12cの形状と側部14cの形状とは、ソースフィンガー12bの他端とドレインフィンガー14bの他端とを結ぶ線分9の中点に対して対称である半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】2つのオーミック電極、及び、それらの間に配置されたゲート電極を備えた、ゲート電極形成用電子線の揺らぎに起因するゲート電極形成不良が生じない形で製造できる半導体装置を提供する。

【解決手段】半導体装置1の、ゲート電極20により近い方のオーミック電極(ソース電極14s)として、ゲート電極20と対向する側の少なくとも一方の隅(電子線の描画開始位置側の隅)がカットされた矩形形状のものを採用しておく。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタにおいて、フィールドプレート終端での高電界の集中を緩和し、もって高耐圧半導体装置として利用可能とする。

【解決手段】本電界効果トランジスタ30は、GaN系エピタキシャル基板32の電子走行層上に、ゲート電極38を挟んで配置されたソース電極34及びドレイン電極36を備え、ゲート電極38及びソース電極34はドレイン電極36を囲み、ソース電極34の上部に、ゲート電極38の上方を通過してドレイン電極36側に庇状に突き出したフィールドプレート170が形成され、GaN系エピタキシャル基板32の表面層とフィールドプレート170との間に、誘電体膜46が形成され、誘電体膜46は、フィールドプレート170の直下領域においてフィールドプレート終端面と面一状態となるように切れ込み、その下端からドレイン電極36に接続するようにドレイン電極36に向かって延びている。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗が低く耐圧および信頼性が高い電界効果トランジスタを提供する。

【解決手段】基板1上に形成されたキャリア走行層3と、前記キャリア走行層上に形成され前記キャリア走行層よりもバンドギャップエネルギーが高いキャリア供給層4a、4bと、前記キャリア供給層から前記キャリア走行層の表面または内部に到る深さまで形成されたリセス部5と、前記キャリア供給層上に形成されたドレイン電極11と、前記リセス部に形成され、前記ドレイン電極側のキャリア供給層と重畳するように延設したゲート電極7と、前記リセス部の底面と前記ゲート電極との間に形成された第1絶縁膜6と、前記ゲート電極と前記ドレイン電極側のキャリア供給層との間に形成され前記第1絶縁膜よりも誘電率が高い第2絶縁膜8aとを備える。

(もっと読む)

半導体装置

【課題】 表面保護膜中へのホットキャリアの侵入に起因する半導体装置の出力低下を抑制すること。

【解決手段】 本半導体装置100は、窒化ガリウム系半導体からなる電子走行層12と、電子走行層12上に設けられ、窒化ガリウム系半導体からなる電子供給層16と、電子供給層16上に設けられ、窒化ガリウムからなるキャップ層18と、キャップ層18上に設けられたゲート電極24と、電子供給層16上にゲート電極24を挟んで設けられたソース電極20及びドレイン電極22と、キャップ層18上に設けられた表面保護膜30と、キャップ層18と表面保護膜30との間に介在し、少なくともゲート電極24とドレイン電極22との間の領域に設けられたAlxGa1−xN(0.5≦x≦1)からなるバリア層50と、を備える。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプスが小さく且つ良好な高周波特性を有する電界効果トランジスタを実現できるようにする。

【解決手段】電界効果トランジスタは、基板101の上に形成された窒化物半導体積層体102と、ソース電極105、ドレイン電極106及びゲート電極107と、窒化物半導体積層体102の上に形成された絶縁膜110と、絶縁膜110の上に接して形成され、端部がゲート電極107とドレイン電極106との間に位置するフィールドプレート115とを備えている。絶縁膜110は、第1の膜111と、第1の膜111よりも絶縁耐圧が低い第2の膜112とを含み、ゲート電極117とドレイン電極116との間に形成された薄膜部110aを有している。フィールドプレート115は、薄膜部110aを覆い且つ開口部においてソース電極と接続されている。

(もっと読む)

接合型電界効果トランジスタ、その製造方法及びアナログ回路

【課題】外部ノイズの影響を低減できるJFETを提供する。

【解決手段】本発明に係るJFET50は、p型半導体基板1と、p型半導体基板1の表面に形成されているn型チャネル領域3と、n型チャネル領域3内に形成されており、n型チャネル領域3よりも不純物濃度の高いn型埋め込み領域4と、n型チャネル領域3の表面に形成されているp型ゲート領域6と、n型チャネル領域3の表面に、p型ゲート領域6を挟むように形成されているn型ドレイン/ソース領域7及びn型ドレイン/ソース領域8とを備え、n型埋め込み領域4は、n型ドレイン/ソース領域7及びn型ドレイン/ソース領域8の一方の下方に形成されており、他方の下方に形成されていない。

(もっと読む)

窒化物電子デバイス、窒化物電子デバイスを作製する方法

【課題】チャネル層のキャリア濃度が増大することを避けてリークを低減できる構造を有する、窒化物電子デバイスを提供する。

【解決手段】半導体積層15の斜面15a及び主面15cは、それぞれ、第1及び第2の基準面R1、R2に対して延在する。半導体積層15の主面15cは六方晶系III族窒化物のc軸方向を示す基準軸Cxに対して5度以上40度以下の範囲内の角度で傾斜すると共に、第1の基準面R1の法線と基準軸Cxとの成す角度は第2の基準面R2の法線と基準軸Cxとの成す角度より小さいので、チャネル層19の酸素濃度を1×1017cm−3未満にすることができる。これ故に、チャネル層19において、酸素添加によりキャリア濃度が増加することを避けることができ、チャネル層を介したトランジスタのリーク電流を低減できる。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および電子装置

【課題】 ミリ波以上の周波数において、安定して、高い利得および動作周波数が得られる電界効果トランジスタを提供する。

【解決手段】 基板11上の動作層13の上に、ソース電極14、ドレイン電極15、ゲート電極18、絶縁膜17が形成され、

ゲート電極18は、ソース電極14とドレイン電極15の間に配置され、

絶縁膜17は、ゲート電極18とドレイン電極15の間に配置され、

フィールドプレート電極19は、絶縁膜17上に形成され、かつ、ソース電極14と電気的に接続され、

ゲート電極18上部は、ソース電極14側およびドレイン電極15側に突出し、

フィールドプレート電極19下端は、ゲート電極18下端よりも下方に配置され、

フィールドプレート電極19上端は、ゲート電極19上部においてドレイン電極15側に最も突出した部分よりも下方に配置されている電界効果トランジスタ。

(もっと読む)

半導体装置

【課題】本発明は、ゲート電極の端部に発生する電界集中を緩和し、高いオフ耐圧と優れた高周波特性を有する半導体装置を提供するを目的とする。

【解決手段】実施形態によれば、チャネル層3上に互いに離間して設けられ、それぞれがチャネル層3に電気的に接続されたソース電極4およびドレイン電極5と、ソース電極4とドレイン電極5との間においてチャネル層3に接して設けられたゲート電極6と、ゲート電極6とドレイン電極5との間においてチャネル層3上に設けられたパッシベーション膜7と、ゲート電極6に接触し、且つ、ドレイン電極5と離間してパッシベーション膜7上に設けられたパッシベーション膜7よりも誘電率が高い高誘電率膜8と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能で、性能のばらつきが抑制された半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下方から上方に向かって径が連続的に拡大された形状であるとともに、下から順にソース領域17、ゲート領域18、ドレイン領域19からなるとともに、ドレイン領域19は、ソース領域17よりも長く形成され、ソース領域17の周囲には第1の絶縁膜20、ゲート領域18の周囲にはゲート電極21、ドレイン領域19の周囲には第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能で、性能のばらつきが抑制された半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたドレインパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたソースパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下方から上方に向かって径が連続的に拡大された形状であるとともに、下から順にドレイン領域17、ゲート領域18、ドレイン領域17よりも短いソース領域19からなり、ドレイン領域17の周囲には第1の絶縁膜20、ゲート領域18の周囲にはゲート電極21、ソース領域19の周囲には第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

デュアル・デプレションを示す高電子移動度トランジスタ及びその製造方法

【課題】デュアル・デプレションを示す高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】互いに異なる極性を有する複数の半導体層20,22を含み、ソース電極28とドレイン電極32との間にデュアル・デプレション領域が存在し、該複数の半導体層は、上部物質層26、中間物質層22、下部物質層20を含み、中間物質層の極性は、上部物質層及び下部物質層の極性と異なる高電子移動度トランジスタである。

(もっと読む)

窒化物電子デバイスを作製する方法

【課題】ゲートリーク電流を低減できる、窒化物電子デバイスを作製する方法を提供する。

【解決手段】時刻t0で基板生産物を成長炉に配置した後に、摂氏950度まで基板温度を上昇する。基板温度が十分に安定した時刻t3でトリメチルガリウム及びアンモニアを成長炉に供給して、i−GaN膜を成長する。時刻t5で基板温度が摂氏1080度に到達する。基板温度が十分に安定した時刻t6でトリメチルガリウム、トリメチルアルミニウム及びアンモニアを成長炉に供給して、i−AlGaN膜を成長する。時刻t7でトリメチルガリウム及びトリメチルアルミニウムの供給を停止して成膜を停止した後に、速やかに、成長炉へアンモニア及び水素の供給を停止すると共に窒素の供給を開始して、成長炉のチャンバ中においてアンモニア及び水素の雰囲気を窒素の雰囲気に変更する。窒素の雰囲気が形成された後に、時刻t8で基板温度の降下を開始する。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 サージ電圧等に対するバイパス用の保護部を備え、耐圧性能および低いオン抵抗(低いオン電圧)を実現し、かつ、構造が簡単な、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】 支持基体上にオーミック接触するGaN層を有するn+型GaN基板1と、第1領域R1上におけるn−型GaNドリフト層2を有するFETと、第2領域R2においてn−型GaNドリフト層2にショットキー接触するアノード電極を有するSBDとを備え、FETとSBDとは並列配置されており、n+型GaN基板1の裏面に、FETのドレイン電極DおよびSBDのカソード電極Cを備えることを特徴とする。

(もっと読む)

金属キャリアを有する半導体デバイスおよび製造方法

【課題】 金属キャリアを有する半導体デバイス及び製造方法を提供する。

【解決手段】 金属キャリア基板を含む半導体デバイス。キャリア基板の上には、Alx1Gay1Inz1N(x1+y1+z1=1、x1≧0、y1≧0、z1≧0)の第1の半導体層が形成される。第1の半導体層の上にはAlx2Gay2Inz2N(x2+y2+z2=1、x2>x1、y2≧0、z2≧0)の第2の半導体層が配され、第2の半導体層の上にはゲート領域が配置される。半導体デバイスはさらに、ソース領域およびドレイン領域を含み、これらの領域のうちの一方が金属キャリア基板と電気的に接続され、第1の半導体層を介して延在する導電性領域を含む。

(もっと読む)

半導体装置

【課題】GaN電子走行層、AlGaN電子供給層、およびGaNキャップ層が順次積層された半導体装置において、高周波数動作および高出力動作を実現することが可能な半導体装置を提供すること。

【解決手段】本発明は、基板10上に順次積層されたGaN電子走行層12、AlGaN電子供給層14、およびGaNキャップ層16と、GaNキャップ層16上に形成されたゲート電極18と、ゲート電極18の両側であって、AlGaN電子供給層14上に形成されたソース電極20およびドレイン電極22と、ゲート電極18とソース電極20との間のGaNキャップ層16に形成された第1の凹部30と、を具備し、第1の凹部30が有する底面32下におけるGaNキャップ層16の厚さは、ゲート電極18下におけるGaNキャップ層16の厚さに比べて薄い半導体装置である。

(もっと読む)

61 - 80 / 176

[ Back to top ]