Fターム[5F102GR11]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 非対称構造 (606)

Fターム[5F102GR11]の下位に属するFターム

S−G電極間とD−G電極間の距離が異なるもの (319)

ソースとドレインの形状、不純物濃度が異なるもの (111)

Fターム[5F102GR11]に分類される特許

41 - 60 / 176

窒化物半導体素子の製造方法

【課題】ドレインリーク電流を低減することが可能な窒化物半導体素子の製造方法を提供する。

【解決手段】ヘテロ電界効果トランジスタ1の製造方法は、ドリフト層20aを支持基板10上にエピタキシャル成長させる工程と、水素ガスをキャリアガスとして用いて、p型半導体層である電流ブロック層20bをドリフト層20a上に1000℃以上でエピタキシャル成長させる工程と、窒素ガス、アルゴンガス、ヘリウムガス及びネオンガスからなる群より選ばれる少なくとも一種のガスをキャリアガスとして用いて、コンタクト層20cを電流ブロック層20b上にエピタキシャル成長させる工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】電界集中を緩和させることにより、高耐圧、高信頼性を得ることが可能な半導体装置とその製造方法を提供する。

【解決手段】本発明の実施形態は、半導体基板と、半導体基板上に設けられるゲート電極と、ゲート電極を挟んで半導体基板上に設けられるソース電極及びドレイン電極と、ゲート電極の少なくともドレイン電極側のエッジの下部に設けられるリセスと、を備える。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】半導体装置において、セルフターンオンが発生しないようにし、安定した動作を実現する。

【解決手段】半導体装置を、基板1と、基板の上方に設けられ、電子走行層6及び電子供給層7を含む半導体積層構造2と、半導体積層構造の上方に設けられたゲート電極3、ソース電極4及びドレイン電極5と、ゲート電極、ソース電極及びドレイン電極の上方に設けられ、ゲート電極、ソース電極及びドレイン電極のそれぞれに接続されたゲートパッド10、ソースパッド11及びドレインパッド12と、ゲートパッド、ソースパッド及びドレインパッドの下方に設けられた導電層1とを備えるものとし、ゲートパッドとソースパッドとの間の距離を、ゲートパッドとドレインパッドとの間の距離よりも小さくする。

(もっと読む)

炭化珪素半導体装置

【課題】従来よりオン抵抗が低くかつ高い耐圧を有する炭化珪素半導体装置を提供する。

【解決手段】この発明に従ったJFET10は、n型基板11と、p型層2、12と、n型層13と、ソース領域15と、ドレイン領域17と、ゲート領域16とを備える。n型基板11は、{0001}面に対するオフ角が32°以上である主表面11Aを有し、炭化珪素(SiC)からなる。p型層2、12は、n型基板11の主表面11A上に形成され、導電型がp型である。n型層13は、p型層2、12上に形成され、導電型がn型である。ソース領域15およびドレイン領域17は、n型層13において、互いに間隔を隔てて形成され、導電型がn型である。ゲート領域16は、n型層13において、ソース領域15とドレイン領域17との間の領域に形成され、導電型がp型である。

(もっと読む)

半導体装置およびその製造方法

【課題】 開口部が設けられ、当該開口部に二次元電子ガスで形成されるチャネルを備える縦型半導体装置の耐圧性能を向上させることを目的とする。

【解決手段】 GaN系積層体15は、n−型GaNドリフト層4/p型GaNバリア層6/n+型GaNコンタクト層7、を有し、開口部28は表層からn−型GaNドリフト層4内にまで届いていて、開口部の壁面および底部を覆うように位置する、電子走行層22および電子供給層26を含む再成長層27と、開口部の周囲に位置するソース電極Sと、開口部の再成長層上に位置するゲート電極Gと、開口部の底部に位置する底部絶縁膜37とを備えることを特徴とする。

(もっと読む)

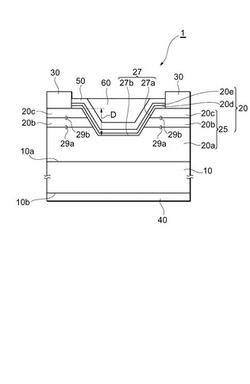

半導体装置およびその製造方法

【課題】開口部にチャネルを備える縦型半導体装置において、高周波特性を向上することができる半導体装置およびその製造方法を提供する。

【解決手段】 n型GaN系ドリフト層4/p型GaN系バリア層6/n型GaN系コンタクト層7、を有し、開口部28は表層からn型GaN系ドリフト層内にまで届いており、該開口部を覆うように位置する電子走行層22および電子供給層26を含む再成長層27と、ソース電極Sと、ドレイン電極Dと、再成長層上に位置するゲート電極Gとを備え、ソース電極を一方の電極とし、またドレイン電極を他方の電極としてコンデンサを構成するとみて、該コンデンサの容量を低下させる容量低下構造を備えることを特徴とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ファインゲート構造を採用してゲート電極の微細化を図るも、ゲート電極の周辺における電界集中によるデバイス特性の変動・劣化を防止する、信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極8は、ファインゲート構造の幹状の下方部分8aと、下方部分8aの上端から当該上端よりも幅広に傘状(オーバーハング形状)に拡がる上方部分8bとが一体形成されており、下方部分8aは、下端を含む第1の部分8aaと、第1の部分8aa上の第2の部分8abとを有し、保護壁7は、第1の部分8aaの両側面のみを覆うように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 開口部が設けられ、当該開口部に二次元電子ガスで形成されるチャネルを備える縦型半導体装置の耐圧性能を向上させることを目的とする。

【解決手段】開口部28が設けられたGaN系積層体15を備える縦型の半導体装置であって、n型GaN系ドリフト層4/p型GaN系バリア層6/n型GaN系コンタクト層7、を備え、開口部を覆うように電子走行層22および電子供給層26を含む再成長層27と、ソース電極Sと、再成長層上に位置するゲート電極Gとを備え、ゲート電極Gは、p型GaNバリア層の厚み範囲に対応する部分を覆い、かつ開口部の底部から離れた位置の壁面内で終端している。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタをより高速に動作させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の一態様には、基板1と、基板1の上方に形成された電子走行層3及び電子供給層4を備えたトランジスタと、基板1の上方に形成され、トランジスタのゲート11gに接続された窒化物半導体層7及び8と、窒化物半導体層7及び8を移動する電荷を制御する制御手段12、13、11s、及び16と、が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、SBD、HEMT等のデバイスに逆方向電圧をかけたときの電極端部に生じる電界集中を緩和して電流コラプス、及び長期信頼性の問題を解決した半導体装置を提供する。

【解決手段】窒化物化合物半導体層を有する電子走行層11と、前記電子走行層11に形成された窒化物化合物半導体からなる電子供給層12と、前記電子供給層12上に形成された第1電極13と、前記電子供給層12上に前記第1電極13と離間して形成された第2電極14と、前記電子走行層11および前記電子供給層12を挟んで前記第1電極13に対向して形成された、前記第1電極13と同電位の第1導電体14と、前記電子走行層11および前記電子供給層12を挟んで前記第2電極14に対向して形成された、前記第2電極14と同電位の第2導電体16とを有する半導体装置1を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】 縦型GaN系半導体装置において、p型GaNバリア層による耐圧性能の向上を得ながら、オン抵抗を低くできる半導体装置を提供する。

【解決手段】 開口部28壁面に位置するチャネルを含む再成長層27と、端面が被覆されるp型バリア層6と、p型バリア層上に接するソース層7と、再成長層の上に位置するゲート電極Gと、開口部の周囲に位置するソース電極Sとを備え、ソース層が超格子構造で構成され、該超格子構造が、p型バリア層よりも小さい格子定数を持つ第1の層(a層)と、該第1の層よりも格子定数が大きい第2の層(b層)との積層体である、ことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 ピンチオフ特性を改善しまたはチャネル層の移動度を向上させ電気的特性の良好な半導体装置の製造方法を提供すること。

【解決手段】基板10上にGaN系半導体層20を形成する工程と、前記GaN系半導体層に開口部28を形成する工程と、前記開口部の側面に電子走行層22および電子供給層26を形成する工程と、前記電子供給層の前記開口部側の側面にゲート電極32を形成する工程と、前記GaN系半導体層上にソース電極30を形成する工程と、前記GaN系半導体層の前記ソース電極と相対する面に接続するドレイン電極34を形成する工程と、を具備する半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】低いオン抵抗を得ながら、優れた耐圧性能を持つ、縦型の半導体装置およびその製造方法を提供する。

【解決手段】開口部28はn−型GaNドリフト層4にまで届いており、開口部の壁面を覆うように位置する再成長層27と、p型GaNバリア層6と、ゲート電極Gと、ソース電極Sとを備え、チャネルが電子走行層22内の電子供給層26との界面に生じる二次元電子ガスにより形成され、p型GaNバリア層6がGaN系積層体15の表層をなし、かつソース電極Sが、再成長層27およびp型GaNバリア層6に接して位置することを特徴とする。

(もっと読む)

ソース領域の下にp型埋込み層を備えたトランジスタ及びその作製方法

【課題】本発明は、金属半導体電界効果トランジスタ(MESFET)を提供する。

【解決手段】このMESFETは、ソース(13)とドレイン(17)とゲート(24)とを備えている。このゲート(24)を、ソース(13)とドレイン(17)の間及びn導電型チャネル層(18)上に設ける。ドレイン(17)に向かって延びている端部を備えるp導電型領域(14)をソースの下に設ける。このp導電型領域(14)をn導電型チャネル領域(18)から隔ててソース(13)に電気的に結合させる。

(もっと読む)

接合型電界効果トランジスタを備えた半導体装置およびその製造方法

【課題】埋込ゲート層とゲート配線とのコンタクト構造をより微細化できる構造としたJFETを有する半導体装置を提供する。

【解決手段】埋込ゲート層10とゲート配線12との電気的な接続をトレンチ13内に形成したp+型コンタクト埋込層14によって行うようにする。これにより、p+型コンタクト埋込層14のみしか配置されないトレンチ13の幅を、従来の半導体装置のように層間絶縁膜やゲート配線などが配置されるトレンチと比較して、狭くすることが可能となる。したがって、埋込ゲート層10とゲート配線12とのコンタクト構造をより微細化できる構造としたJFETを有する半導体装置とすることが可能となる。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】低オン抵抗の電界効果トランジスタを低コストで実現する。

【解決手段】電界効果トランジスタは、第一導電型の半導体基体であるN+型SiC基板2及びN-型ドレイン領域1と、N+型SiC基板2の第一主面側に、P型ウエル領域3とN+型ソース領域5とゲート電極7とを有する。N-型ドレイン領域1中に、N-型ドレイン領域1とはバンドギャップの異なるP+型ポリシリコンで形成され、第一主面から第二主面へ向かって伸びる柱状のヘテロ半導体領域4が、間隔を置いて並んで複数形成されている。ゲート電極7直下にチャネル領域が形成されないときに、N-型ドレイン領域1がヘテロ半導体領域4と接することによりN-型ドレイン領域1の全域が空乏化される。

(もっと読む)

電界効果トランジスタ

【課題】 本発明は、低消費電力で動作する論理回路に応用できる電界効果トランジスタを提供することを目的とするものである。

【解決手段】 ソース電極とソース電極が接する半導体の伝導帯又は価電子帯との間に障壁を有しており、ソース電極から障壁を通して流れ込む電子又はホールをゲート電圧により調整できる構成を有することを特徴とするnチャンネル又はpチャンネルの電界効果トランジスタ。

(もっと読む)

化合物半導体装置

【課題】窒化物化合物半導体装置において、ゲートリーク電流を抑制する。

【解決手段】化合物半導体装置20は、基板21と、前記基板上方に形成された窒化物半導体よりなるキャリア走行層22を含む半導体積層構造と、前記半導体積層構造上方に形成されたゲート電極26、ソース電極27A、ドレイン電極27Bと、前記半導体積層構造上方であって、ゲート電極とソース電極の間、及び、ゲート電極とドレイン電極との間に形成された絶縁膜28と、前記絶縁膜のうち、ゲート電極とソース電極の間、及びゲート電極とドレイン電極の間に形成された開口と、前記開口に埋め込まれたアルミナ膜29と、を備える。

(もっと読む)

ヘテロ接合電界効果トランジスタ及びその製造方法

【課題】電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明に係るヘテロ接合電界効果トランジスタは、バリア層40及びバリア層40上に形成されたキャップ層50を含む窒化物半導体層と、前記窒化物半導体層に下部を埋没するようにして前記窒化物半導体層上に設けられたゲート電極90と、前記窒化物半導体層上に形成されたSiを含まない絶縁膜からなる表面保護膜100とを備える。

(もっと読む)

半導体装置の製造方法

【課題】高周波領域において優れた電気的特性が得られるように、寄生容量を低減し得る半導体装置の製造方法を得る。

【解決手段】第1のソース電極、ゲート電極、ドレイン電極、及び第2のソース電極が、所定方向に沿ってこの順に並んで半導体基板の上面上に形成された構造を有するトランジスタを形成する。犠牲層を、トランジスタを覆って半導体基板の上面上に形成する。犠牲層を部分的に除去することにより、第1のソース電極及び前記第2のソース電極を露出する。第1のソース電極及び第2のソース電極に接続され、所定方向に沿って延在する配線を、犠牲層の上面上に形成する。犠牲層を除去する。上面が開口した枠体を、トランジスタの周囲を取り囲んで、半導体基板の上面上に形成する。枠体上にテープを貼り付けることにより、枠体及びテープによってトランジスタ及び配線を覆う。

(もっと読む)

41 - 60 / 176

[ Back to top ]