Fターム[5F102GR11]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 非対称構造 (606)

Fターム[5F102GR11]の下位に属するFターム

S−G電極間とD−G電極間の距離が異なるもの (319)

ソースとドレインの形状、不純物濃度が異なるもの (111)

Fターム[5F102GR11]に分類される特許

101 - 120 / 176

窒化物半導体装置およびその製造方法

【課題】緩衝層を介したリーク電流の増加を抑制して、特性の劣化を防止した窒化物半導体装置を提供する。

【解決手段】AlGaN層4に、インシュレータ領域8Aを有する。このため、熱や衝撃などで緩衝層2に歪みが生じて、緩衝層2に電流が流れ易くなっても、図1中の点線の矢印aに示すように、インシュレータ領域8Aにより電流の流れを阻止することで、緩衝層2を介したリーク電流の増加を抑制して、特性の劣化を防止できる。

(もっと読む)

半導体チップ

【課題】熱抵抗の低減と寄生容量の低減を同時に実現できる半導体チップを提供する。

【解決手段】ドレインフィンガー3及びソースフィンガー2の下部の半導体領域のうち、ゲートフィンガー1の近傍のみに熱抵抗低減用のドーピング領域4を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】フィールドプレートを設けることによって、半導体装置のゲート電極及びドレイン電極間における電解集中を、効率良く緩和する。

【解決手段】下地11と、この下地の下地面11aに、互いに離間しかつ対向して形成された第1及び第2主電極29a及び29bを具えている。また、下地面に、第1及び第2主電極間に挟み込まれて形成されたゲート電極27を具えている。さらに、ゲート電極と第1主電極との間に露出した下地面には、第1下地面保護膜31aが形成されている。また、ゲート電極と第2主電極との間に露出した下地面には、第2下地面保護膜31bが形成されている。そして、ゲート電極の上側表面27aから、このゲート電極の第2主電極と対向する側の側面27b、第2下地面保護膜に渡って、一体的に被覆するフィールドプレート43が形成されている。さらに、フィールドプレートと第2下地面保護膜との境界面47は、下地面側に凸状に湾曲している傾斜面である。

(もっと読む)

窒化物半導体素子

【課題】本発明は、低オン抵抗でノーマリーオフ型の窒化物半導体素子を提供する。

【解決手段】本発明の一態様によれば、p型窒化物半導体の第1の半導体層と、第1の半導体層上に設けられたアンドープ窒化物半導体の第2の半導体層と、第2の半導体層上に選択的に設けられたアンドープまたはn型窒化物半導体の第3の半導体層と、第3の半導体層上に設けられた第1の主電極と、第3の半導体層上に設けられた第2の主電極と、第2の半導体層上に設けられた絶縁膜と、絶縁膜上に設けられた制御電極と、を備え、第3の半導体層のバンドギャップは、第2の半導体層のバンドギャップよりも大きく、制御電極は、第1の主電極と第2の主電極との間に位置することを特徴とする窒化物半導体素子が提供される。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜におけるリーク電流を抑制し、安定なFET特性を得ること。

【解決手段】本半導体装置の製造方法は、基板上10にGaN系半導体層15を形成する工程と、GaN系半導体層上15に、TMAと、O2またはO3とを用い、酸化アルミニウムからなるゲート絶縁膜18をALD法により形成する工程と、ゲート絶縁膜18の上にゲート電極24を形成する工程と、を含む。本半導体装置の製造方法によれば、ゲート絶縁膜中のリーク電流を抑制し、安定なFET特性を得ることができる。

(もっと読む)

化合物半導体電界効果トランジスタ及びその製造方法

【課題】化合物半導体電界効果トランジスタの高集積化及び高電力化を図る。

【解決手段】角柱状又は角錐台状の、オン状態のときに軸方向に電流が流れる半導体部43と、半導体部の周囲に、第1絶縁層50、制御電極層60及び第2絶縁層72が、半導体部の軸方向に沿って順に積層された周辺部とを備える。半導体部が、角柱状又は角錐台状の電子走行部44と、電子走行部の側面44c上に形成された電子供給部46とを備えて構成される。

(もっと読む)

炭化ケイ素半導体装置および炭化ケイ素半導体装置の製造方法

【課題】チャネルの低い抵抗を維持するとともに、ドリフト層の高い耐圧を維持するSiC半導体装置およびSiC半導体装置の製造方法を提供する。

【解決手段】SiC半導体装置は、SiC基板101、第1半導体層、ベース領域105、第2半導体層、ゲート領域109およびソース領域113を備えている。SiC基板101は、{0001}面に対して30°以上60°以下傾斜した主面101aを有する。第1半導体層は、主面101a上に形成される。ベース領域105は、表面103aの一部に形成される。第2半導体層は、表面103a上に形成される。ゲート領域109は、表面107aの一部に形成され、第2半導体層を挟んでベース領域105と対向する位置に形成される。ソース領域113は、表面107aの一部に形成され、ゲート領域109と隣り合い、かつベース領域105と対向する位置に形成される。

(もっと読む)

半導体装置

【課題】ノーマリーオフ動作を実現でき且つ低オン抵抗な絶縁ゲート構造の半導体装置を提供する。

【解決手段】本発明の半導体装置は、第1の窒化物半導体を含む第1の半導体層1と、第1の半導体層1上に設けられ第1の窒化物半導体よりもバンドギャップが広い第2の窒化物半導体を含む第2の半導体層2と、第2の半導体層2に接続された第1の主電極3と、第2の半導体層2に接続された第2の主電極4と、第1の主電極3と第2の主電極4との間の第2の半導体層2表面に接して設けられたフローティング電極5と、フローティング電極5上に設けられたゲート絶縁膜7と、ゲート絶縁膜7上に設けられた制御電極8と、フローティング電極5と第1の主電極3との間およびフローティング電極5と第2の主電極4との間の第2の半導体層2表面上に設けられたフィールド絶縁膜6とを備えた。

(もっと読む)

半導体装置及びその製造方法

【課題】MIS−HEMTにおいて、閾値電圧の低下を抑制する。

【解決手段】半導体装置は、基板19と、この基板上に形成されており、電子走行層13及び電子供給層15が順次積層されて形成された積層構造体17とを含む下地11を具えている。この下地の下地面には、互いに離間し、かつ対向して第1及び第2主電極が形成されている。そして、下地面11aの、これら第1主電極41a及び第2主電極41b間に挟まれた領域内に、ゲート形成用凹部27が形成されている。更に、半導体装置はゲート絶縁膜29を具えている。そして、このゲート絶縁膜は、最小でも2.9g/cm3の結晶密度で形成されている。また、半導体装置は、ゲート絶縁膜が形成された前記ゲート形成用凹部を埋め込むゲート電極43を具えている。

(もっと読む)

III族窒化物系化合物半導体基板とその製造方法

【課題】平面視したときに限定された範囲にp型領域が形成されているIII族窒化物系化合物半導体基板であり、p型領域とその周囲の領域との間に段差がない基板を提供する。

【解決手段】 III族窒化物系化合物半導体下層6の表面にIII族窒化物系化合物半導体を結晶成長させるに先立って、p型領域12を形成したい範囲に相当する範囲内の下層6の表面近傍にマグネシウムとアルミニウムの双方を含ませておく。下層6の限られた範囲の表面近傍にマグネシウムとアルミニウムの双方が含まれていると、その上に上層16を結晶成長したときに、結晶成長する上層16の限られた範囲にマグネシウムが移動してp型領域12になるともに、下層6に含まれているアルミニウムがマグネシウムの移動範囲を制約し、下層6におけるマグネシウムの含有範囲10と上層16におけるマグネシウムの含有範囲12をよく一致させる。

(もっと読む)

伝導を高めた非パンチスルー半導体チャネルを有する半導体デバイス及びその製法

デバイスにおける電流フローが整流接合(例えば、p−n接合又は金属半導体接合)の間で制限される、半導体デバイスが記載される。デバイスは、非パンチスルー挙動と高められた電流伝導能力を提供する。デバイスは、接合型電界効果トランジスタ(JFETs)、静電誘導トランジスタ(SITs)接合型電界効果サイリスタ、又はJFET電流制限器などのような電力半導体デバイスである。デバイスは、炭化ケイ素(SiC)等の広バンドギャップでできている。いくつかの実施形態において、デバイスは、常時オフ型SiC垂直接合型電界効果トランジスタである。デバイス及びデバイスを備える回路を製造する方法もまた記載される。 (もっと読む)

半導体装置

【課題】窒化物系半導体機能層に生成される二次元キャリアガスチャネルにおいてキャリア密度及び電界をキャリア走行方向に変調する半導体装置を提供する。

【解決手段】半導体装置(HEMT)1において、第1の窒化物系半導体領域21上に第2の窒化物系半導体領域22を有する窒化物系半導体機能層2と、窒化物系半導体機能層2上に互いに離間されて配設された第1の主電極3及び第2の主電極4と、窒化物系半導体機能層2上の第1の主電極3と第2の主電極4との間に配設されたゲート電極5とを備え、第2の窒化物系半導体領域22の第1の主電極3側の膜厚に対して第2の主電極4側の膜厚が異なる。

(もっと読む)

半導体装置

【課題】基板の結晶面方位を規定して表面の微細な凹凸を抑制した炭化珪素基板上のエピタキシャル相に半導体装置を形成することによって、その電気的特性を改善する。

【解決手段】炭化珪素半導体基板上に形成する半導体装置として、基板の(000−1)面から0°超で以上1°未満傾斜した面上に成長したエピタキシャル層に、P型あるいはN型領域をイオン注入により選択的に形成して製造したダイオード、トランジスターなどとする。

(もっと読む)

半導体装置及びその製造方法

【課題】細く深いバイアホールが設けられる場合でも、ソースインダクタンスを十分に低減し、高い放熱効率を得ることができる半導体装置及びその製造方法を提供する。

【解決手段】SiC基板1上に化合物半導体領域2を形成し、その後、化合物半導体領域2上にゲート電極4g、ソース電極4s及びドレイン電極4dを形成し、更に、化合物半導体領域2上にソース電極4sに接続されるAu膜10を形成する。次に、SiC基板1の裏面にレーザビームを照射して、SiC基板1、化合物半導体領域2及びAu層を貫通するバイアホール21を形成する。次に、バイアホール21の側面及びSiC基板1の裏面にわたってビア配線14を形成する。次に、バイアホール21内に溶融金属滴32を充填し凝固させることにより、導通ビアを形成する。そして、溶融金属滴32を充填する際に、SiC基板1を溶融金属滴32に対して相対的に振動させる。

(もっと読む)

有機半導体材料及びその製造方法、並びに有機電子デバイス

【課題】高いキャリア移動度と安定性を有し、容易なプロセスで作製可能な有機半導体材料及び有機デバイスを提供する。

【解決手段】下記一般式で表されるポルフィリン2量体を含む有機半導体材料、及び、ビシクロ構造を有する前駆体としてのポルフィリン2量体を溶媒に溶解した溶液を基板上に塗布し、加熱することにより、上記ポルフィリン2量体に変換する有機半導体材料の製造方法、並びに、半導体層と2以上の電極とを有する有機電子デバイスにおいて、該半導体層が上記有機半導体材料を含む有機電子デバイス。 (もっと読む)

(もっと読む)

促進された導電性を有する非パンチスルー半導体チャネルを備えた半導体素子及び製法

半導体素子が記載されており、当該素子における電流の流れは変換接合(例えば、p−n接合又は金属−半導体接合)の間に閉じ込められる。当該素子は、非パンチスルー挙動と、促進された導電可能性とをもたらす。当該素子は、接合型電界効果トランジスタ(JFET)、スタティック誘導トランジスタ(SIT)、接合型電界効果サイリスタ、又はJFET電流リミッタであり得る。当該素子は、炭化ケイ素(SiC)などの広いバンドギャップ半導体により製造され得る。いくつかの実施形態によれば、当該素子は、通常OFFのSiC垂直接合型電界効果トランジスタであり得る。当該素子の製法、及び当該素子を備えた回路も記載されている。 (もっと読む)

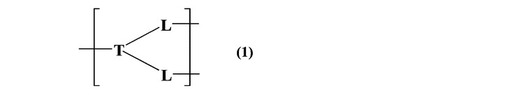

分岐型化合物、これを用いた有機薄膜及び有機薄膜素子

【課題】電荷輸送性に優れる両極性の有機半導体として利用可能な分岐型化合物の提供。

【解決手段】コア部と、該コア部に結合した少なくとも1つの側鎖部と、末端と、から構成される分岐型化合物であって、上記側鎖部の少なくとも1つは、下記一般式(1)で表される繰返し単位が1又は2以上繰り返しており(但し、コア部と結合する前記繰返し単位においては、Tがコア部に結合しており、2以上繰り返す前記繰返し単位においては、LがTに結合している。)、Lは、共役形成単位が複数連結して構成され、上記共役形成単位として少なくとも一つのチエニレン単位を含み、Lの末端(Tと結合していない側のLの末端)に存在する基は、少なくとも2つがアクセプター性の基である、分岐型化合物。

(式中、Lは置換基を有していてもよい2価の有機基を示し、Tは置換基を有していてもよい3価の有機基を示す。)

(もっと読む)

電界効果トランジスタ

【課題】 電界効果トランジスタにおいて、フィールドプレート終端での高電界の集中を緩和し、もって高耐圧半導体装置として利用可能とすること。

【解決手段】 本電界効果トランジスタ30は、GaN系エピタキシャル基板32の電子走行層上に、ゲート電極38を挟んで所定の間隔を隔てて配されたソース電極34及びドレイン電極36を備え、ゲート電極38の上部に、ドレイン電極36側に庇状に突き出したフィールドプレート40が形成され、ソース電極34及びドレイン電極36がオーミック接触するエピタキシャル基板32の電子走行層とフィールドプレート40との間に、誘電体膜46が形成され、誘電体膜46は、フィールドプレート40の直下領域においてフィールドプレート終端面と面一状態で切れ込み50が形成されその下端からドレイン電極36にオーバーラップするようにドレイン電極36に向かって延びる。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】オン抵抗が低減された窒化物半導体素子およびその製造方法を提供すること。

【解決手段】この窒化物半導体素子は、n型層3、p型層4およびn型層5を有する窒化物半導体積層構造部2を備えている。窒化物半導体積層構造部2には、トレンチ6が形成されている。トレンチ6の壁面7の全域を覆うように、n型チャネル層8が形成されている。トレンチ6において、n型チャネル層8の内側には、p型不純物を含むGaNからなるp型ゲート層9が埋設されており、p型ゲート層9の最表面15には、ゲート電極10が形成されている。また、n型層5の最表面16には、ソース電極11が形成され、基板1の他方面には、ドレイン電極12が接触形成されている。

(もっと読む)

スイッチング素子並びにそれを用いたアンテナスイッチ回路及び高周波モジュール

【課題】挿入損失を増大させることなくマルチゲートのゲート間の電位安定化が可能なスイッチング素子並びにそれを用いたアンテナスイッチ回路及び高周波モジュールを提供すること。

【解決手段】電界効果型トランジスタを成すように、半導体基板上に形成された2個のオーミック電極39,40と、上記2個のオーミック電極の間に配置された少なくとも2個のゲート電極41,42と、隣り合うゲート電極の間に挟まれて配置された導電領域45とが備えられる。導電領域は、一端に、上記隣り合うゲート電極に挟まれている導電領域よりも幅が広い幅広部分を有し、隣り合うゲート電極の間の距離が幅広部分の幅よりも狭い。更に、幅広部分を介して2個のオーミック電極の間に直列に抵抗44,46が接続されている。

(もっと読む)

101 - 120 / 176

[ Back to top ]