Fターム[5F102GR11]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 非対称構造 (606)

Fターム[5F102GR11]の下位に属するFターム

S−G電極間とD−G電極間の距離が異なるもの (319)

ソースとドレインの形状、不純物濃度が異なるもの (111)

Fターム[5F102GR11]に分類される特許

81 - 100 / 176

半導体装置および半導体装置の製造方法

【課題】小型かつ高性能な半導体装置を提供すること。

【解決手段】SiC基板11上に形成された第1のGaN層12と、第1のGaN層12上に形成されたソースパッド23と、第1のGaN層12上に形成された複数の円柱状のGaN層14と、これらの円柱状のGaN層14の上端に接するように形成された第2のGaN層16と、第2のGaN層16上に形成されたドレインパッド25と、を具備する半導体装置であって、複数の円柱状のGaN層14は、それぞれ下から順にソース領域18、ゲート領域19、ソース領域よりも径が細いドレイン領域17からなり、ソース領域18の周囲には第1の絶縁膜20、ゲート領域19の周囲にはゲート電極21、ドレイン領域17の周囲には所定の空間を介して第2の絶縁膜22がそれぞれ形成される。

(もっと読む)

縦型パワートランジスタ装置、半導体チップ、および縦型パワートランジスタ装置の製造方法

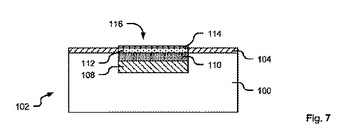

縦型トランジスタ装置は、III−V族半導体材料から形成される基板(100)と、少なくとも部分的に基板内に収容される多層スタック(116)とを備える。多層スタックは、基板(100)に隣接して配置される半絶縁層(108)と、第1のIII−V族半導体材料から形成されており、半絶縁層に隣接して配置される第1の層(110)とを備える。多層スタック(116)はまた、第2のIII−V族半導体材料から形成されて、第1の層(110)に隣接する第2の層(112)と、第1の層と第2の層との界面に形成されるヘテロ接合部とを備える。  (もっと読む)

(もっと読む)

半導体装置

【課題】ソースフィールドプレート電極を形成することによる性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】SiC基板11上にGaN層12およびAlGaN層13がこの順で形成され、AlGaN層13上にドレイン電極14、ソース電極15およびゲート電極16が形成された半導体装置であって、ゲート電極16の下方には、SiC基板11を貫通するように第1の開口23が形成されている。さらに、GaN層12上に形成され、ソース電極15に接続されるソースパッド19の一部が、SiC基板11の裏面側から露出するように、第2の開口24が形成されている。そして、第1の開口23内にソースフィールドプレート電極25−1を形成すると同時に、第2の開口24から露出するソースパッド19に接触するようにSiC基板11の裏面に接地導体25−2を形成する。

(もっと読む)

有機トランジスタ、回路素子及びそれらの製造方法

【課題】低電圧で作動するとともに大きなベース電圧を印加した場合でも耐電圧が高く、各種の回路素子への応用が容易で、製造コストを抑えた有機トランジスタ及び回路素子を提供する。

【解決手段】コレクタ電極1とエミッタ電極2と両電極間に設けられた有機半導体層3と有機半導体層3内に設けられたベース電極4とを有する縦型トランジスタ部、及び、ベース電極4とベース電圧電源端子7との間に設けられた抵抗部6、を有する。抵抗部6は、コレクタ電極1と同じ材料からなりベース電圧電源端子7に接続する第1電極21と、エミッタ電極2と同じ材料からなりベース電極4に接続する第2電極22と、有機半導体層3と同じ材料からなり第1電極21及び第2電極22間に挟まれた抵抗層24とを有する。

(もっと読む)

GaN系ヘテロ構造電界効果トランジスタ

【課題】GaN系ヘテロ構造電界効果トランジスタにおいて、ゲート電極直下のチャネルのソース端に局所的に高電界領域を形成することで同領域における電子の走行時間を短縮し、同トランジスタの優れた高速動作を実現する。

【解決手段】(0001)サファイア基板1上に設けられるGaNバッファ層2及びAlGaNショットキ層3と、AlGaNショットキ層3上に設けられるソース電極6、ドレイン電極7、及びゲート電極8とを備えるGaN系ヘテロ構造電界効果トランジスタにおいて、ソース電極6とゲート電極8との間に、窒化シリコンからなり圧縮性の内部応力を有する第一の絶縁膜9を設けた。

(もっと読む)

半導体装置

【課題】本発明は、絶縁領域において破壊が起こるのを防止できる半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、半導体基板と、前記半導体基板の上面側に設けられた不純物添加領域と、前記半導体基板の上面側において、イオン注入によって前記不純物添加領域の周囲に設けられた絶縁領域と、前記不純物添加領域上に設けられたゲート電極と、前記ゲート電極を挟むように前記不純物添加領域上に設けられた第1の電極及び第2の電極と、前記絶縁領域上に設けられ、前記ゲート電極に接続した第1のパッドと、前記絶縁領域上において前記不純物添加領域を挟んで前記第1のパッドと対向するように設けられ、前記第2の電極に接続した第2のパッドと、前記絶縁領域上において、前記第1の電極と前記第2のパッドの間に設けられた導体と、を備えることを特徴とするものである。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのSBD10は、半導体からなる基板11と、基板11上に形成されたn型層12と、n型層12上に配置されたアノード電極14と、アノード電極14に接続され、n型層12に突出するp型領域13とを備えている。p型領域13は、n型層12との境界領域において、境界領域に隣接するp型領域13内の領域である高不純物領域13Bよりも導電型がp型であるp型不純物の濃度の低い低不純物領域13Aを含んでいる。

(もっと読む)

半導体装置

【課題】インパクトイオン化現象によって発生した電子・正孔を効率よく吸収することが可能で正常な動作特性と高い信頼性を実現する半導体装置を提供する。

【解決手段】半導体装置20は、基板21に対して順次積層されたバッファ層22、下地化合物半導体層23f(下地化合物半導体層23)、インパクトイオン制御層24、下地化合物半導体層23s(下地化合物半導体層23)、チャネル画定化合物半導体層26f(チャネル画定化合物半導体層26)、チャネル画定化合物半導体層26s(チャネル画定化合物半導体層26)、AlGaN(窒化アルミニウムガリウム)層28、GaN(窒化ガリウム)層29を備えている。インパクトイオン制御層24は、下地化合物半導体層23の積層範囲(積層範囲の厚さTst)内に積層されてインパクトイオン化現象の発生位置を制御する。

(もっと読む)

電界効果トランジスタ

【課題】広い温度範囲で高効率に動作可能な電界効果トランジスタを提供することである。

【解決手段】本発明にかかる電界効果トランジスタは、抵抗率が0.02Ω・cm以下のシリコン基板1と、シリコン基板1上に形成された5μm以上の膜厚を有するチャネル層2と、チャネル層2上に形成されると共に、チャネル層2に電子を供給するバリア層4と、チャネル層2とバリア層4とのヘテロ接合により形成された2次元電子ガス層3と、バリア層4とオーミック接触するソース電極5及びドレイン電極6と、ソース電極5とドレイン電極6との間に形成され、バリア層4とショットキー接合するゲート電極7と、を有する。

(もっと読む)

横型HEMTおよび横型HEMTの製造方法

【課題】高いアバランシュブレークダイン強度を有する横型HEMTと、その製造方法を提供する。

【解決手段】基板10と、基板上に配置された、第1導電型のチヤネルとなる第1層11、少なくとも部分的に上記第1層11の上に配置された電子供給層となる第2層12を有する。さらに、上記横型HEMTは、上記第1導電型に対して相補的な第2導電型の半導体物質を有し、少なくとも部分的に上記第1層11の中に配置された第3層13を有する。このためPNダイオードが上記第1層および第3層の間で形成され、PNダイオードは横型HEMTより低いブレークダウン電圧を有することにより、HEMTを高い電界から保護することができ、HEMTの劣化を防止できる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながら、高いドレイン電流を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上方に形成されたソース電極5s、ドレイン電極5d及びゲート電極5gと、が設けられている。更に、ソース電極5sとゲート電極5gとの間の化合物半導体積層構造2上に形成され、シリコンを含む第1の保護膜6と、ドレイン電極5dとゲート電極5gと間の化合物半導体積層構造2上に形成され、第1の保護膜6より多くシリコンを含む第2の保護膜7と、が設けられている。

(もっと読む)

電界効果トランジスタ

【課題】耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】p型の導電型を有する基板と、前記基板上に形成された高抵抗層と、前記高抵抗層上に形成され、p型の導電型を有するp型半導体層を前記基板側に配置したリサーフ構造を有する半導体動作層と、前記半導体動作層上に形成されたソース電極、ドレイン電極、およびゲート電極と、を備える。好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたn型の導電型を有するリサーフ層を備える。また、好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたアンドープのキャリア走行層と、前記キャリア走行層上に形成され該キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層とを備える。

(もっと読む)

半導体装置、電力変換装置及び半導体装置の製造方法

【課題】RCスナバ回路の抵抗Rの値を任意に設計可能な半導体スナバ回路を用いた半導体装置、電力変換装置、半導体装置の製造方法を提供する。

【解決手段】ユニポーラ動作をする還流ダイオード100と、還流ダイオード100に並列接続され、キャパシタ210及び抵抗220をモノリシックに集積化した半導体スナバ回路200とを備える半導体装置において、抵抗220が、半導体スナバ回路200の基材となる半導体基体の一部に形成され、半導体基体の比抵抗よりも高い比抵抗を有する高抵抗層を含む。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮可能な半導体装置を提供する。

【解決手段】半導体装置10は、ユニポーラ型の還流ダイオード100と、還流ダイオード100に接続されたユニポーラ型の還流ダイオード150と、還流ダイオード100に並列接続され、少なくともキャパシタ210と抵抗220とを有する半導体スナバ200、及び、還流ダイオード150に並列接続され、少なくともキャパシタ260と抵抗270とを有する半導体スナバ250が形成された基板領域11を有する半導体チップ1000とを備えている。

(もっと読む)

半導体装置

【課題】窒化物半導体から成るヘテロ接合電界効果型トランジスタに於いて、バリア層上に2次元電子ガス濃度を減少させずに略50nm以上のキャップ層を形成するには、シリコンを1×1019cm-2程度の高濃度でドーピングする必要があるが、この様な高い濃度のシリコンを均一性良くドーピングするのは困難である。窒化物半導体では酸素及び窒素空孔の様なエピタキシャル成長中等に意図せずに混入するドナーがあるため、シリコンだけでドーピング濃度を制御することが難しい。

【解決手段】キャップ層50内でヘテロ接合の形成により発生する分極の影響を受けるバリア層40側の領域に、キャップ層50を構成する窒化物半導体のバンドギャップ内の分極の効果によって決まるフェルミ・レベルよりも高いエネルギー位置に準位を形成する複数のドナーが、合計して2次元電子ガス濃度と同程度の濃度でドーピングされている。

(もっと読む)

半導体装置

【課題】ゲート・ドレイン間の帰還容量増大を防止し、超高周波動作に適する半導体装置。

【解決手段】

基板10上に順次配置され,窒化物系化合物半導体層からなるバッファ層12およびアルミニウム窒化ガリウム層(AlxGa1-xN)(0.1≦x≦1)からなるショットキー層14と、ショットキー層14上に配置されたソース電極16およびドレイン電極18と、ショットキー層14に形成され,ソース電極16およびドレイン電極18間のチャネルを細線状に分割する複数の溝26と、複数の溝26および細線状に分割されたチャネルを横断して配置されたゲート電極20と、ショットキー層14,複数の溝26およびゲート電極20上に形成された絶縁層22と、絶縁層22上に配置され,ソース電極16に接続されたソースフィールドプレート電極24とを備える。

(もっと読む)

III族窒化物デバイスおよび回路

ゲート接続接地電界プレートを有するIII族窒化物ベースの高電子移動度トランジスタを説明する。ゲート接続接地電界プレートデバイスは、ミラー容量効果を最小化することができる。トランジスタは、高電圧空乏モードトランジスタとして形成し、低電圧エンハンスメントモードトランジスタと組み合わせて、単一の高電圧エンハンスメントモードトランジスタとして動作する部品を形成するために用いることができる。 (もっと読む)

化合物半導体装置及びその製造方法

【課題】オフ時のリーク電流を低減することができ、好ましくは高い閾値電圧を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】i−GaN層5(電子走行層)と、i−GaN層5(電子走行層)上方に形成されたn−GaN層7(化合物半導体層)と、n−GaN層7(化合物半導体層)上方に形成されたソース電極21s、ドレイン電極21d及びゲート電極21gと、が設けられている。そして、n−GaN層7(化合物半導体層)のソース電極21sとドレイン電極21dとの間の領域内でゲート電極21gから離間した部分にリセス部7a(凹部)が形成されている。

(もっと読む)

高電力マイクロ電子デバイスのための金属化構造

【課題】高電力で高性能なデバイスによって生成される熱応力に耐えることができる金属相互接続システムを提供する。

【解決手段】半導体デバイス構造であって、炭化ケイ素およびIII族窒化物からなる群から選択される広バンドギャップの半導体部分と、該半導体部分に対する相互接続構造であって、それぞれ2つの高導電性層と互い違いに、少なくとも2つの拡散バリア層を含む、相互接続構造とを備え、該拡散バリア層は、該高導電性層とは異なる熱膨張係数を有し、該高導電性層よりも低い熱膨張係数を有し、該それぞれの熱膨張係数の差異は、該高導電性層の膨張を抑えるために十分な大きさであるが、層間の接着強度を超える歪みを隣接層間に生じさせる差異よりも小さい、半導体デバイス構造。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧に優れ、強度の高いIII−V族窒化物半導体からなる半導体装置を実現する。

【解決手段】本発明の構造では、第1のソース電極106がバイアホール112を介して導電性基板101に接続されており、また、第2のソース電極110が形成されている。これにより、ゲート電極108とドレイン電極107との間に高い逆方向電圧が印加されても、ゲート電極108のうちドレイン電極107に近い側の端部に起こりやすい電界集中を効果的に分散または緩和することができるため、耐圧が向上する。また、素子形成層を形成する基板として導電性基板101を用いているため、導電性基板101には裏面まで貫通するバイアホールを設ける必要がない。したがって、導電性基板101に必要な強度を保持したまま、第1のソース電極106と裏面電極115とを電気的に接続することができる。

(もっと読む)

81 - 100 / 176

[ Back to top ]