Fターム[5F102GS01]の内容

接合型電界効果トランジスタ (42,929) | ゲート電極構造 (2,097) | 多層構造 (903)

Fターム[5F102GS01]の下位に属するFターム

3層以上 (156)

Fターム[5F102GS01]に分類される特許

81 - 100 / 747

窒化物半導体装置

【課題】リーク電流を低減でき、かつ、良好な電流コラプス特性が得られる窒化物半導体装置を提供する。

【解決手段】Si基板1上に順に積層されたチャネルGaN層5およびそのチャネルGaN層5とヘテロ界面を形成するバリアAlGaN層6を含む窒化物半導体層を備える。上記バリアAlGaN層6は、炭素濃度を5×1017/cm3以上とする。また、チャネルGaN層5は、炭素濃度を6×1016/cm3未満とし、かつ、膜厚を500nm以上とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】絶縁破壊耐性に優れた化合物半導体積層構造を備えて基板の絶縁破壊の十分な抑止を実現し、ピンチオフ状態とする際にもリーク電流が極めて少ない信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上に形成された化合物半導体積層構造2は、その厚みが10μm以下であって、AlNからなる厚い第1のバッファ層を有しており、III族元素(Ga,Al)の総原子数のうち、Al原子の比率が50%以上とされ、換言すれば、V族元素のNとの化学結合(Ga−N,Al−N)の総数のうち、Al−Nが50%以上とされる。

(もっと読む)

半導体装置の製造方法

【課題】設計された形状およびサイズのゲート電極を形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】本実施形態に係る半導体装置の製造方法は、半導体層12の表面上のうち、互いに離間した位置に、チタン層17a、18a、アルミニウム層17b、18b、ニッケル層17c、18c、金層17d、18dがこの順で積層した積層体17、18を形成し、これらを、アルミニウムの融点より高い温度で加熱して複数の金属体17´、18´を形成するするとともに、これらの複数の金属体17´、18´を半導体層12にオーミック接触させる。この後、複数の金属体17´、18´を薄膜化して複数の合金層13a、14aを形成し、合金層13a、14aを含むドレイン電極13およびソース電極14を形成する。次に、ドレイン電極13とソース電極14との間のレジスト層19に開口部20し、この開口部20内にゲート電極15を形成する。

(もっと読む)

半導体装置の製造方法

【課題】設計の自由度を損なわずに、高いオン特性とオフ特性を持つ半導体装置を容易に製造する。

【解決手段】可視光に対して透明な半導体基板1の表面にソース電極2及びドレイン電極3を形成する。半導体基板1の表面においてソース電極2とドレイン電極3との間に表側ゲート電極4を形成する。半導体基板1の表面においてソース電極2とドレイン電極3との間以外の領域に合わせマーク5を形成する。半導体基板1を透過して見える合わせマーク5に基づいて半導体基板1を位置合わせして、半導体基板1の裏面において表側ゲート電極4と対向する位置に裏側ゲート電極6を形成する。

(もっと読む)

窒化物半導体層のエッチング方法及びこれを用いた窒化物半導体装置の製造方法

【課題】高抵抗なダメージ層を形成しない窒化物半導体層のエッチング方法と、これを用いた低抵抗なオーミック電極を備える窒化物半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の窒化物半導体層のエッチング方法は、(a)窒化物半導体層に不純物イオンを注入し、その表面から所定深さまで不純物領域を形成する工程と、(b)前記不純物領域を熱処理する工程と、(c)前記不純物領域の前記表面側の所定領域をウェットエッチングで除去する工程とを備える。

(もっと読む)

パワーデバイス

【課題】膜剥がれの要因となる有機材料を用いることなく、エレクトロマイグレーションの耐性と長期信頼性を向上できるパワーデバイスを提供する。

【解決手段】バリア層4(AlGaN)4上に形成された酸化シリコン(SiO2)からなる層間絶縁膜10と、層間絶縁膜10のソース電極5上に形成され、基板平面に対して略垂直な第1の側壁W1を有する第1コンタクトホール部10aと、第1コンタクトホール部10aの第1の側壁W1の上縁から上側に向かって徐々に広がるように層間絶縁膜10に形成され、基板平面に対して傾斜した第2の側壁W2を有する第2コンタクトホール部10bと、第1,第2コンタクトホール部10a,10b内および層間絶縁膜10上に形成された配線層12とを備える。上記配線層12は、第1コンタクトホール部10aにおいて第1の側壁W1の基板厚さ方向の寸法よりも膜厚が厚い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

半導体装置

【課題】電流の減少を抑制することが可能な半導体装置を提供すること。

【解決手段】本発明は、炭化シリコンからなる基板10と、基板10上に設けられた窒化アルミニウムからなるバッファ層12と、バッファ層12上に設けられた窒化ガリウムからなるチャネル層14と、チャネル層14上に設けられた窒化物半導体からなる電子供給層16と、電子供給層16上に設けられたソース電極20、ドレイン電極22及びゲート電極24と、を具備し、バッファ層12の厚さの逆数の平均値の逆数は20nm以下であり、バッファ層12の最も厚い部分と、最も薄い部分との厚さの差は6nm以上であることHEMT100である。

(もっと読む)

半導体装置の製造方法

【課題】InAlN電子供給層上にGaN層を形成する場合でも、InAlN電子供給層の品質の悪化を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、基板10上にGaN電子走行層14を形成する工程と、GaN電子走行層14上にInAlN電子供給層18を形成する工程と、InAlN電子供給層18を形成した後、In含有ガスを供給しつつ、基板10を昇温させる工程と、昇温が終了した後、InAlN電子供給層18上にGaN層20を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

印刷可能半導体素子を製造して組み立てるための方法及びデバイス

【課題】印刷可能半導体素子を製造するとともに、印刷可能半導体素子を基板表面上に組み立てるための方法及びデバイスを提供する。

【解決手段】デバイス、デバイス部品は、幅広いフレキシブル電子デバイス及び光電子デバイス並びにデバイスの配列を高分子材料を備える基板上に形成する。伸張形態で良好な性能が得られる伸縮可能な半導体構造及び伸縮可能な電子デバイスを形成する。

(もっと読む)

半導体装置

【課題】高周波数動作が可能な半導体装置を提供すること。

【解決手段】本発明は、基板10上に設けられたGaN電子走行層14と、GaN電子走行層14上に設けられたAlNスペーサ層16と、AlNスペーサ層16上に設けられたInAlN電子供給層18と、InAlN電子供給層18上に設けられたゲート電極24とゲート電極24を挟むソース電極26およびドレイン電極28と、を備え、AlNスペーサ層16の膜厚が、0.5nm以上1.25nm以下の半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】InAlN電子供給層上にGaN層を形成する場合でも、InAlN電子供給層の品質の悪化を抑制すること。

【解決手段】本発明は、基板10上にGaN電子走行層14を形成する工程と、GaN電子走行層14上にInAlN電子供給層18を形成する工程と、InAlN電子供給層18上に第1のGaN層20を形成する工程と、第1のGaN層20上に、InAlN電子供給層18および第1のGaN層20を形成した際の温度よりも高い温度で、第2のGaN層22を形成する工程と、InAlN電子供給層18上に、ゲート電極26と、ゲート電極26を挟むソース電極28およびドレイン電極30と、を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

化合物半導体装置

【課題】 電流コラプスを抑制するとともに、高耐圧動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】 SiC基板10上に形成されたi−GaNバッファ層12と、i−GaNバッファ層12上に形成されたn−AlGaN電子供給層16と、n−AlGaN電子供給層16上に形成されたn−GaNキャップ層18と、n−GaNキャップ層18上に形成されたソース電極20及ドレイン電極22と、ソース電極20とドレイン電極22との間のn−GaNキャップ層18上に形成されたゲート電極26と、ソース電極20とドレイン電極22との間のn−GaNキャップ層18上に形成された第1の保護層24と、ゲート電極26とドレイン電極22との間の第1の保護層24に形成されたn−GaNキャップ層18に達する開口部28に埋め込まれ、第1の保護層24とは異なる絶縁層よりなる第2の保護層30とを有する。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】ウルツ鉱型結晶構造の半導体を用いた電界効果トランジスタで、電極との接触抵抗を高くすることなく、バンドギャップエネルギーのより大きな半導体から障壁層が構成できるようにする。

【解決手段】ゲート電極104を挟んで各々離間して障壁層103の上に接して形成された2つの電流トンネル層105と、各々の電流トンネル層105の上に形成された2つのキャップ層106とを備える。電流トンネル層105の分極電荷は、障壁層103の分極電荷よりも大きい。

(もっと読む)

半導体装置

【課題】ソース・ドレイン間容量の低下と、電流コラプスの抑制とを両立することが可能な半導体装置を提供すること。

【解決手段】基板10と、基板10上に形成された窒化物半導体層11と、窒化物半導体層11上に設けられたソース電極24、ゲート電極28、及びドレイン電極26と、ゲート電極28、及びゲート電極28とドレイン電極26との間の窒化物半導体層11の表面を覆う絶縁膜20と、窒化物半導体層11上であって、ゲート電極28とドレイン電極26との間に設けられたフィールドプレート30と、を具備し、ゲート電極28とドレイン電極26との間の領域の絶縁膜20上におけるフィールドプレート30の幅Wは0.1μm以上であり、フィールドプレート30のドレイン電極26側の端部と、ドレイン電極26のゲート電極28側の端部との距離L1は、3.5μm以上であり、動作周波数が4GHz以下である半導体装置である。

(もっと読む)

半導体装置

【課題】冷却効率を向上させることができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、裏面に複数の凹部16を有するシリコン基板11と、この基板11の表面上に形成された半導体層12と、半導体層12の表面上に、互いに離間して形成されたドレイン電極13およびソース電極14と、ドレイン電極13とソース電極14との間の半導体層12上に形成されたゲート電極15と、複数の凹部16の内部を含むシリコン基板11の裏面全体に形成された裏面金属17と、を具備する。

(もっと読む)

半導体エピタキシャル基板、およびその製造方法

【課題】

高周波信号遮断後の回復が早く、素子分離特性のよい化合物半導体エピタキシャル基板を提供する。

【解決手段】

半導体エピタキシャル基板は、単結晶基板と、単結晶基板上にエピタキシャル成長されたAlN層と、AlN層の上にエピタキシャル成長された窒化物半導体層とを有し、単結晶基板とAlN層間界面より、AlN層と窒化物半導体層間界面の方が凹凸が大きい、ことを特徴とする。

(もっと読む)

窒化物半導体装置および窒化物半導体装置の製造方法

【課題】オン抵抗が低く、かつ、Vth(閾値電圧)が高い窒化物半導体装置の提供。

【解決手段】アクセプタになるアクセプタ元素を含み、窒化物半導体で形成されたバックバリア層106と、バックバリア層106上に窒化物半導体で形成されたチャネル層108と、チャネル層108の上方に、チャネル層よりバンドギャップが大きい窒化物半導体で形成された電子供給層112と、チャネル層108と電気的に接続された第1主電極116、118と、チャネル層108の上方に形成された制御電極120と、を備え、バックバリア層106は、制御電極120の下側の領域の少なくとも一部に、アクセプタの濃度がバックバリア層の他の一部の領域より高い高アクセプタ領域126を有する窒化物半導体装置100。

(もっと読む)

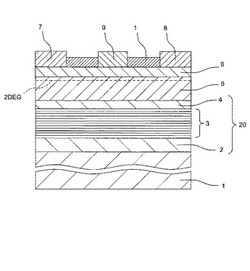

半導体素子及びその製造方法

【課題】転位密度を低減させるバッファ層を有する半導体素子を提供する。

【解決手段】基板と、基板の上方に形成されたバッファ領域と、バッファ領域上に形成された活性層と、活性層上に形成された少なくとも2つの電極とを備え、バッファ領域は、第1の格子定数を有する第1半導体層と、第1の格子定数と異なる第2の格子定数を有する第2半導体層と、第1の格子定数と第2の格子定数との間の第3の格子定数を有する第3半導体層とが順に積層した複合層を少なくとも一層有する半導体素子。

(もっと読む)

半導体素子及びその製造方法

【課題】リーク電流が低減された窒化物系半導体素子及びその製造方法を提供する。

【解決手段】基板10と、基板10の上方に形成されたバッファ領域30と、バッファ領域30上に形成された活性層70と、活性層上に形成された少なくとも2つの電極72、74、76とを備え、バッファ領域30は、格子定数の異なる複数の半導体層31、32、33を含み、バッファ領域30の表面に、基板10の裏面より低い電位を与え、基板10の裏面とバッファ領域30の表面との間の電圧をバッファ領域30の膜厚に応じた範囲で変化させたときの基板10の裏面およびバッファ領域30の表面との間の静電容量が略一定である半導体素子100を提供する。

(もっと読む)

81 - 100 / 747

[ Back to top ]