Fターム[5F102GS02]の内容

接合型電界効果トランジスタ (42,929) | ゲート電極構造 (2,097) | 多層構造 (903) | 3層以上 (156)

Fターム[5F102GS02]に分類される特許

1 - 20 / 156

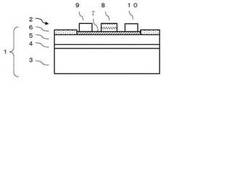

グラフェン構造の製造方法及びこれを用いた半導体装置の製造方法

【課題】所望の位置にグラフェン膜を有するグラフェン構造及びこれを用いた半導体装置を提供する。

【解決手段】所定の基材3上において、炭素含有層4と、少なくともケイ素を含む炭素化合物層5とを順次に積層し、その上に絶縁膜層6を形成した後、絶縁膜層の一部をエッチングにより取り除いた基板に対してアニーリングを実施し、絶縁膜の除去部にのみグラフェン膜7を形成したグラフェン構造1を形成し、これを用いて表面にショットキー電極8、およびオーミック電極9,10を形成させて半導体装置2を作製する。

(もっと読む)

半導体装置

【課題】複数のチャネルを有する窒化物半導体装置において、ノーマリオフかつ低オン抵抗を実現する技術を提供する。

【解決手段】第1の窒化物半導体層3,5,7と、第1の窒化物半導体層よりも禁制帯幅が大きい第2の窒化物半導体層5,6,8とが積層されたヘテロ接合体を少なくとも2つ以上有する窒化物半導体積層体10を備え、窒化物半導体積層体10に設けられたドレイン電極14と、ソース電極13と、ドレイン電極14とソース電極13の両者に対向して設けられたゲート電極15,16とを有し、ドレイン電極14とソース電極13は、窒化物半導体積層体10の表面または側面に配置され、ゲート電極15,16は、窒化物半導体積層体10の深さ方向に設けられた第1ゲート電極15と、該第1ゲート電極15と窒化物半導体積層体10の深さ方向の配置深さが異なる第2ゲート電極16とを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、半導体層12、絶縁膜17、ゲート電極22、ドレイン電極19およびソース電極20、を具備する。半導体層12は、半絶縁性半導体基板11上に形成され、表面に、側壁が傾いたテーパ状のリセス領域18を有する。半導体層12は、活性層14を含む。絶縁膜17は、半導体層12上に形成されたものであり、リセス領域18を全て露出する貫通孔21を有する。貫通孔21は、側壁がリセス領域18の側壁の傾き角θ1より小さい角度θ2で傾いたテーパ状である。ゲート電極22は、リセス領域18および貫通孔21を埋めるように形成されたものである。ドレイン電極19およびソース電極20は、半導体層12上のうち、リセス領域18を挟む位置に形成されたものである。

(もっと読む)

半導体装置

【課題】低コンタクト抵抗を実現し得る半導体基板上の半導体層と電極配線層とのオーミック電極構造を提供する。

【解決手段】半導体基板106と、半導体基板106上に形成された第1のバリア層107と、第1のバリア層107上に形成された厚さ1nm以上40nm以下のチャネル層108と、チャネル層108の上に形成された第2のバリア層102と、少なくとも第2のバリア層102及びチャネル層108を厚さ方向に貫通する第1の電極領域109と、少なくとも第2のバリア層102及びチャネル層108を厚さ方向に貫通する第2の電極領域109とを備える半導体装置であって、少なくとも第1の電極領域109は、チャネル層108と接触する側の面が凹凸形状で構成されている。

(もっと読む)

半導体素子および半導体素子の製造方法

【課題】バッファ層を有する半導体素子において、チャネルの基準電位を固定する半導体素子及びその製造方法を提供する。

【解決手段】基板10と、基板上に設けられ、エネルギーギャップの異なる複数種類の窒化物半導体が積層された積層体を少なくとも1層有するバッファ層20と、バッファ層上に設けられた窒化物半導体のチャネル層30と、バッファ層の側面に電気的に接続された側面電極60と、チャネル層の上方に形成され、チャネル層と電気的に接続されたチャネル電極52,56とを備える半導体素子。

(もっと読む)

GaN系化合物半導体装置

【課題】ゲート電極へのリーク電流を大幅に低減できるGaN系化合物半導体装置を提供する。

【解決手段】このGaN系HFETによれば、ゲート電極をなすTiN膜の抵抗率(Ω・μm)を24.7(Ω・μm)とした。このように、ゲート電極のショットキー電極層としてのTiN膜の抵抗率が10Ωμm以上であることによって、ゲート電極をなす金属材料TiNの抵抗率(ゲートメタル抵抗率)が10Ωμm未満である場合に比べて、ゲートリーク電流を著しく低減できる。

(もっと読む)

テラヘルツ波素子

【課題】テラヘルツ波を発生又は検出するテラヘルツ波素子において、単色性が良いテラヘルツ波を効率良く出射する。

【解決手段】テラヘルツ波素子は、基板101の上に形成された第1の半導体層102と、第1の半導体層102の上に形成された第2の半導体層104と、第2の半導体層104の上に形成されたゲート電極106と、第2の半導体層104の上にゲート電極106を挟んで対向するように形成されたソース電極107及びドレイン電極108と、第2の半導体層104の上におけるゲート電極106とソース電極107との間及びゲート電極106とドレイン電極108との間に形成され、複数の金属膜109が周期的に配置された周期構造を有する周期金属膜109A,109Bと、ゲート電極106及び複数の金属膜109の上方に配置された第1のミラー111と、基板101の下に形成された第2のミラー112とを備えている。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

半導体装置

【課題】高電圧を印加しても短絡破壊を生じないトランジスタとして動作する半導体装置を提供する。

【解決手段】半導体装置1は、基板10(シリコン基板10a)の上に形成されたバッファ層21と、バッファ層21の上に形成されたチャネル層22と、チャネル層22の上に形成され、チャネル層22とヘテロ接合を構成する障壁層23とを備える。バッファ層21およびチャネル層22は、窒化物半導体で形成されている。チャネル層22は、膜厚を1μm以上2μm以下とされ、炭素濃度を5×1016cm-3以下とされている。

(もっと読む)

高電力マイクロ電子デバイスのための金属化構造

【課題】高電力で高性能なデバイスによって生成される熱応力に耐えることができる金属相互接続システムを提供する。

【解決手段】半導体デバイス構造であって、炭化ケイ素およびIII族窒化物からなる群から選択される広バンドギャップの半導体部分と、該半導体部分に対する相互接続構造であって、それぞれ2つの高導電性層と互い違いに、少なくとも2つの拡散バリア層を含む、相互接続構造とを備え、該拡散バリア層は、該高導電性層とは異なる熱膨張係数を有し、該高導電性層よりも低い熱膨張係数を有し、該それぞれの熱膨張係数の差異は、該高導電性層の膨張を抑えるために十分な大きさであるが、層間の接着強度を超える歪みを隣接層間に生じさせる差異よりも小さい、半導体デバイス構造。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート部におけるリーク電流が低減できる反面、プロセス上の制約があるため製造が困難で、ゲートリーク電流を安定して低減させることが困難だった。

【解決手段】基板と、前記基板上に形成され且つ二次元キャリアガスを有する半導体機能層と、前記半導体機能層上において互いに離間して形成される第1及び第2の主電極と、前記半導体機能層上における前記第1及び第2の主電極間に形成される制御電極と、前記半導体機能層と前記制御電極との間に形成される金属酸化膜と、を備え、

前記金属酸化膜と前記半導体機能層との接合界面における結晶格子は不連続であることを特徴とする半導体装置。

(もっと読む)

テラヘルツ波素子

【課題】単色性が強く、高効率にテラヘルツ波を発生または検出することができるテラヘルツ波素子を提供する。

【解決手段】テラヘルツ波素子100は、バッファ層102と電子供給層104とのヘテロ接合を含む半導体多層構造101〜104と、半導体多層構造101〜104上に形成されたゲート電極105、ドレイン電極106およびソース電極107とを有し、ゲート電極105とヘテロ接合界面との間の静電容量は、ドレインとソースとの間を流れる電流の方向と直交する方向に周期的に、第1の静電容量と第1の静電容量の値と異なる第2の静電容量とを有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】GaN系の材料により形成されるHEMTの信頼性を高める。

【解決手段】基板10の上方に形成された窒化物半導体からなる半導体層21〜24と、半導体層21〜24の上方に、金を含む材料により形成された電極41と、電極41の上方に形成されたバリア膜61と、半導体層21〜24の上方に、シリコンの酸化膜、窒化膜、酸窒化物のいずれかを含む材料により形成された保護膜50と、を有する。

(もっと読む)

電界効果トランジスタ、半導体スイッチ回路、および通信機器

【課題】半導体スイッチのチップサイズを大きくすることなく、高調波特性を改善する。

【解決手段】FET1において、化合物半導体基板上に形成され、所定の間隔を隔てて互いに平行状に設けられる複数のソース電極6を有するソース配線3と、化合物半導体基板上に形成され、所定の間隔を隔てて互いに平行状に設けられて複数のソース電極6に対して並列方向に交互に配置される複数のドレイン電極7を有するドレイン配線4と、化合物半導体基板上に形成され、少なくとも前記並列方向に互いに隣り合うソース電極6とドレイン電極7との電極間に位置する部分を有するゲート配線5と、ゲート配線5が形成される領域にてゲート配線5下に形成され、複数のソース電極6と複数のドレイン電極7との各電極間に独立して設けられる複数の埋め込みゲート層8とを備えた。

(もっと読む)

半導体装置の製造方法

【課題】工程を簡素化して歩留まりを向上すると共に、安定した形状の電極を再現性よく得ることができる半導体装置の製造方法を提供する。

【解決手段】第1のレジスト膜11と、第1のレジスト膜11の開口よりも小さな開口を有する第2のレジスト膜12とを用いて、SiO2絶縁膜10を異方性ドライエッチングによってエッチングして、SiO2絶縁膜10にテーパ状の開口部101を形成する。このため、GaN層1を斜めに設置し直してSiO2絶縁膜10をエッチングする必要がなく、GaN層1を水平に設置したままSiO2絶縁膜10をエッチングすることができ、工程を簡素化できる。

(もっと読む)

炭化ケイ素金属半導体電界効果トランジスタ及び炭化ケイ素の金属半導体電界効果トランジスタを製造する方法

【課題】深いレベルのドーパントがほとんど存在しない半絶縁性のSiC基板上にMESFETを形成することにより、バックゲート効果が減少された、SiCのMESFETを提供する。

【解決手段】半絶縁性の基板上10に選択的にドープされたP型の炭化珪素の層13、及びN型のエピタキシャル層14を積層し、背面ゲート効果を減少させる。また2つの凹部を有するゲート構造体も備える。これにより、出力コンダクタンスを1/3に減少することができ、また電力のゲインを3db増加することができる。クロム42をショットキーゲート接点として利用することもでき、酸化物−窒化物−酸化物(ONO)の保護層60を利用して、MESFET内の表面効果を減少させる。また、ソース及びドレインのオーム接点をn型チャネル層上に直接形成して、これにより、n+領域を製造する必要がなくなる。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】本発明は、トランジスタ特性の再現性が高く、高速でパワーの大きい電界効果トランジスタ及びその製造方法を提供することを課題とする。

【解決手段】ダイヤモンド基板11と、前記ダイヤモンド基板11の一面11a側に離間して形成された第2の電極13及び第3の電極14と、2つの電極13、14の間に離間して形成された第1の電極15と、を有する電界効果トランジスタであって、第1の電極15とダイヤモンド基板11との間にIII族窒化物半導体層12が設けられ、ダイヤモンド基板11とIII族窒化物半導体層12との界面17の近傍領域に正孔伝導チャネル領域16が形成されている電界効果トランジスタ10を用いることによって前記課題を解決できる。

(もっと読む)

半導体基板および絶縁ゲート型電界効果トランジスタ

【課題】絶縁ゲート型(MIS型)のP−HEMT構造において、チャネル層のキャリア移動度を向上し、界面準位の影響を低減した、良好なトランジスタ性能を実現できる技術を提供する。

【解決手段】ベース基板と、第1結晶層と、絶縁層とを有し、前記ベース基板、前記第1結晶層および前記絶縁層が、前記ベース基板、前記第1結晶層、前記絶縁層の順に位置し、前記第1結晶層が、GaAsまたはAlGaAsに擬格子整合できるInxGa1−xAs(0.35≦x≦0.43)からなる半導体基板を提供する。前記第1結晶層は、電界効果トランジスタのチャネル層に適用できる層であってもよく、前記絶縁層は、前記電界効果トランジスタのゲート絶縁層に適用できる層であってもよい。前記第1結晶層の77Kにおけるフォトルミネッセンス発光のピーク波長が、1070nmより大きいものであってもよい。

(もっと読む)

半導体基板、絶縁ゲート型電界効果トランジスタおよび半導体基板の製造方法

【課題】絶縁ゲート型P−HEMT構造において、良好なトランジスタ性能を実現する。

【解決手段】ベース基板、第1結晶層、第2結晶層および絶縁層をこの順に有し、第1結晶層と第2結晶層との間、または、ベース基板と第1結晶層との間に位置する第3結晶層をさらに有し、第2結晶層が、第1結晶層を構成する結晶に格子整合または擬格子整合し、かつ第1結晶層を構成する結晶よりも禁制帯幅が大きい結晶からなり、第3結晶層が、第1結晶層を構成する結晶に格子整合または擬格子整合し、かつ第1結晶層を構成する結晶よりも禁制帯幅が大きい結晶からなり、第3結晶層は、ドナーまたはアクセプタとなる第1原子を含み、第3結晶層がドナーとなる第1原子を含む場合、第2結晶層が、アクセプタとなる第2原子を含み、第3結晶層がアクセプタとなる第1原子を含む場合、第2結晶層が、ドナーとなる第2原子を含む半導体基板。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、Al2O3−SiO2の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

1 - 20 / 156

[ Back to top ]