Fターム[5F102GS01]の内容

接合型電界効果トランジスタ (42,929) | ゲート電極構造 (2,097) | 多層構造 (903)

Fターム[5F102GS01]の下位に属するFターム

3層以上 (156)

Fターム[5F102GS01]に分類される特許

141 - 160 / 747

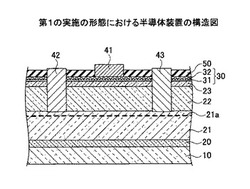

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体装置に形成される絶縁膜の付着力を高め歩留りを向上させる。

【解決手段】基板10の上方に形成された半導体層20〜23と、前記半導体層20〜23上に形成された絶縁膜31,32と、前記絶縁膜上31,32に形成された電極41と、を有し、前記絶縁膜31,32は、前記電極41の側における膜応力よりも、前記半導体層20〜23の側における膜応力が低いことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】材料の熱膨張係数の差に起因する反り等を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成された電子走行層2と、電子走行層2上方に形成された電子供給層3と、が設けられている。基板1の表面に、電子走行層2よりも熱膨張係数が小さい第1の領域1bと、電子走行層2よりも熱膨張係数が大きい第2の領域1aと、が混在する。

(もっと読む)

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体層とゲート電極との間に絶縁膜が形成された半導体装置の信頼性を高める。

【解決手段】基板の上方に形成された半導体層と、前記半導体層上に形成された絶縁膜と、前記絶縁膜上に形成された電極と、を有し、前記絶縁膜は炭素を主成分とするアモルファス膜を含むものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

化合物半導体装置及び化合物半導体装置の製造方法

【課題】トレンチを用いて素子分離され、且つ、隣接素子の動作による影響が抑制された化合物半導体装置及び化合物半導体装置の製造方法を提供する。

【解決手段】半導体基板10と、キャリア走行層21とキャリア供給層22を有し、半導体基板上に配置された窒化物半導体層20と、上端部がキャリア走行層とキャリア供給層との界面よりも上方に位置する空洞40を内部に有する、窒化物半導体層の周囲を囲んで配置された素子分離絶縁膜30とを備える。

(もっと読む)

半導体基板、半導体装置、および半導体基板の製造方法

【課題】GaN系半導体は、面方位が(111)のシリコン基板上にエピタキシャル成長される。GaNの格子定数と、とシリコン(111)面の格子定数の差が、約17%と大きいのでめ、成長されたGaNには1010cm−2を超える転位が導入される。転位により、GaNを用いたトランジスタのリーク電流が増大する。また、トランジスタの移動度が低下する。

【解決手段】シリコン基板と、シリコン基板の(150)面上に、エピタキシャル成長された窒化物半導体層と、を備える半導体基板を提供する。

(もっと読む)

III族窒化物半導体電子デバイス、エピタキシャル基板、及びIII族窒化物半導体電子デバイスを作製する方法

【課題】半導体積層内の電流経路からゲート電極を隔てる半導体層を厚くできるIII族窒化物半導体電子デバイスを提供する。

【解決手段】第2の半導体層15は第1の半導体層13上に設けられる。ゲート電極17は第2の半導体層15の上に設けられる。第1の半導体層13は、AlXGa1−XN(0<X≦1)からなる半導体表面21aの上に設けられる。第2のIII族窒化物半導体材料のバンドギャップE15は第1のIII族窒化物半導体材料のバンドギャップE13より大きい。第1の半導体層13の第1のIII族窒化物半導体材料はAlXGa1−XNと異なり、第1の半導体層13は歪みを内包する。また、第2の半導体層15の厚さT15は、無歪みの第1のIII族窒化物半導体材料の組成と、第2のIII族窒化物半導体の組成により規定される臨界膜厚より大きい。また、第1の半導体層13は、歪みを内包すると共に、半導体表面21aのAlXGa1−XNの上において格子緩和している。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

ノーマリオフ型パワーJFETの製造方法

【課題】SiC系JFETにおいて、トレンチゲート領域間を高精度に制御するため、ソース領域内にゲート領域を形成する必要がある。これにより増加するソース領域、ゲート領域間高濃度PN接合による接合電流を削減できる半導体装置を提供する。

【解決手段】ノーマリオフ型パワーJFETの製造方法であって、N型SiC1sの表面に、Nエピタキシャル下層1ea、中層1eb、上層1ec等複数層を形成し、表面には複数のソース層9、及びPゲート領域4が設けられる。ゲート領域はアクティブ領域3の外端部に接するように、下層、中層、上層のPエッジターミネーション領域7a、7b、7cが設けられる。裏側種面には、高濃度ドレイン層8が形成される。

(もっと読む)

窒化物半導体素子の製造方法

【課題】ドレインリーク電流を低減することが可能な窒化物半導体素子の製造方法を提供する。

【解決手段】ヘテロ電界効果トランジスタ1の製造方法は、ドリフト層20aを支持基板10上にエピタキシャル成長させる工程と、水素ガスをキャリアガスとして用いて、p型半導体層である電流ブロック層20bをドリフト層20a上に1000℃以上でエピタキシャル成長させる工程と、窒素ガス、アルゴンガス、ヘリウムガス及びネオンガスからなる群より選ばれる少なくとも一種のガスをキャリアガスとして用いて、コンタクト層20cを電流ブロック層20b上にエピタキシャル成長させる工程と、を備える。

(もっと読む)

半導体素子

【課題】低オン抵抗および高信頼性を有する半導体素子を提供する。

【解決手段】半導体素子1Aは、第1導電形層11が表面に選択的に設けられた半絶縁性基板10と、前記半絶縁性基板および前記第1導電形層の上に設けられたノンドープAlXGa1−XN(0≦X<1)を含む第1半導体層15と、前記第1半導体層上に設けられたノンドープもしくは第2導電形のAlYGa1−YN(0<Y≦1、X<Y)を含む第2半導体層16とを備える。半導体素子は、前記第2導電形層11に接続された第1主電極20と、前記第2半導体層16に接続された第2主電極と21、前記第1主電極と、前記第2主電極と、のあいだの前記第2半導体層の上に設けられた制御電極30とを備える。前記第1導電形層11は、前記制御電極30の下に設けられている。

(もっと読む)

窒化ガリウム系半導体装置および半導体装置の製造方法

【課題】窒化ガリウム系半導体のドライエッチングに、塩素系ガスを用いたICP−RIEを用いると、誘電結合型プラズマは、温度が高いので、エッチングされた面に凹凸ができ、半導体にダメージを与え、塩素が残留する。

【解決手段】窒化ガリウム系半導体からなる第1の半導体層を形成する第1半導体層形成工程と、第1の半導体層の一部を、臭素系ガスを用いて、マイクロ波プラズマプロセスでドライエッチングして、リセス部を形成するリセス部形成工程と、を備え、窒化ガリウム系半導体装置を製造する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】工程を簡素化して歩留まりを向上すると共に、安定した形状の電極を再現性よく得ることができる半導体装置の製造方法を提供する。

【解決手段】第1のレジスト膜11と、第1のレジスト膜11の開口よりも小さな開口を有する第2のレジスト膜12とを用いて、SiO2絶縁膜10を異方性ドライエッチングによってエッチングして、SiO2絶縁膜10にテーパ状の開口部101を形成する。このため、GaN層1を斜めに設置し直してSiO2絶縁膜10をエッチングする必要がなく、GaN層1を水平に設置したままSiO2絶縁膜10をエッチングすることができ、工程を簡素化できる。

(もっと読む)

半導体装置の製造方法

【課題】半導体の表面の酸化物を含む不純物を、エッチングあるいは、他の層を積層する前に除去する。

【解決手段】第1の半導体層110の少なくとも一部に接し、第1の半導体層110に含まれる不純物の固溶度が、第1の半導体層110より高い第1の犠牲層を形成する第1犠牲層形成工程と、第1の犠牲層および第1の半導体層をアニールするアニール工程と、第1の犠牲層をウェットプロセスで除去する除去工程と、第1の半導体層の少なくとも一部を覆う絶縁層120を形成する工程および第1の半導体層の一部をエッチングする工程の少なくとも一の工程と、第1の半導体層に電気的に接続された電極層126を形成する電極形成工程とを備える。

(もっと読む)

半導体装置

【課題】導体ベースプレート上に実装するSiCやダイヤモンドを基板とする高周波半導体チップの割れを防止する。

【解決手段】導体ベースプレートと、導体ベースプレート上に配置された高周波半導体チップとを備え、高周波半導体チップは、四隅が面取りされている半導体装置。

(もっと読む)

炭化ケイ素金属半導体電界効果トランジスタ及び炭化ケイ素の金属半導体電界効果トランジスタを製造する方法

【課題】深いレベルのドーパントがほとんど存在しない半絶縁性のSiC基板上にMESFETを形成することにより、バックゲート効果が減少された、SiCのMESFETを提供する。

【解決手段】半絶縁性の基板上10に選択的にドープされたP型の炭化珪素の層13、及びN型のエピタキシャル層14を積層し、背面ゲート効果を減少させる。また2つの凹部を有するゲート構造体も備える。これにより、出力コンダクタンスを1/3に減少することができ、また電力のゲインを3db増加することができる。クロム42をショットキーゲート接点として利用することもでき、酸化物−窒化物−酸化物(ONO)の保護層60を利用して、MESFET内の表面効果を減少させる。また、ソース及びドレインのオーム接点をn型チャネル層上に直接形成して、これにより、n+領域を製造する必要がなくなる。

(もっと読む)

パッケージ

【課題】導体ベースプレートと金属外壁との熱膨張係数が異なることに伴う、銀ロウ付けする際の導体ベースプレートの反りを抑制したパッケージを提供する。

【解決手段】導体ベースプレートと、導体ベースプレート上に配置された半導体装置と、半導体装置を内在し、導体ベースプレート上に配置され、導体ベースプレートと接する面に複数の開放部を有する金属壁と、開放部を充填するブロックとを備えるパッケージ。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度を得ながら、かつ、縦方向耐圧およびゲート電極端における耐圧の両方の耐圧性能を確実に得ることができる、半導体装置およびその製造方法を提供する。

【解決手段】 n型ドリフト層および該n型ドリフト層上に位置するp型層を含むGaN系積層体に、開口部が設けられ、開口部を覆うように位置する、チャネルを含む再成長層と、再成長層に沿って該再成長層上に位置するゲート電極とを備え、開口部はn型ドリフト層に届いており、ゲート電極の端は、平面的に見てp型層から外れた部分がないように位置していることを特徴とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】素子形成領域となる素子形成層の高品質化を実現し、また基板の反りを低減させると共に確実な素子分離を図り、信頼性の高い装置構成を得ることができる化合物半導体装置を実現する。

【解決手段】下地層3上に、素子分離領域に相当する部位に開口4aを有する第1のマスク4を形成し、開口4aを埋め込み、第1のマスク4上を覆うようにELO−GaN層5を成長し、ELO−GaN層5上に、素子形成領域に相当する部位に開口6aを有する第2のマスク6を形成し、開口6aを埋め込むように素子形成層7を形成する。

(もっと読む)

半導体装置

【課題】電流コラプスの発生を抑制できるIII族窒化物半導体トランジスタおよびその製造方法を提供する。

【解決手段】FET1では、第1窒化物半導体層103の上に第2窒化物半導体層104が設けられ、少なくとも一部が第2窒化物半導体層104に接するようにソース電極106およびドレイン電極107が設けられている。第2窒化物半導体層104の上面においてソース電極106とドレイン電極107との間に位置するように凹部110aが形成されており、ゲート電極108が凹部110aの開口を覆うように凹部110aの上方に設けられている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】GaN系の材料により形成されるHEMT(高電子移動度トランジスタ)をノーマリーオフ化させる。

【解決手段】基板11上に形成された第1の半導体層12と、前記第1の半導体層上に形成された第2の半導体層13と、所定の領域の前記第2の半導体層の一部または全部を除去することにより形成されているゲートリセス22と、前記ゲートリセス及び第2の半導体層上に形成されている絶縁膜31と、前記ゲートリセス上に絶縁膜を介して形成されているゲート電極32と、前記第1の半導体層または前記第2の半導体層上に形成されているソース電極33及びドレイン電極34と、を有し、前記ゲートリセスが形成されている領域における前記第2の半導体層、または、前記第2の半導体層及び前記第1の半導体層にはフッ素が含まれているフッ素を含む領域24を有する。

(もっと読む)

141 - 160 / 747

[ Back to top ]