Fターム[5F102GS01]の内容

接合型電界効果トランジスタ (42,929) | ゲート電極構造 (2,097) | 多層構造 (903)

Fターム[5F102GS01]の下位に属するFターム

3層以上 (156)

Fターム[5F102GS01]に分類される特許

21 - 40 / 747

半導体装置の製造方法

【課題】エピ抵抗や抵抗チップを用いることなく、奇モードのループ発振を抑えること。

【解決手段】本発明は、金属層60を形成する工程と、複数のFETそれぞれのゲートフィンガー14を共通に接続するゲートバスライン26のパターンのうち一部分を除いたパターンを有するめっき層64と、一部分の領域を被覆する第2マスク層66と、をマスクにして金属層60をパターニングすることで、ゲートバスライン26を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

III族窒化物半導体電子デバイス、III族窒化物半導体電子デバイスを作製する方法、及びエピタキシャルウエハ

【課題】AlNからなる半導体表面上に設けられると共に向上されたトランジスタ特性を有するIII族窒化物半導体電子デバイスを提供する。

【解決手段】5×107cm−2以下の転位密度を有しAlNからなる半導体表面21a上に、第1のエピタキシャル半導体層13はコヒーレントに設けられる。第2のエピタキシャル半導体層15は、第1のエピタキシャル半導体層13にヘテロ接合23aを成すように第1のエピタキシャル半導体層13上に設けられる。第1のエピタキシャル半導体層13がこの半導体表面21aへのコヒーレントな成長により、第1のエピタキシャル半導体層13は、半導体表面21aの格子定数に合わせて歪んであり、緩和していない。AlNに対してコヒーレントに設けられた第1のエピタキシャル半導体層13により、III族窒化物半導体電子デバイス11のトランジスタ特性が向上可能である。

(もっと読む)

半導体装置

【課題】窒化物半導体を用いたFETを樹脂封止パッケージに搭載した半導体装置の耐湿性を向上させること。

【解決手段】本発明は、窒化物半導体を用いたFETが形成されたチップ30と、前記チップがAgペースト22を用い搭載されたベース12と、前記チップ30を封止するガラス転移温度が190℃以上の樹脂20と、を具備する半導体装置である。

(もっと読む)

高効率および/または高電力密度のワイドバンドギャップトランジスタ

【課題】少なくとも4GHzの周波数で動作する場合に、40W/mm以上の電力密度を持つ電界効果トランジスタを提供する。

【解決手段】III族窒化物チャネル層16と、III族窒化物チャネル層16の上にあるゲート電極24と、ソース電極20と、ドレイン電極22と、ゲート電極24の上にある絶縁層72と、絶縁層72の上にあり、ソース電極20に電気的に連結するフィールドプレート74、とを備えた電界効果トランジスタ。

(もっと読む)

高電子移動度トランジスタ

【課題】電子移動度を低下させることなく、電子密度を高くできる高電子移動度トランジスタを提供する。

【解決手段】Si基板100上に形成されたバッファ層10と、バッファ層10上に形成されたGaN層11と、GaN層11上に形成されたAlGaN層12と、AlGaN層12内に形成されると共に、互いに間隔をあけて形成されたソース電極13とドレイン電極14と、AlGaN層12上かつソース電極13とドレイン電極14との間に形成されたゲート電極15と、ソース電極13とドレイン電極14およびゲート電極15が形成されたAlGaN層12の一部を覆うように形成された絶縁膜16とを備える。上記絶縁膜16中にCsの原子が2×1013cm−2以上存在する。

(もっと読む)

印刷可能な半導体構造、並びに関連する製造方法及び組立方法

【課題】選択された物理的寸法、形状、組成、及び、空間的配置を有する高品質印刷可能半導体素子の製造、転写、組み立てのための高歩留りの経路を与える。

【解決手段】大面積基板及び/又はフレキシブル基板を含む基板上へのミクロサイズ及び/又はナノサイズの半導体構造の配列の高精度の位置合わせ転写及び集積を行なう。また、バルクシリコンウエハ等の低コストバルク材料から印刷可能半導体素子を形成する方法、及び、広範囲の機能的な半導体デバイスを形成するための多目的で商業的に魅力的な印刷ベースの製造ブラットフォームを可能にするスマート材料処理を行う。

(もっと読む)

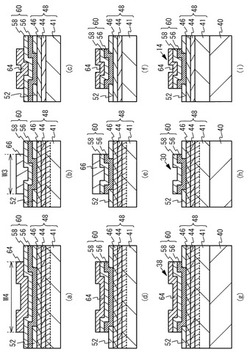

半導体装置およびその製造方法

【課題】閾値電圧を制度良く制御することが可能な半導体装置及びその製造方法を提供する。

【解決手段】基板10上に、窒化物半導体からなるチャネル層14と、チャネル層14よりもバンドギャップエネルギーの大きい第1窒化物半導体層16と、を順次形成する工程と、第1窒化物半導体層16上であって、ゲート電極26を形成すべき領域にダミーゲートを形成する工程と、ダミーゲートを形成した後、第1窒化物半導体層16上のダミーゲート以外の領域に、チャネル層14のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する第2窒化物半導体層18を再成長する工程と、ダミーゲートを除去した後、ダミーゲートを除去した領域の第1窒化物半導体層16上にゲート電極26を形成する工程と、を有する半導体装置の製造方法。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】動作電圧の高電圧化を図るも、電極端における電界集中を緩和してデバイス特性の劣化を確実に抑止し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を提供する。

【解決手段】HEMTは、SiC基板1上に、化合物半導体層2と、開口6bを有し、化合物半導体層2上を覆う、窒化珪素(SiN)の保護膜6と、開口6bを埋め込むように化合物半導体層2上に形成されたゲート電極7とを有しており、保護膜6は、その下層部分6aが開口6bの側面から張り出した張出部6cが形成されている。

(もっと読む)

化合物半導体装置の製造方法

【課題】化合物半導体積層構造上の絶縁膜に所期の微細な開口を形成するも、リーク電流を抑止した信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2上にパッシベーション膜6を形成し、パッシベーション膜6の電極形成予定位置をドライエッチングにより薄化し、パッシベーション膜6の薄化された部位6aをウェットエッチングにより貫通して開口6bを形成し、この開口6bを電極材料で埋め込むように、パッシベーション膜6上にゲート電極7を形成する。

(もっと読む)

半導体装置

【課題】高い障壁を有し、かつ高品質のバッファ層及びチャネル層を有する半導体装置を提供する。

【解決手段】基板10と、基板10上に設けられ、AlNからなる下地層12と、下地層12上に設けられ、AlxGa1−xNからなるバッファ層14と、バッファ層14上に設けられ、厚さが100nm以上300nm以下のGaNからなるチャネル層16と、チャネル層16上に設けられ、AlGaNからなる電子供給層20と、電子供給層20上に設けられたソース電極26、ドレイン電極28及びゲート電極30と、を具備し、バッファ層14のAlの組成xは、下地層12側の領域において0.3≦x≦0.5であり、チャネル層16側の領域において0.9≦x≦1.0である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を得る。

【解決手段】HEMTは、化合物半導体層2と、開口を有し、化合物半導体層2上を覆う保護膜と、開口を埋め込み、化合物半導体層2上に乗り上げる形状のゲート電極7とを有しており、保護膜は、酸素非含有の下層絶縁膜5と、酸素含有の上層絶縁膜6との積層構造を有しており、開口は、下層絶縁膜5に形成された第1の開口5aと、上層絶縁膜6に形成された第1の開口5aよりも幅広の第2の開口6aとが連通してなる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電極と化合物半導体層との界面に電極材料が到達することを抑止し、ゲート特性の劣化を防止した信頼性の高い高耐圧の化合物半導体装置を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成され、貫通口6aを有するパッシベーション膜6と、貫通口6aを埋め込むようにパッシベーション膜6上に形成されたゲート電極7とを有しており、ゲート電極7は、相異なる結晶配列の結晶粒界101が形成されており、結晶粒界101の起点が貫通口6aから離間したパッシベーション膜6の平坦面上に位置する。

(もっと読む)

窒化物電子デバイス、窒化物電子デバイスを作製する方法

【課題】リーク特性のばらつき幅を低減可能な、窒化物電子デバイスを作製する方法を提供する。

【解決手段】テトラメチルアンモニウムヒドロキシドを含む第1溶液を用いた処理を行って半導体積層53bに第1処理面65fを処理装置10dで形成する。第1溶液による処理温度は、摂氏50度以上摂氏100度以下である。第1溶液の濃度は5パーセント以上であり、50パーセント以下である。第1処理工程に引き続き第2処理工程を行う。第2処理工程では、テトラメチルアンモニウムヒドロキシド処理の後に、フッ化水素酸及び過酸化水素を含む第2溶液を用いた処理を半導体積層53bに行って半導体積層53bに第2処理面65gを処理装置10eで形成する。第2処理工程の後において、半導体積層53bの処理面65gのドナー性不純物の濃度は5×1017cm−3以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体層と電極との間に絶縁膜を介するMIS構造を採用するも、オン抵抗の上昇及び閾値の変動を抑止し、信頼性の高い半導体装置を得る。

【解決手段】AlGaN/GaN・HEMTは、化合物半導体積層構造2と、化合物半導体積層構造2の表面と接触する挿入金属層4と、挿入金属層4上に形成されたゲート絶縁膜7と、挿入金属層4の上方でゲート絶縁膜7を介して形成されたゲート電極8とを含み構成される。

(もっと読む)

半導体装置

【課題】電子が第1励起準位に存在する割合が増えても、量子井戸層の中の電子の有効質量が軽くなる井戸層にできるだけ多くの電子が存在するようにして、より一層の高速化を実現する。

【解決手段】半導体装置を、基板10の上方に設けられた第1半導体層11と、第1半導体層11の上側に接する電子走行層24と、電子走行層24の上側に接する第2半導体層17(25)とを備えるものとし、電子走行層を24、第1井戸層13、中間障壁層14、第2井戸層15を順に積層させた構造を含む2重量子井戸層とし、中間障壁層14の伝導帯のエネルギーが、第1半導体層11及び第2半導体層17(25)の伝導帯のエネルギーよりも低くなり、第1井戸層13及び第2井戸層15の中に基底準位が形成され、2重量子井戸層の中に第1励起準位が形成されるようにする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリオフ動作を実現しながら良好な伝導性能を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、電子供給層5とp型半導体層8との間に形成され、電子供給層5よりもバンドギャップが大きい正孔障壁層6と、が設けられている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁耐圧が高く、オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層13と、前記第1の半導体層の上に形成された第2の半導体層14と、前記第2の半導体層の上に形成された第3の半導体層15と、前記第3の半導体層の上に形成されたゲート電極21と、前記第2の半導体層に接して形成されたソース電極22及びドレイン電極23と、を有し、前記第3の半導体層には、半導体材料にp型不純物元素がドープされており、前記第3の半導体層は、前記ゲート電極の端部より、前記ドレイン電極が設けられている側に張出している張出領域を有していることを特徴とする半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層14と、第2の半導体層14の上に形成された第3の半導体層15と、第3の半導体層15の上に形成されたゲート電極21と、第2の半導体層14の上に形成されたソース電極22及びドレイン電極23と、を有し、第3の半導体層15には、半導体材料にp型不純物元素がドープされており、第3の半導体層において、ゲート電極の直下にはp型領域15aが形成されており、p型領域15aを除く領域は、p型領域15aよりも抵抗の高い高抵抗領域15bが形成されている半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】第1の極性を有する第1の化合物半導体層と共にこれと逆極性(第2の極性)の第2の化合物半導体層を用い、化合物半導体層の再成長をすることなく、第2の極性に対応した導電型の含有量が実効的に、容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧の化合物半導体装置を得る。

【解決手段】第1の極性を有する電子走行層2bと、電子走行層2bの上方に形成された第2の極性を有するp型キャップ層2eと、p型キャップ層2e上に形成された第1の極性を有するn型キャップ層2fとを有しており、n型キャップ層2fは、厚みの異なる部位2fa,2fbを有する。

(もっと読む)

半導体装置

【課題】格子整合したバッファ層、及び高い平坦性を有する接合界面を得ることが可能な半導体装置を提供すること。

【解決手段】本発明は、n−GaNからなる基板10と、基板10上に設けられ、InxAl1−xN(0.15≦x≦0.2)からなる第1バッファ層12と、第1バッファ層12上に設けられ、厚さ1nm以上10nm以下のAlNからなるスペーサ層14と、スペーサ層14上に設けられ、GaNからなるチャネル層16と、チャネル層16上に設けられ、窒化物半導体からなる電子供給層18と、を具備する半導体装置である。

(もっと読む)

21 - 40 / 747

[ Back to top ]