Fターム[5F102HC21]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | 熱処理(アニール) (453)

Fターム[5F102HC21]の下位に属するFターム

局部的アニール(レーザ、電子線照射) (10)

レジスト、ガラスの軟化 (1)

合金化、シリサイド化 (42)

Fターム[5F102HC21]に分類される特許

381 - 400 / 400

半導体装置の製造方法

【課題】AlGaN層の表面を平坦とし、かつ、AlGaN/GaN界面に存在する二次元電子ガスにダメージを与えない半導体装置の製造方法を提供する。

【解決手段】先ず、サファイア又は炭化珪素で形成される支持基板12を用意して、支持基板上にバッファ層14を堆積させる。次に、支持基板及びバッファ層を900℃以上1100℃以下に設定された成長温度に保持した状態で、バッファ層上に、GaN層16及びAlGaN層20を順次に積層してGaN半導体基板10を形成する。GaN半導体基板を形成する工程に引き続いて、GaN半導体基板を500℃以上成長温度以下の温度に保持した状態で、AlGaN層の上側表面28上に、表面保護膜としてAlN層30を形成する。

(もっと読む)

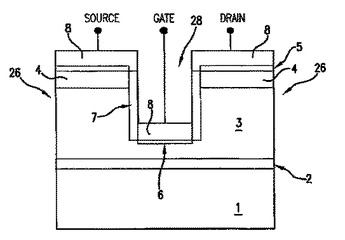

広いバンドギャップの半導体材料における横型トレンチ電界効果トランジスタ、該トランジスタを製造する方法、および該トランジスタを組み込む集積回路

接合電界効果トランジスタが記載される。このトランジスタは、広いバンドギャップの半導体から造られる。上記デバイスは、ソース、チャネル、ドリフトおよびドレインの半導体の層ならびにp型注入ゲート領域またはショットキーゲート領域を含む。上記ソース、チャネル、ドリフトおよびドレイン層は、エピタキシャルに成長され得る。上記ソース、ゲートおよびドレイン領域に対するオーム接触は、ウェーハと同じ側に形成され得る。上記デバイスは、垂直チャネル幅に依存する異なる閾電圧を有し得、同じチャネルドーピングに対し、デプレッション動作モードおよびエンハンス動作モードの両方に対して実施され得る。上記デバイスは、デジタル、アナログおよびモノリシックなマイクロ波集積回路のために使用され得る。上記デバイスを含むトランジスタおよび集積回路を製造する方法もまた、記載される。  (もっと読む)

(もっと読む)

窒化物ベースのトランジスタ及びトランジスタ構造体のキャップ層及び/又は不活性層並びにそれらの製造方法

不均一アルミニウム濃度のAlGaNをベースとするキャップ層を備えるIII族窒化物高電子移動度トランジスタが提供される。このキャップ層は、それが上に設けられたバリア層から遠い方のその表面付近に高い濃度のアルミニウム濃度を有する。キャップ層を備える高電子移動度トランジスタが提供される。このキャップ層は、それが上に設けられるバリア層から遠い方のその表面付近にドープ領域を有する。広バンドギャップ半導体デバイスの黒鉛状BN不活性構造体が提供される。また、III族窒化物半導体デバイスのSiC不活性構造体が提供される。また、不活性構造体の酸素アニールも提供される。また、凹部のないオーミックコンタクトも提供される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 耐圧特性の低下、ゲート電極におけるリーク電流の増加などのような不利益な結果をもたらすことなく接触抵抗を低減する。

【解決手段】 半導体装置は、AlxInyGa1-x-yN(0≦x<1,0≦y<1)からなる層を含むチャネル層1の上側にAlzGa1-zN(0≦z≦1)からなる第1種層を含む電子供給層2が形成され、チャネル層1と電子供給層2とがヘテロ接合されている窒化物半導体へテロ接合型電界効果トランジスタであって、電子供給層2の上側にゲート電極4、ソース電極3およびドレイン電極5が配置されており、電子供給層2は、ゲート電極4の下側の部分では不純物濃度が1E18cm-3以下のn型となっている。ソース電極3およびドレイン電極5の下側の部分では不純物濃度が1E18cm-3より多いn型となっている。

(もっと読む)

半導体装置及びその製造方法

窒化物半導体層を含む半導体装置は、シリコン基板1の上にAlNから成る第1の層8とp型GaNから成る第3の層10とCaNから成る第2の層9とを交互に複数積層した構造のバッファ層2を有する。バッファ層2の上にHEMTを形成するための窒化物半導体層を含む主半導体領域3を有する。第3の層10の厚みは0.5〜50nmである。第3の層10は2次元電子ガスの発生を抑制する効果を有する。これにより、バッファ層2の低抵抗化が防止される。  (もっと読む)

(もっと読む)

III族窒化物半導体光素子

【課題】III族窒化物半導体を容易に加工することのできる技術により実現される新規な素子構造を提供する。

【解決手段】半導体レーザは、p型GaNガイド層307と、p型GaNガイド層307上に形成された、AlN層である電流狭窄層308と、電流狭窄層308の開口部を埋め込むように形成されたp型クラッド層309とを有する。

(もっと読む)

ショットキー電極の製造方法

【課題】理想的な特性に近いショットキー電極を製造する方法を提供する。

【解決手段】GaAs基板101にリセス107を形成するためのエッチングを行う際に、このリセス107の表面に、水酸基を多く含むGa酸化膜108が形成される。このGa酸化膜108はショットキー電極の特性を悪化させる原因になる。このため、エッチング後、このGaAs基板101をホットプレートで加熱することにより、このGa酸化膜108から水酸基を取り除き、絶縁性の高いGa酸化膜109に変質させる。その後、Ga酸化膜109上にショットキー電極111を形成し、レジストパターン106や金属層110を取り除いた後、保護膜113を形成する。この発明によれば、Ga酸化膜108内の水酸基が水に変化する反応を加熱処理によって促進させることができ、これにより水酸基を取り除くことができるので、理想的な特性に近いショットキー電極111を得ることができる。

(もっと読む)

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。したがって、埋込み部を形成する際のエッチングにより損傷をきたした埋込みゲートを提供することによって生じ得るゲート領域劣化が低減された、高品質のゲートコンタクトおよびオーミックコンタクトを提供することができる。  (もっと読む)

(もっと読む)

窒化物系化合物半導体装置及びその製造方法

【課題】 極めて簡単な手段を採ることで、窒化物系化合物半導体と電極との接触抵抗を低下させ、また、電極表面及び電極パターンエッジのモフォロジを良好に維持することを可能にして高い信頼性を実現できるようにする。

【解決手段】 金属窒化物、例えばTiNを含む第1の層及びMox Ga1-x (0<x<1)を含む第2の層が半導体に近い側から前記の順に積層されてなる電極を備えてなることが基本になっている。

(もっと読む)

半導体装置とその製造方法

【課題】 ヘテロ構造を備えているとともにIII-V族化合物半導体で構成される半導体装置において、安定的なノーマリオフ動作を実現する。

【解決手段】 p−GaN層32とSI−GaN層62とAlGaN層34が積層され、AlGaN層34の表面側にショットキー接続されているゲート電極44を備えている半導体装置である。p−GaN層32とSI−GaN層62よりもAlGaN層34のバンドギャップの方が大きく、さらに、SI−GaN層62は、その不純物濃度が1×1017cm-3以下であることを特徴としている。

(もっと読む)

再成長オーミックコンタクト領域を有する窒化物ベースのトランジスタの製作方法及び再成長オーミックコンタクト領域を有する窒化物ベースのトランジスタ

トランジスタ製作は、基板上に窒化物ベースのチャネル層を形成すること、窒化物ベースのチャネル層上に障壁層を形成すること、窒化物ベースのチャネル層のコンタクト領域を露出させるように障壁層にコンタクト凹部を形成すること、例えば、低温堆積プロセスを使用して、窒化物ベースのチャネル層の露出されたコンタクト領域上にコンタクト層を形成すること、コンタクト層上にオーミックコンタクトを形成すること、及びオーミックコンタクトに隣接した障壁層上に配置されたゲートコンタクトを形成すること、を含んでいる。また、高電子移動度トランジスタ(HEMT)及びHEMTの製作方法が提供される。HEMTは、基板上の窒化物ベースのチャネル層と、窒化物ベースのチャネル層上の障壁層と、チャネル層の中まで延びる、障壁層のコンタクト凹部と、コンタクト凹部の中の窒化物ベースのチャネル層上の窒化物ベースのn型半導体材料のコンタクト領域と、窒化物ベースのコンタクト領域上のオーミックコンタクトと、このオーミックコンタクトに隣接した障壁層上に配置されたゲートコンタクトと、を含んでいる。窒化物ベースのn型半導体材料のコンタクト領域及び窒化物ベースのチャネル層は、表面積拡大構造を含んでいる。  (もっと読む)

(もっと読む)

自己整列型炭化ケイ素半導体デバイスおよびそのデバイスの作成方法

電流安定性の改善された自己整列型炭化ケイ素パワーMESFETおよびそのデバイスの作成方法を記載する。このデバイスは、ゲート凹部により分離されたレイズドソースおよびドレイン領域を含み、低ゲートバイアスにおいてでさえ表面トラップ効果が低減されるため、電流安定性が改善される。このデバイスは自己整列型プロセスを用いて作成され得る。このプロセスでは、金属エッチマスクを用いて、nドープのSiCチャネル層上のn+ドープのSiC層を備えた基板がエッチングされてレイズドソースおよびドレイン領域が規定される。この金属エッチマスクがアニールされ、ソースおよびドレイン・オームコンタクトが形成される。単層または多層の誘電性フィルムが成長または堆積され異方性エッチングされる。蒸着または別の異方性堆積技術を用いて、ショットキーコンタクト層および最終金属層が堆積され、オプションとして、誘電性層の等方エッチングされる。  (もっと読む)

(もっと読む)

ショットキ・コンタクトを形成するために半導体上に導電性炭素材料を堆積するための方法、及び半導体コンタクト・デバイス

【課題】 本発明は、ショットキ・コンタクト(16)を形成するために半導体(14)上に導電性炭素材料(17)を堆積する方法に関する。

【解決手段】 本発明の方法は、半導体(14)をプロセス・チャンバ(10)内に導入するステップと、プロセス・チャンバ(10)の内部(10')を所定温度に加熱するス

テップと、プロセス・チャンバ(10)を第1所定圧力以下に減圧するステップと、プロセス・チャンバ(10)の内部(10')を第2所定温度に加熱するステップと、少なく

とも炭素を含むガス(12)を、第1所定圧力よりも高い第2所定圧力に達するまで導入するステップと、少なくとも炭素を含むガス(12)から、半導体(14)上に導電性炭素材料(17)を堆積することにより、半導体(14)上に堆積した炭素材料(17)がショットキ・コンタクト(16)を形成するステップを備えている。

(もっと読む)

炭化珪素半導体素子及びその製造方法

半導体素子の製造方法は、炭化珪素基板1上に形成された炭化珪素薄膜2内にイオンを注入する工程と、炭化珪素基板を減圧雰囲気で加熱することで炭化珪素基板の表面にカーボン層5を形成する工程と、カーボン層5を形成する工程より高い圧力で、且つ高い温度の雰囲気中で炭化珪素基板を活性化アニールする工程とを含んでいる。 (もっと読む)

保護層および低損傷陥凹部を備える窒化物ベースのトランジスタならびにその製作方法

窒化物ベースの半導体チャネル層上に窒化物ベースの半導体バリア層を形成すること、および窒化物ベースの半導体バリア層のゲート領域上に保護層を形成することによって、トランジスタが製作される。パターニングされたオーム性接触金属領域が、バリア層上に形成され、第1および第2のオーム性接触を形成するためにアニールされる。アニールは、保護層をゲート領域上に載せたままで実施される。バリア層のゲート領域上に、ゲート接点も形成される。ゲート領域内に保護層を有するトランジスタも形成され、バリア層の成長させたままのシート抵抗と実質的に同じシート抵抗をもつバリア層を有するトランジスタも同様である。  (もっと読む)

(もっと読む)

ダイアモンド基板上炭化珪素並びに関連するデバイス及び方法

ワイドバンドギャップ材料内に、接合温度低下、動作中の高電力密度化、及び定格電力密度における信頼性向上を達成する高電力デバイスを形成する方法を、結果的に得られる半導体構造及びデバイスと共に開示する。本方法は、ダイアモンドの層を炭化珪素ウェハに添加して、得られる複合ウェハの熱伝導率を高め、その後、炭化珪素の上におけるエピタキシャル成長を支持するためにその十分な厚さを保持しつつ、複合ウェハの炭化珪素部分の厚さを削減し、複合ウェハの炭化珪素面を、その上におけるエピタキシャル成長のために、準備し、第III族窒化物ヘテロ構造を、ウェハの準備した炭化珪素面に添加することを含む。  (もっと読む)

(もっと読む)

III族窒化物素子の不動態化およびその方法

【課題】

【解決手段】III族窒化物半導体素子およびその製造方法の実施形態は、高温処理中にIII族窒化物材料に損傷を与えずに、素子のコンタクトを形成することを可能にする低抵抗の不動態化層を備えてよい。不動態化層は、素子全体を不動態化するために用いられてよい。不動態化層は、さらに、素子のコンタクトと活性層との間に設けられて、導電のための低抵抗の電流路を提供してもよい。この不動態化処理は、FET、整流器、ショットキダイオードなど、任意の種類の素子に用いて、破壊電圧を改善すると共に、コンタクトの接合部付近の電界集中効果を防止してよい。不動態化層は、外部拡散に関してIII族窒化物素子に影響を与えない低温アニールで活性化されてよい。

(もっと読む)

モノリシック集積型エンハンスメントモードおよびデプリーションモードFETおよびその製造方法

【課題】 製造コストを低減し品質の均一性および安定性を高めたモノリシック集積型エンハンスメントモード/デプリーションモードFETデバイスを提供する。

【解決手段】 単一の半導体多層構造でデプリーションモード(Dモード)FETをエンハンスメントモード(Eモード)FETとモノリシックに集積回路化する。上記多層構造にはチャネル層を設け、その上に障壁層をオーバーレイし、さらにその上にオームコンタクト層をオーバーレイする。これらDモードFETおよびEモードFETのソースコンタクトおよびドレーンコンタクトをオームコンタクト層に接続する。またDモードFETおよびEモードFETのゲートコンタクトを障壁層に接続する。障壁層の中のEモードゲートコンタクトの下に非晶質化領域を設ける。この非晶質化領域が障壁層との間の埋込みEモードSchottkyコンタクトを構成する。代わりに実施例ではDモードFETのゲートコンタクトを障壁層にオーバーレイした第1の層に接続し、その第1の層の中にDモード非晶質化領域を形成する。

(もっと読む)

化合物半導体層の表面処理方法及び半導体装置の製造方法

【課題】窒素を含む化合物半導体層の表面に生じた、エッチングによるダメージを除去あるいは軽減し、ゲート電極に良好なショットキ特性を有する半導体装置を形成する。

【解決手段】ドライエッチングにより、第1化合物半導体層22のゲート電極形成予定領域36の表面を露出するとともに、コンタクト層32を形成する。次いで、この第1化合物半導体層22の露出した表面に対するアニール処理を行う。前述のドライエッチングの際に第1化合物半導体層22の表面に生じたダメージを、窒素プラズマを用いた表面処理を行うことにより、良好な電気特性をもつ第1化合物半導体層22の表面を形成する。この窒素プラズマを用いた表面処理を行った第1化合物半導体層22の表面上にゲート電極38を形成し、良好なショットキ特性を有するゲート電極を具えたリセス型HEMT10を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート長の短いゲート電極を有し、しかも低抵抗で高周波特性が優れている半導体装置およびその製造方法を提供する。

【解決手段】少なくともノンドープInGaP層又はノンドープInAlGaP層からなる上層半導体層12と、この上層半導体層直下にGaAs層またはAlGaAs層からなる下層半導体層11を含む半導体基板に、上層半導体層表面から上層半導体層への浸入が、下層半導体層で略停止するショットキーゲート電極15と、このショットキーゲート電極部に接続して第1の電極の抵抗を低減する第2の電極部16からなるT字型ゲート電極を形成する。

(もっと読む)

381 - 400 / 400

[ Back to top ]