Fターム[5F110AA03]の内容

Fターム[5F110AA03]に分類される特許

641 - 660 / 732

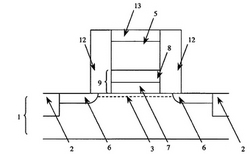

半導体装置

【課題】 ショットキー型電界効果トランジスターに於いて、殊にソース領域近傍のチャネル領域に対するゲート電極の制御性を高めて、素子の電流駆動能力の向上を図る。

【解決手段】 ゲート絶縁膜を異なる誘電率を持つ膜の積層とすることで、誘電率の高い材料のみで形成した場合と比べてゲート絶縁膜の幾何学的な意味の厚さを薄く形成することを可能とし、ゲート電極から出た電気力線のゲート絶縁膜の側面から外への漏れに起因する、殊にソース領域近傍のチャネル領域の電位に対するゲート電極の制御性の低下を抑制する事が可能となる。また、誘電率の高い材料よりなるゲート側壁絶縁膜12を設ける事に依り、異なる誘電率を持つ物質の界面に於ける電気力線の屈折に依って、ゲート電極から出た電気力線をソース領域近傍のチャネル領域に集める事が可能となり、ソース領域とチャネル領域との間に形成されるショットキー障壁を薄くし、その抵抗を低減する。

(もっと読む)

電気光学装置及びその製造方法、並びに電子機器

【課題】 電気光学装置の駆動回路において、TFTの半導体層と配線との電気的接続に係る抵抗を小さくし、更には当該駆動回路の動作不良を防止して消費電流を小さくする。

【解決手段】 駆動回路は、相補型トランジスタを構成するnチャネル型の第1TFT及びpチャネル型の第2TFTと、第1TFTの半導体層と層間絶縁膜に開孔された第1コンタクトホールを介して電気的に接続されるか、又は第2TFTの半導体層と層間絶縁膜に開孔された第2コンタクトホールを介して電気的に接続される配線と、配線と第1TFTの半導体層との電気的接続に係る第1抵抗と、配線と第2TFTの半導体層との電気的接続に係る第2抵抗とを相互に近付けるように、第1又は第2TFTの半導体層より下層側に、第1又は第2コンタクトホールと重畳的に形成された導電性のシート層とを備える。

(もっと読む)

表示装置およびその製造方法

【課題】 液晶表示装置において、Crなどからなるソース電極およびドレインライン用外部接続端子とITOなどの金属酸化物からなる画素電極および上層ドレインライン用外部接続端子との間の接続抵抗値を低くする。

【解決手段】 画素電極18および上層ドレインライン用外部接続端子24は、オーバーコート膜16に形成されたコンタクトホール17、23を介して、ソース電極7およびドレインライン用外部接続端子21上に設けられた、ITOなどからなる金属酸化膜11、22に接続されている。そして、オーバーコート膜16にコンタクトホール17、23をドライエッチングにより形成するとき、コンタクトホール17、23を介して露出される金属酸化膜11、22の上面はドライエッチングによるプラズマダメージに強く、またエッチングガスにさらされても変質することはない。

(もっと読む)

半導体装置、半導体装置の製造方法、電気光学装置及び電子デバイス

【課題】 ソース・ドレイン電極と半導体膜とのコンタクト不良を抑制することが可能な半導体装置等を提供する。

【解決手段】 両端部30s、30dの膜厚が平坦部30cの膜厚よりも厚い半導体膜30を形成する。ゲート絶縁膜40は、両端部30s、30dが露出されるように形成される。両端部30s、30dには、ソース・ドレイン電極50s、50dとソース・ドレイン領域とを接続する中間電極50s、50dが形成され、この中間電極50s、50dまで開口するコンタクトホールが形成される。

(もっと読む)

表示装置用配線、薄膜トランジスタ表示板及びその製造方法

【課題】本発明は、表示装置用配線及び前記配線を含む薄膜トランジスタ表示板に関する。

【解決手段】本発明は、銅(Cu)とモリブデン(Mo)、タングステン(W)、及びクロム(Cr)から選択された少なくとも一つの金属を含有する銅合金からなる表示装置用配線、並びに、基板、前記基板上に形成されているゲート線、前記ゲート線と交差するデータ線、前記ゲート線及び前記データ線に接続されている薄膜トランジスタ、及び前記薄膜トランジスタに接続されている画素電極を含み、前記ゲート線及び前記データ線のうちの少なくとも一つは、銅(Cu)とモリブデン(Mo)、タングステン(W)、及びクロム(Cr)から選択された少なくとも一つの金属を含有する合金からなる薄膜トランジスタ表示板を提供する。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに薄膜トランジスタ基板及びその製造方法並びに該薄膜トランジスタを用いた液晶表示装置及び有機EL表示装置並びに透明導電積層基板

【課題】 透明電極である第2電極と、第1電極(ゲート、ソース、ドレイン)とのコンタクト部のコンタクト抵抗を低減し、電池反応を抑制する。

【解決手段】 透明絶縁性基板上に、Al合金を用いて、第1電極である薄膜トランジスタの第1電極(ソースなど)を形成する工程と、第1電極及び基板を覆って絶縁膜を成膜する工程と、絶縁膜にコンタクトホールを形成する工程と、絶縁膜上に第2電極(透明電極)を形成し、第2電極と第1電極とを前記コンタクトホールを介して電気的に直接接続する工程と、を含み、Al合金は、Niと、{Mo、Nb、W、Zr}から選択された一種以上の金属と、を含むAl合金であることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 異なるゲート長またはゲート幅を有し、フルシリサイド化されたゲート電極を備えた半導体装置を提供する。

【解決手段】 半導体装置100は、半導体基板5と、半導体基板上に形成された第1のゲート絶縁膜51と、半導体基板上に形成された第2のゲート絶縁膜52と、第1のゲート絶縁膜上に形成され、フルシリサイド化された第1のゲート電極11と、第2のゲート絶縁膜上に形成され、フルシリサイド化された第2のゲート電極12であって、半導体基板の表面を占める面積が第1のゲート電極よりも大きく、なおかつ、第1のゲート電極よりも厚みが薄い第2のゲート電極12とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】フルシリサイド化されたゲート電極(フルシリサイドゲート電極)を有する半導体装置であっても、接合リーク電流増大の問題なく、ソースドレイン領域に形成された金属シリサイド膜の膜厚を厚く形成することが可能であり、かつ一回のシリサイド形成工程でフルシリサイドゲート電極及び金属シリサイド膜を形成可能な半導体装置及びその製造方法を提供する。

【解決手段】上主面が半導体基板1より高くなるように金属シリサイド膜11を形成する。金属シリサイド膜11と半導体基板1からなる界面Aと、ソースドレイン拡散層8と半導体基板1からなる界面Bとの距離が十分確保できるように、金属シリサイド膜11の膜厚を厚く形成できる。その結果、フルシリサイドゲート電極10を形成した場合であっても、接合リーク電流の増大を回避しつつ、金属シリサイド層11の膜厚を厚くできる。

(もっと読む)

TFT基板及びその製造方法

【課題】 特定の金属を含有する透明導電材料を画素電極、透明電極に使用することにより、TFT(薄膜トランジスタ)基板の製造方法を簡略化する。

【解決手段】 表示装置に用いられるTFT基板であって、透明基板と、前記透明基板上に設けられ、前記表示装置の画素を制御する画素電極と、前記透明基板上に設けられ、前記画素電極を駆動する薄膜トランジスタと、を備え、前記薄膜トランジスタは、少なくとも、Alゲート電極と、ゲート絶縁膜と、第1の半導体層と、第2の半導体層と、Alソース・ドレイン電極と、を含み、前記画素電極は、前記Alゲート電極及び/又は前記Alソース・ドレイン電極と直接接合し、当該画素電極が、酸化亜鉛を主成分とする導電性酸化物よりなることを特徴とするTFT基板である。バリヤーメタルを設けていないので、製造工程を簡略化することができる。

(もっと読む)

半導体装置とその製造方法

【課題】

フィン型構造を持つ電界効果トランジスタのソース/ドレインのコンタクト抵抗を低減する。

【解決手段】

半導体装置の製造方法は、第1の高さのフィン型半導体領域うえに、第1の高さより高い第2の高さの絶縁ゲート電極構造を形成し、サイドウォール絶縁膜をフィン型半導体領域の側面からは完全に異方性エッチングで除去し、フィン型半導体領域近傍のゲート電極両側面ではフィン型半導体領域の上面、側面をサイドウォール絶縁膜が囲むように、ゲート電極両側面上下部を残して上部上からエッチング除去し、フィン型半導体領域の少なくとも露出している両側面に上端から下端までシリサイド層を形成する。層間絶縁膜形成後、フィン型半導体領域の両側面のシリサイド層を露出するコンタクトホールを形成し、導電性プラグを埋め込む。

(もっと読む)

酸化物透明導電膜材料及びAl配線を備えた透明導電膜積層回路基板及びその製造方法。

【課題】 特定の金属を含有する透明導電材料を透明導電膜に使用することにより、Al配線を設けた積層回路基板の製造方法を簡略化する。

【解決手段】 酸化亜鉛−酸化スズを主成分とする酸化物であって、

30℃のテトラメチルアンモニウムハイドロオキサイド(TMAH)2.4%水溶液中のAg/AgCl標準電極を基準とした起電力が−0.6V以下であることを特徴とする非晶質酸化物透明導電膜材料。この材料を用いてAl配線を備えた透明基板上に透明導電膜を成膜すれば、バリヤーメタル等を用いなくても、TMAHを用いた現像処理を行っている最中にAl配線が溶出することがない。さらに、Al配線と透明導電膜との接触抵抗を小さくすることができる。

(もっと読む)

Al配線を備えた透明導電膜積層基板及びその製造方法。

【課題】 特定の金属を含有する透明導電材料を透明導電膜に使用することにより、Al配線を設けた積層基板の製造方法を簡略化する。

【解決手段】 透明基板と、前記透明基板上に設けられたAl配線と、酸化亜鉛を主成分とする導電性酸化物からなり、前記Al配線に直接接合する透明導電膜と、を含むことを特徴とするAl配線を備えた透明導電膜積層基板である。バリヤーメタルを間に設けず、直接Al配線と透明導電膜が直接接合しているので、製造工程を簡略化することができる。

(もっと読む)

半導体装置とその製造方法

【課題】

フィン型構造を持つ電界効果トランジスタのソース/ドレインのコンタクト抵抗を低減する。

【解決手段】

半導体装置は、絶縁性表面を有する支持基板上に形成され、ほぼ垂直な一対の側面および前記両側面を接続する上面を有し、第1導電型を有するフィン型半導体領域と、前記フィン型半導体領域の中間部を横断して形成され、フィン型半導体領域の側面に倣う側壁を有する絶縁ゲート電極構造と、ゲート電極両側のフィン型半導体層に形成された、第1導電型と逆の第2導電型を有するソース/ドレイン領域と、導電性ゲート電極の側壁上に形成された部分を含み、ソース/ドレイン領域上において、前記フィン型半導体領域の側面の上端から下端に達する開口を有するサイドウォール絶縁膜と、サイドウォール絶縁膜の開口内に露出されたソース/ドレイン領域の表面に形成されたシリサイド層と、シリサイド層にコンタクトするソース/ドレイン電極と、を有する。

(もっと読む)

薄膜トランジスタ

【課題】アクティブマトリクス型の液晶表示装置において、薄膜トランジスタの点欠陥や線欠陥を完全に排除するのは極めて困難であるのが現状である。その原因の1つである薄膜トランジスタのコンタクト不良を低減することを課題とする。

【解決手段】薄膜トランジスタの層間絶縁膜に設けられたソース領域又はドレイン領域に達する第一のコンタクトホールと、層間絶縁膜に設けられたゲート電極に達する第二のコンタクトホールと、第一のコンタクトホール及び第二のコンタクトホールにそれぞれ形成された配線とを有し、該配線に第一のチタン膜と、アルミニウム又はアルミニウムを主成分とする膜と、第二のチタン膜とが積層した構造を用い、且つアルミニウム又はアルミニウムを主成分とする膜がアルミニウム又はアルミニウムを主成分とする膜に流動性を付与する元素を有することにより、コンタクト不良を低減することができる。

(もっと読む)

表示装置

【課題】プロジェクタ等に用いられるアクティブマトリクス型の表示装置において、補助容量と、遮光膜またはシールドパターンを備えた構成について提案する。

【解決手段】本発明に係る表示装置は、薄膜トランジスタを有する画素マトリクス回路を用いた表示装置であって、当該薄膜トランジスタ上に順次形成された第1の絶縁膜、第1および第2の電極、窒化珪素膜、電極パターンと、窒化珪素膜および電極パターン上に形成された第2の絶縁膜と、当該第2の絶縁膜上に順次形成された遮光膜、第3の絶縁膜と、当該第3の絶縁膜上に形成され、第1の電極に接続された画素電極と、を有し、第1の電極、窒化珪素膜、電極パターンによって、容量が形成されることを特徴とする。

(もっと読む)

高い誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法

【課題】

高誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法を提供する。

【解決手段】

本発明の金属化合物は、TiCを含み、約4.75乃至約5.3eV、望ましくは、約5eVの仕事関数を有し且つ高誘電率の誘電体および界面層を含むゲート積層体上で熱的に安定する。更に、そのTiC金属化合物は、非常に意欲的な等価酸化膜厚(EOT)およびp型金属酸化物半導体(pMOS)装置における14Åよりも小さい反転層厚へのスケーリングを可能にする1000℃においても非常に効率的な酸素拡散バリアである。

(もっと読む)

有機電界効果トランジスタ及び半導体装置

【課題】導電層と半導体層との界面のエネルギー障壁を低減できる電極を有する有機電界効果トランジスタ及び有機電界効果トランジスタを有する半導体装置を提供することを課題とする。

【解決手段】有機電界効果トランジスタ用の電極、すなわち有機電界効果トランジスタにおけるソース電極及びドレイン電極の少なくとも一方の一部に、有機化合物と金属酸化物とを含む複合層を用いる。または、さらにアルカリ金属等を含む層を設けた電極とする。

(もっと読む)

半導体装置、表示装置、及びそれらの作製方法、並びにテレビジョン装置

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な半導体装置、表示装置及びその作製技術を提供することを目的とする。また、それらの半導体装置、表示装置を構成する配線等のパターンを、所望の形状で密着性よく形成できる技術を提供することも目的とする。

【解決手段】第1の導電層と第2の導電層の間に、導電性の有孔バッファ層を形成することによって、第1の導電層と第2の導電層との密着性を高める。有孔バッファ層が有する孔に、粒子状の導電性材料を侵入させ、焼成によって固化し、第2の導電層を形成する。孔内で固化した導電層がくさびのような働きをし、この働く力によって、第2の導電層は、第1の導電層と密着性よく安定して形成される。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程でNiシリサイドを形成する。

【解決手段】基板上に半導体膜を形成し、前記基板を加熱しながら前記半導体膜上にNi膜を成膜することにより、前記半導体膜にNiシリサイドを形成することを特徴とする。また基板上に半導体膜を形成し、前記基板を450℃以上に加熱しながら前記半導体膜上にNi膜を成膜することにより、前記半導体膜にNiシリサイドを形成することを特徴とする。また基板上に半導体膜を形成し、前記基板を450℃以上に加熱しながら前記半導体膜上にNi膜を10nm以上成膜することにより、前記半導体膜にNiシリサイドを形成することを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】ゲート電極や配線を低抵抗な金属膜を用いて形成することにより、大面積なデバイスにも対応できる半導体装置の作製方法を提供する。

【解決手段】基板上にアルミニウムを主成分とする第1の導電層を形成し、前記第1の導電層上に当該第1の導電層と異なる材料からなる第2の導電層を形成し、前記第1の導電層及び前記第2の導電層をパターニングしてゲート電極を形成することを特徴とする。また、前記第1の導電層は、炭素と、クロム、タンタル、タングステン、モリブデン、チタン、シリコン、ニッケルのいずれか一又は複数を含有していることを特徴とする。前記第2の導電層は、クロム、タンタル、タングステン、モリブデン、チタン、ニッケルまたはこれらの窒化物のいずれか一又は複数からなることを特徴とする。

(もっと読む)

641 - 660 / 732

[ Back to top ]