Fターム[5F110AA03]の内容

Fターム[5F110AA03]に分類される特許

701 - 720 / 732

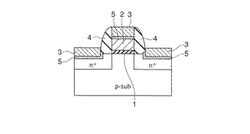

半導体装置

【課題】 原子レベルで平坦な界面をもって基板上に堆積され、しかも低抵抗のシリサイド層を有する半導体装置を提供する。

【解決手段】 素子分離領域を有する半導体基板と、前記半導体基板に形成された拡散領域と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、前記拡散領域上に形成されたシリサイド層(3)とを具備するMISトランジスタを含む半導体装置である。前記シリサイド層は、前記半導体基板との界面にEr、Gd、Tb、Dy、Ho、Tm、Yb、Lu、およびPtからなる群から選択される少なくとも1種の金属のシリサイドからなる界面層(5)を有することを特徴とする。

(もっと読む)

LCDのTFT基板及びその製造方法

【課題】 液晶表示装置の薄膜トランジスタ基板及びその製造方法が開示されている。

【解決手段】 シリコン元素を含む基板、前記基板上に形成された拡散防止膜、及び前記拡散防止膜上に形成され、前記拡散防止膜形成物質が0.5〜15at%範囲で含まれた銅合金層を含んで形成される。前記拡散防止膜は、Zr、Ti、Hf、V、Ta、Ni、Cr、Nb、Co、Mn、Mo、W、Rh、Pd、Pt等のような化合物を50〜5000Å範囲で蒸着して熱処理して、シリサイド化合物に変換して製造する。銅合金配線を用いてトランジスタ基板を製造するので、低い抵抗と高い伝導度を具現することができる。又、薄い厚さの拡散防止膜と同じ元素を添加した銅合金と用いて銅配線を形成したので、同時エッチングが可能であり、後続工程で基板との相互拡散を防止することができる。  (もっと読む)

(もっと読む)

サリサイド工程及びこれを利用した半導体素子の製造方法

【課題】サリサイド工程及びこれを利用した半導体素子の製造方法を提供する。

【解決手段】 本発明による金属シリサイド膜の形成方法は、シリコン領域を備える基板を準備する段階と、前記基板上にシリコン層を形成する段階と、前記シリコン層と接触する金属膜を形成する段階と、前記金属膜を有する基板を熱伝達気体を採択した対流または伝導方式を使用して等温熱処理して前記少なくとも前記金属膜の一部を金属シリサイド膜に転換する段階と、を含む。

(もっと読む)

半導体装置

【課題】特性の優れた薄膜トランジスタ(TFT)およびTFTを有する半導体集積回路を提供する。

【解決手段】周辺回路およびアクティブマトリクス回路を含む半導体装置において、前記周辺回路および前記アクティブマトリクス回路は、第1の絶縁膜を介して半導体層の下に設けられた第1のゲイト電極および第2の絶縁膜を介して前記半導体層の上に設けられた第2のゲイト電極を含む複数の薄膜トランジスタを含み、前記周辺回路の薄膜トランジスタの半導体層に結晶性半導体が用いられ、前記アクティブマトリクス回路の半導体層に非晶質半導体が用いられたことを特徴とする。

(もっと読む)

電界効果型トランジスタ

【課題】チャネル領域を構成する有機半導体材料層と良好なオーミック・コンタクトを形成することができるソース/ドレイン電極を備えた電界効果型トランジスタを提供する。

【解決手段】電界効果型トランジスタは、ゲート電極12と、ゲート絶縁層13と、ソース/ドレイン電極21と、チャネル領域15を構成する有機半導体材料層14とを備え、ソース/ドレイン電極21は、金属から成る導体部22、及び、導体部22を少なくとも部分的に被覆し、不純物がドーピングされた有機導電材料層23から成り、有機導電材料層23を介して、チャネル領域15と導体部22との間の電気的接続が形成される。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】ゲート絶縁膜のうち、ソース・ドレイン電極及びゲート電極に対応する部分にグルー層を備えた有機薄膜トランジスタ及びその製造方法を提供する。

【解決手段】基板上に形成されたゲート電極と、ゲート電極を含んだ基板上に形成されたゲート絶縁膜と、ゲート絶縁膜の上部に形成されたソース・ドレイン電極と、ソース・ドレイン電極の下部そしてソース・ドレイン電極間のゲート絶縁膜上に形成されたグルー層とを備える有機薄膜トランジスタである。

(もっと読む)

薄膜トランジスタアレイ基板及びその製造方法

【課題】 アルミを含んだ上層と下層金属層との積層から加工されるドレイン電極は反射電極を兼ねており、しかも、ドレイン電極と画素電極とのコンタクト抵抗が低い薄膜トランジスタを備えた薄膜トランジスタアレイ基板をマスク枚数を追加することなく提供する。

【解決手段】 下層の金属膜と上層のアルミ膜の積層構造をなすドレイン電極の露光時に一部領域のみ露光量を変えることによりレジスト厚が他よりも薄い領域を形成した後に、通常どおりのパターニングを行う。その後、該領域のレジストを完全に除去し、露出したアルミ膜のみ選択エッチング除去する。ドレイン電極上の層間絶縁膜に形成するコンタクトホールを該領域に設け、該コンタクトホールを介して画素電極と電気的に接続させる。

(もっと読む)

半導体デバイス製造のためのゲート材料

電子デバイスを形成する際、半導体層を予めドープして、ドーパント分布アニールをゲート画定前に行う。場合によっては、ゲートは金属から形成されている。したがって、続いて形成される浅いソースおよびドレインは、ゲートアニールステップの影響を受けない。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】 ゲート容量が小さく、短チャネル効果が抑制された薄膜トランジスタ(TFT)を作製する。またゲート配線の配線抵抗を減少させ、回路面積の減少とTFTの高速駆動を可能にする。

【解決手段】 ゲート電極を二層にし、下層の幅を上層よりも小さくすることにより、ゲート電極と半導体膜からなる活性層の重なる面積が小さくなる。これによりゲート容量を減少させ、短チャネル効果を抑制することができるので、TFTを高速駆動させることが可能である。また、ゲート電極と配線を一体形成せず別々に形成することによって、TFTによって構成される回路面積も縮小でき、高速化に寄与できる。

(もっと読む)

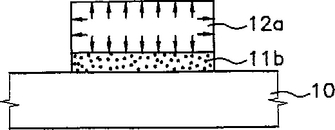

薄膜トランジスタ,電子装置およびフラットパネルディスプレイ装置

【課題】 優れた特性を有し,常温で製造可能であり,活性層とソースおよびドレイン電極間のコンタクト抵抗が改善され,多数の異種TFTの同時形成工程を簡単にする薄膜トランジスタおよびこれを備えたフラットパネルディスプレイ装置を提供する。

【解決手段】 少なくとも一つのナノ粒子12を有する少なくとも2層のナノ粒子層11a,11bを含む活性層11と,活性層11から絶縁されるゲート電極14と,活性層11のいずれか1層のナノ粒子層11aまたは11bとコンタクトされるソースおよびドレイン電極16と,を含み,ナノ粒子層11a,11b間には絶縁層11cが介在される。

(もっと読む)

半導体装置の製造方法

【課題】 安定製造が可能であり、また安価に低電圧動作、低消費電力、高速動作が可能である極薄膜SOI基板を用いたMOS型半導体装置の製造方法を提供することを目的とする。

【解決手段】 極薄膜SOI基板を用いたMOS型半導体装置において、ソースおよびドレイン上に薄い絶縁膜中に設けたコンタクトを介して多結晶シリコンを形成し、次に比較的厚い絶縁膜を設けコンタクトを形成し、金属配線とソースおよびドレインの電気的接合は多結晶シリコンを介して行うようにした。

(もっと読む)

半導体装置用基板及びその製造方法、電気光学装置用基板、電気光学装置並びに電子機器

【課題】 スタックコンタクトにおける接触抵抗を抑制させる。

【解決手段】 基板と、基板上に設けられた薄膜トランジスタと、該薄膜トランジスタの上層側に設けられた配線と、該配線と薄膜トランジスタの少なくとも半導体層とを層間絶縁する層間絶縁層と、該層間絶縁層に掘られており且つ基板面上で平面的に見て長手状に延びる第1の穴、及び、夫々、第1の穴の底部から層間絶縁層を貫通して半導体層の表面に至り且つ第1の穴の長手方向に沿って配列された複数の第2の穴を含んでおり、配線と半導体層とを層間絶縁層を介して接続するコンタクトホールとを備える。

(もっと読む)

表示デバイスおよびその製法

【課題】 アルミニウム合金膜と透明電極が直接コンタクトすることを可能とし、バリアメタルの省略を可能にするアルミニウム合金膜を用いた表示デバイスとその製造技術を提供すること。

【解決手段】 基板上に配置された薄膜トランジスタと、透明電極によって形成された透明導電膜、および、これら薄膜トランジスタと透明導電膜を電気的に接続するアルミニウム合金膜を有し、該アルミニウム合金膜と前記透明導電膜の界面には該アルミニウム合金の酸化皮膜が形成されており、該酸化皮膜の膜厚が1〜10nmで、該酸化皮膜中の酸素含有量が44原子%以下である表示デバイスとその製法を開示する。

(もっと読む)

配線層の形成方法、配線層および薄膜トランジスタ

【課題】 配線膜厚が200〜1000nm程度のサブμmオーダの薄膜でも2.5μΩcm以下の比抵抗を得ること配線層の形成方法および配線層を提供すること。

【解決手段】 ガラス基板1上に下地絶縁膜2の窒化シリコン膜を形成し、この上に下地金属層3を形成し、この上に金属シード層4を形成し、この金属シード層4上に金属配線層7を形成した配線層であって、上記金属シード層4は主として結晶面が(111)に配向し、平均結晶粒径が0.25μm以上であり、上記金属配線層は膜厚が200乃至1000nmであり、無電解めっき法で形成された層である。

(もっと読む)

導電性有機ポリマー/ナノ粒子複合材料およびその使用方法

導電性有機ポリマーと複数のナノ粒子との水性分散液を含んでなる組成物が提供される。発明組成物からキャストされるフィルムは、有機発光ダイオード(OLED)のようなエレクトロルミネセンスデバイスおよび薄膜電界効果トランジスタ用電極での緩衝層として有用である。ナノ粒子を含有する緩衝層は、ナノ粒子なしの緩衝層よりもはるかに低い導電率を有する。さらに、エレクトロルミネセンス(EL)デバイス中へ組み込まれた場合に、本発明による緩衝層はELデバイスのより高い応力寿命に寄与する。  (もっと読む)

(もっと読む)

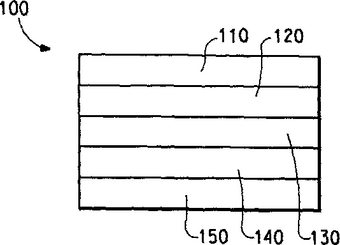

薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備えた平板表示装置及びその平板表示装置の製造方法

【課題】 薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備えた平板表示装置及びその平板表示装置の製造方法を提供する。

【解決手段】 チャンネル領域、ソース、及びドレイン領域を有する活性層と、前記チャンネル領域に信号を印加するゲート電極と、前記ソース及びドレイン領域にそれぞれ接続し、Ti、Ti合金、Ta、及びTa合金のうち少なくとも一つを含むソース及びドレイン電極と、前記ソース及びドレイン電極と前記活性層との間に介在され、シリコンナイトライドを含む絶縁膜と、を含むことを特徴とする薄膜トランジスタ。これにより、ソース/ドレイン電極の配線抵抗を低め、活性層からの汚染を防止し、画素電極との接触抵抗特性が改善され、活性層への水素供給を円滑にして移動度、オンカレント特性、スレショルド電圧特性などに優れたTFT及びそれを備えた平板表示装置が得られる。

(もっと読む)

半導体装置および電子機器

【課題】 半導体集積回路において、今後のさらなるゲート電極の微細化を進める技術を提供することを課題とする。

【解決手段】 本発明は、レジストマスクをエッチングにより後退させて導電膜のエッチングを行い、ゲート配線の断面形状は上層配線とコンタクト可能な幅を有する台形とし、且つ、ゲート配線から分岐するゲート電極の断面形状を意図的に3つの内角をもつ形状、代表的には三角形状として1μm以下のゲート幅を実現する。本発明により、オン電流の増大が実現し、高速動作する回路(代表的にはCMOS回路やNMOS回路)を得ることができる。

(もっと読む)

ニッケルゲルマノシリサイド化したゲートを組み込んだMOSFETおよびこれらのMOSFETを形成する方法

MOSFETのゲートまたはMOSFETのソースまたはドレイン領域は、シリコンゲルマニウムまたは多結晶シリコンゲルマニウムを含む。好ましくはニッケルシリサイドのモノシリサイドフェーズを含むニッケルゲルマノシリサイド(62、64)を形成すべく、ニッケルでのシリサイデーションを実行する。

ニッケルモノシリサイドによって呈される優れたシート抵抗を実質的に保持する一方、シリサイド中にゲルマニウムを含むことは、モノシリサイドフェーズが形成され得るより温度領域をより広くする。その結果、ニッケルゲルマノシリサイドは、後続のプロセスの間、ニッケルモノシリサイドよりも、より高い温度に耐えることができる。しかしながら、ニッケルモノシリサイドとほぼ同一のシート抵抗および他の有益な特性を提供する。  (もっと読む)

(もっと読む)

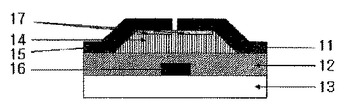

セミコンダクタ・オン・インシュレータ半導体装置及び製造方法

セミコンダクタ・オン・インシュレータ半導体装置は金属又はシリサイド・ソース・コンタクト領域及びドレイン・コンタクト領域(38、40)、活性化ソース領域及びドレイン領域(30、32)並びに本体領域(34)を有する。構造体は二重ゲートSOI構造体又は完全空乏型(FD)SOI構造体でよい。スペーサ(28)を使用し、半導体層の全厚みをコンタクト領域で完全に置き換えるプロセスを用いてシャープな海面と低抵抗とが達成される。  (もっと読む)

(もっと読む)

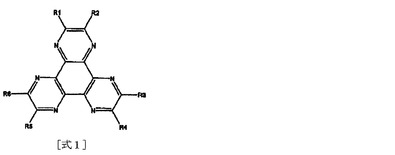

有機薄膜トランジスタ

本発明は、有機物層を有する有機トランジスタが提供される。本発明の前記有機物層は、下記式1で表される化合物のうち少なくともいずれか1種を含む。

(もっと読む)

(もっと読む)

701 - 720 / 732

[ Back to top ]