Fターム[5F110AA03]の内容

Fターム[5F110AA03]に分類される特許

601 - 620 / 732

薄膜トランジスタ、その製造方法および液晶表示装置

【課題】閾値電圧の変動を防止できる薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ8のゲート電極27を、アルミニウム層の母層31上に窒化チタン層の上層32を積層させ、母層31下に合金化していないチタン層の下層33を積層させた三層構造とした。薄膜トランジスタ8の活性層21のソース領域23およびドレイン領域24へのイオンドーピングをイオンインプランテーションとした。ソース領域23およびドレイン領域24を350℃以上450℃以下の低温度でアニールして活性化した。母層31と上層32および下層33との間の化学的な反応を抑制できる。ゲート電極27での抵抗値上昇を抑制できる。ゲート電極27を低抵抗化できる。薄膜トランジスタ8の閾値電圧の変動を抑制できる。

(もっと読む)

薄膜トランジスタ、およびその製造方法

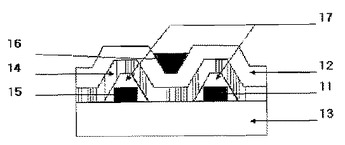

【課題】ソース電極、ドレイン電極と、ゲート絶縁層上のチャネルとの電荷移動をスムースにし、高い移動度を安定して実現した有機薄膜トランジスタの製造方法を提供する。

【解決手段】基板10の上にゲート電極11を設ける。ゲート電極11の上にゲート絶縁層12を設ける。ゲート絶縁層12の上に有機電子材料層13を設ける。有機電子材料層13の上の、ソース電極及びドレイン電極を設ける領域との間の間隙領域にスペーサー部30を設ける。ソース電極及び/またはドレイン電極を設ける領域における有機電子材料層13を、所定の深さまで除去する。ゲート絶縁層12及び/または有機電子材料層13の上のソース電極、及びドレイン電極を設ける領域に、ソース電極15及びドレイン電極14を設ける。

(もっと読む)

半導体装置の作製方法

【課題】耐熱性の低い基板にも低抵抗のTiシリサイド層を形成することを課題とする。

【解決手段】Tiシリサイド層の加熱処理工程にレーザー光を用いることで、耐熱性の低い基板上にも低抵抗のTiシリサイド層を形成することができる。シリコンを含む半導体膜に接してTi膜を成膜し、第一の加熱処理により高抵抗のTiシリサイド層を形成し、レーザー照射を用いた第二の加熱処理により、高抵抗のTiシリサイド層を低抵抗のTiシリサイド層にする。本発明によりTiシリサイド層を形成するために高温で加熱処理する必要がないため、基板を制限なく用いることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】電気的な接続の信頼性が確保される半導体装置とその製造方法を提供する。

【解決手段】ガラス基板1の表面上に1対のソース・ドレイン領域4a,4bが形成された島状シリコン層4が形成されている。島状シリコン層4上に絶縁膜5を介在させてゲート電極6が形成され、そのゲート電極6を覆うように層間絶縁膜7が形成されている。層間絶縁膜7および絶縁膜5にコンタクトホール9が形成され、そのコンタクトホール9内にプラグ10a,10bが形成されている。コンタクトホール9は、島状シリコン層4を貫通するように形成され、島状シリコン層4を貫通するコンタクトホール9aと、コンタクトホール9aよりも大きい開口断面積を有するコンタクトホールの部分9bとにより構成される。コンタクトホール9内に露出した島状シリコン層4の部分に高濃度領域4dが形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 接合リークを増大させることがなく、低抵抗なコンタクトを半導体基板の全面で安定して形成することができる半導体装置、及びその製造方法を提供する。

【解決手段】 半導体層を有する基板1上に、金属酸化物からなるライナ膜26と絶縁膜22からなる層間絶縁膜20を形成する。次に、絶縁膜22上に、コンタクトホール24の形成位置に開口部を有するマスクパターン23を形成する。そして、マスクパターン23をエッチングマスクとして絶縁膜22をエッチング除去し、ライナ膜26を露出させる。この後、露出したライナ膜26を真空中でエッチング除去し、半導体基板1を露出させ、当該真空中で連続して、露出した半導体基板1上に導電膜を形成することでコンタクト構造を形成する。

(もっと読む)

有機薄膜トランジスタ

本発明は、有機薄膜トランジスタにおいて、半導体層と電極との間のオーミックコンタクトを容易にし、かつ半導体層そのものとして作用する有機化合物を含む有機物層を有する有機薄膜トランジスタに関するものである。

本発明に係る有機薄膜トランジスタは、半導体層とソース電極/ドレーン電極との間の電気的接触に優れて、電気電子素子の構成部品として広く用いることができ、その結果、前記有機薄膜トランジスタのソース電極やドレーン電極用材料として仕事関数が比較的低くても低費用で、かつ加工性に優れた物質を用いることができる。  (もっと読む)

(もっと読む)

エッチング液、これを用いた配線形成方法及び薄膜トランジスタ基板の製造方法

【課題】モリブデン/銅/窒化モリブデン多重膜配線用エッチング液を提供すること。また、前記エッチング液を利用する配線形成方法を提供すること。さらに、前記エッチング液を利用する薄膜トランジスタ基板の製造方法を提供すること。

【解決手段】エッチング液、これを利用する配線形成方法及び薄膜トランジスタ基板の製造方法が提供される。モリブデン/銅/窒化モリブデン多重膜配線用エッチング液は過酸化水素10ないし20重量%、有機酸1ないし5重量%、トリアゾール系化合物0.1ないし1重量%、ふっ素化合物0.01ないし0.5重量%及び残量の超純水を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 MISFETを有する半導体装置の性能を向上させる。

【解決手段】 半導体基板1のp型ウエル7上にゲート絶縁膜8を介してゲート電極15が形成され、p型ウエル7にはソース・ドレインとしてのn+型半導体領域35が形成されている。ゲート電極15の両側壁上にはオフセットスペーサ23を介してサイドウォールスペーサ33が形成され、サイドウォールスペーサ33の側面34aには凹部34bが形成されている。ゲート電極15上およびn+型半導体領域35上に金属シリサイド膜43a,43bが形成され、金属シリサイド膜43aはゲート電極15の上面上だけでなく、サイドウォールスペーサ33の側面34aうちの凹部34bよりも上部の領域上にも延在している。金属シリサイド膜43bは、n+型半導体領域35の上に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板に形成され、素子間分離として部分トレンチ分離を有する半導体装置において、トランジスタのソースドレインの低抵抗化およびリーク電流の低減を図る。

【解決手段】埋込酸化膜層(BOX層)2上に形成されたSOI層3には、分離絶縁膜5で規定された活性領域にMOSトランジスタ10が形成されている。分離絶縁膜5は、BOX層2に達していない部分トレンチ分離であり、ソースドレイン領域17は、互いに質量数が異なる第1および第2不純物イオンにより形成されている。

(もっと読む)

機能性分子素子及びその製造方法、並びに機能性分子装置

【課題】 構成分子と電極との界面での接触抵抗を低減できる新規な構造をもつ機能性分子素子及びその製造方法、並びに機能性分子装置を提供すること。

【解決手段】 まず、リニアテトラピロールの1種で、ポルフィリン様の略円盤状構造を有する骨格部2と、アルキル鎖からなるフレキシブルな側鎖部3とをもつπ電子共役系分子1を用いて、電極5および6の表面に密着した分子層を単層で形成する。次に、このπ電子共役系分子1の上にπ-πスタッキングによって、π電子共役系分子1又は他のπ電子共役系分子を積層させ、配列構造体4を形成する。配列構造体4の第1層の分子層を形成するπ電子共役系分子1は、フレキシブルな側鎖部3が電極5(または6)の表面に吸着され、この結果、骨格部2の円盤面が電極5(または6)の表面に平行に密着するように固定される。また、配列構造体4の第2層以後の分子層の積層方向は、π-π相互作用によって制御される。

(もっと読む)

半導体ナノワイヤトランジスタ

ナノワイヤのラップゲートトランジスタはSiより狭いバンドギャップを持つ半導体材料において実現される。ナノワイヤの歪み緩和は、トランジスタが多くの種類の基板と素子中に組み込まれるヘテロ構造との上に配置されることを可能にする。各種ヘテロ構造は、低減された衝突イオン化速度により出力コンダクタンスを低減し、電流オンオフ比を増加し、サブしきい値の傾斜を減少し、トランジスタの接触抵抗を減少し、および熱安定性を改善するためにトランジスタ中に導入される。寄生容量は半絶縁基板の使用とソースおよびドレインアクセス領域の間の横木構造の使用によって最小にされ得る。本トランジスタはデジタル高周波、低電力回路およびアナログ高周波回路に応用されるだろう。  (もっと読む)

(もっと読む)

エッチング液、エッチング液及びその結果構造物を用いた導電性配線を含む薄膜トランジスタ基板の製造方法

【課題】銀(Ag)配線用エッチング液を提供すること。また、エッチング液を利用する銀(Ag)配線形成方法を提供すること。さらに、エッチング液を利用する薄膜トランジスタ基板の製造方法を提供すること。

【解決手段】本発明により、エッチング液、これを用いた配線形成方法及び薄膜トランジスタ基板の製造方法が提供される。エッチング液は下記化学式1で表示される物質、酢酸アンモニウム及び超純水を含む。

(化学式1)

M(OH)XLY

(ただし、前記式でMはZn、Sn、Cr、Al、Ba、Fe、Ti、SiまたはBであり、Xは2または3であり、LはH2O、NH3、CN、COR、NH2Rであり、Yは0、1、2または3であり、Rはアルキル基である。)

(もっと読む)

液晶表示装置の製造方法

【課題】少なくとも有機絶縁膜を有する層間絶縁膜上に透明導電膜をパターン形成する液晶表示装置の製造方法において、ITOドライエッチング時の均一性を確保する。

【解決手段】パッシベーション膜32にコンタクトホール26,27を開口する工程は、層間絶縁膜上にフォトレジストをパターン形成する工程と、フォトレジストをポストベークする工程を経ることなく、フォトレジストをマスクとしてパッシベーション膜32にドライエッチングを施す工程と、を備える。

(もっと読む)

半導体装置およびその作製方法

【課題】薄膜トランジスタにおいて、ソース/ドレイン領域へのコンタクトの方法を改良することにより、配線抵抗を減らす。

【解決手段】ガラス基板上に第1の絶縁膜、島状の結晶性珪素膜、ゲイト絶縁層、ゲイト電極、第1の配線、ゲイト電極及び第2の絶縁膜を形成し、第2の絶縁膜及びゲイト絶縁層をエッチングしてゲイト電極及び第1の配線の側面に側壁を形成するとともに、島状の結晶性珪素膜のソース領域及びドレイン領域を露出し、ゲイト電極、第1の配線、側壁、島状の結晶性珪素膜及び第1の絶縁膜上に金属層を形成し、ソース領域及びドレイン領域と、金属層とを反応させて島状の結晶性珪素膜の側面から上面にわたって密着したシリサイド層を形成し、金属層をエッチングして、ソース領域又はドレイン領域の一方のシリサイド層と第1の配線とを接合する第2の配線を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 接合リークを抑制しつつ、ソース/ドレイン層の低抵抗化を図るとともに、ショートチャネル効果を抑制する。

【解決手段】 ゲート電極15の一方の側に絶縁層12に底面が接する合金層からなるソース層18aを配置し、単結晶半導体層13の結晶方位面20aに沿ってチャネル領域17に対する接合面を形成し、ゲート電極15の他方の側に絶縁層12に底面が接する合金層からなるドレイン層18bを配置し、単結晶半導体層13の結晶方位面20bに沿ってチャネル領域17に対する接合面を形成し、ソース層18aを構成する合金層と単結晶半導体層13との界面には、結晶方位面20aに沿うようにして自己整合的に形成された不純物導入層19aを設け、ドレイン層18bを構成する合金層と単結晶半導体層13との界面には、結晶方位面20bに沿うようにして自己整合的に形成された不純物導入層19bを設ける。

(もっと読む)

表示装置用配線、これを含む薄膜トランジスタ表示板、及びその製造方法

【課題】銀(Ag)配線の低抵抗性の利点を生かしながらも接着性及びエッチングプロファイルを補完する薄膜トランジスタの製造方法を提供する。

【解決手段】基板110上に第1信号線を形成する段階と、第1信号線上にゲート絶縁膜140及び半導体層を順次に形成する段階と、ゲート絶縁膜140及び半導体層上に第2信号線171を形成する段階と、第2信号線171と連結される画素電極191を形成する段階と、を含み、第1信号線を形成する段階及び第2信号線171を形成する段階のうちの少なくとも一つの段階は、第1導電性酸化膜を形成する段階と、銀(Ag)を含む導電層を形成する段階と、第1導電性酸化膜よりも低い温度で第2導電性酸化膜を形成する段階と、を含む。

(もっと読む)

薄膜トランジスタ基板及びその製造方法

【課題】本発明は、液晶表示装置に用いられる薄膜トランジスタ基板及びその製造方法に関し、ゲート電極や所定の配線の材料に低抵抗金属を用いても、高い信頼性を確保しうる薄膜トランジスタ基板及びその製造方法を提供することを目的とする。

【解決手段】TFT基板は、窒素含有層としてのAlN膜51と、主配線層としてのAl膜50と、MoN膜54とMo膜53とからなる上層配線層とにより構成された積層構造のゲート電極33を有している。ゲート電極33の側面は全体としてなだらかに傾斜するように形成されているので、ゲート絶縁膜32上に良好な膜質のゲート絶縁膜32を形成することができる。

(もっと読む)

ナノワイヤ・チャネルおよびシリサイド化下部コンタクトを有する垂直型FET

【課題】 下部コンタクトに対するアクセス抵抗を低減させ、ゲート長が制御された、ナノワイヤ・チャネルを含む垂直型FETを提供する。

【解決手段】 FETチャネルを形成するナノワイヤを有する垂直型FET構造を開示する。ナノワイヤを、導電性シリサイド層の上に形成する。ナノワイヤは、周囲のゲートによって制御される。上部および下部の絶縁プラグがゲート・スペーサとして機能し、ゲート−ソースおよびゲート−ドレイン静電容量を低減させる。

(もっと読む)

多層相補型配線構造及びその製造方法

【課題】 配線の抵抗を大幅に低減することができる多層相補型配線構造及びその製造方法を提供する。

【解決手段】 多層配線構造は、基板と、第1の方向に互いに平行に延び基板上の第1の層に形成される複数の第1の導電性ラインと、第1の方向に直交する第2の方向に互いに平行に延び第1の層上の第2の層に形成される複数の第2の導電性ラインと、第1の方向に延び第2の層に形成され、その各セットが第1の導電性ラインの1つに対応する複数の第3の導電性ラインのセットと、第1の層と第2の層との間に形成され、その各セットが第1の導電性ラインの1つと第3の導電性ラインの1つのセットに対応し、対応する第1の導電性ラインを対応する第3の導電性ラインのセットに電気的に接続する複数の導電性パスのセットを備える。

(もっと読む)

多層薄膜、並びに該多層薄膜を有する薄膜トランジスタ及び薄膜トランジスタ表示板の製造方法

【課題】薄膜トランジスタの特性及び表示装置の性能を向上させる。

【解決手段】基板41上に多結晶シリコン膜42が形成され、その上に多結晶シリコン膜の表面を露出させるコンタクトホール44を有する絶縁膜43が形成されている。該絶縁膜上には、非晶質シリコン膜45及び導電膜46を有するゲート線が形成され、コンタクトホールを介して多結晶シリコン膜42と接続している。また、ゲート線上に絶縁膜とデータ線が形成されている。このように、非晶質シリコン膜45を設けて側面傾斜を多様にし、基板を熱処理して導電膜46と非晶質シリコン膜45の間の接着力を向上させることで、接触抵抗を低減することができ、薄膜トランジスタの特性及び信頼性が向上される。

(もっと読む)

601 - 620 / 732

[ Back to top ]