Fターム[5F110AA03]の内容

Fターム[5F110AA03]に分類される特許

581 - 600 / 732

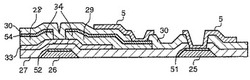

ソース−ドレイン電極、トランジスタ基板およびその製造方法、並びに表示デバイス

【課題】下部バリアメタル層の省略を可能にすると共に、工程数を増やすことなく簡略化し、Al系合金膜を薄膜トランジスタの半導体層に対し直接かつ確実に接続することができ、しかも、Al合金膜に対して低い熱プロセス温度を適用した場合でも、透明画素電極間の低電気抵抗率化を達成し得るソース−ドレイン電極を提供する。

【解決手段】薄膜トランジスタの半導体層33と、ソース−ドレイン電極34と、透明画素電極5とを有する薄膜トランジスタ基板において、ソース−ドレイン電極34は、合金成分としてNiを0.1〜6原子%含有するAl合金の薄膜からなり、Al合金の薄膜は薄膜トランジスタの半導体層33と直接接続している。

(もっと読む)

半導体素子

【課題】 電極層と半導体層との接触抵抗が低く、密着性と経時安定性に優れた酸化物半導体素子を提供する。

【解決手段】 酸化物半導体層と貴金属電極との間に、それらの間の密着性を向上させるための密着性向上層106が分散して配置され、前記酸化物半導体層と貴金属電極が接触する部分を有する。密着性向上層106は、島状又はストライプ状に分散している。密着性向上層106は、10nm以下の厚さを有し、Ti、Ni、Cr、V、Hf、Zr、Nb、Ta、Mo又はWの少なくとも1つを含む。貴金属電極103の材料は、Au、Pt又はPdの少なくとも1つを含む。

(もっと読む)

薄膜トランジスタ

【課題】 薄膜トランジスタの構成半導体(活性層)である酸化亜鉛を主成分とする酸化物半導体薄膜の表面層を保護する構造を有し、ドレイン・ソース間の低抵抗化などによる特性劣化を防止し得る高性能の薄膜トランジスタの提供。

【解決手段】 絶縁基板上にソース・ドレイン電極が間隔を有して形成され、前記ソース・ドレイン電極の間にチャネルとして形成される酸化亜鉛ZnOを主成分とする酸化物半導体薄膜層と、該酸化物半導体薄膜層の上表面及び側面を被覆してシリコン系絶縁膜にて形成されるゲート絶縁膜を有し、前記ゲート絶縁膜は、前記酸化物半導体薄膜層の上表面を被覆する第一ゲート絶縁膜と、前記第一ゲート絶縁膜の全面及び酸化物半導体薄膜の少なくとも側面を被覆する第二ゲート絶縁膜からなることを特徴とする薄膜トランジスタ。

(もっと読む)

多層ゲート電極及びその製造方法、ならびに多層ゲート電極が形成された半導体素子及びその製造方法

【課題】高温で安定であり、抵抗等の特性が改善され、信頼性が高い多層ゲート電極及びこれを備える半導体素子、ならびに多層ゲート電極の製造方法及び半導体素子の製造方法を提供する。

【解決手段】多層ゲート電極は、ゲート絶縁膜上に形成され導電型不純物がドープされた多結晶半導体膜と、前記多結晶半導体膜上に形成されタングステン(W1−x)及び非タングステン金属(Mx、x=0.01〜0.55)を含むオーミックコンタクト膜と、前記オーミックコンタクト膜の上に形成された金属バリヤ膜と、前記金属バリヤ膜の上に形成された高融点金属膜と、を備える。

(もっと読む)

半導体構造

【課題】 金属ゲート電極層に望まれる特性は、微細加工を施された半導体立体構造体上に段差被覆率良く被覆されていることである。またもう一つの特性は、堆積された電極層の表面が1ナノメートルのスケールで平坦であり、電極層の堆積後に特別な平坦化処理を施すことなく電気的な絶縁を目的とした誘電体層を被服することが可能なことである。また、金属ゲート電極層に望まれる更なる特性の一つは、通常の半導体プロセスと同様のエッチング加工性を有していることである。また、金属ゲート電極層に望まれるもうひとつの特性は、結晶粒界がなく均一であり、不純物拡散が抑制された構造であることである。

【解決手段】 上記特性を満たす最良の金属ゲート電極としてアモルファス構造の金属電極が優れていることを見出し、本発明に至った。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース/ドレイン領域とニッケルシリサイド膜との間の界面の平坦性を改善すること。

【解決手段】ソース/ドレイン領域5sd上にErを含むNi膜を形成し、その後、ソース/ドレイン領域5sdと、Erを含むNi膜とを加熱することにより、ニッケルシリサイド膜9を形成する。

(もっと読む)

半導体素子のゲートパターン及びその形成方法

【課題】ゲートパターン間に埋め込まれる層間絶縁膜の埋め込み性及びランディングプラグ形成物質の埋め込み性を向上させることができる半導体素子のゲートパターン及びその形成方法を提供すること。

【解決手段】半導体素子のゲートパターンは、基板110に形成されたトレンチ112の内面及び基板110の表面に形成されたゲート絶縁膜114と、トレンチ112が形成されていない領域におけるゲート絶縁膜114の上面より突出しないように、トレンチ112に埋め込まれた第1ゲート電極層116Aと、一部分が第1ゲート電極層116Aと接触するように、第1ゲート電極層116A上に形成された第2ゲート電極層120Aとを備えている。

(もっと読む)

半導体装置の製造方法、薄膜トランジスタ及び表示装置

【課題】ソース領域及びドレイン領域における不純物の活性化及びコンタクト抵抗の低減を効率良く行うことができる、生産性に優れた半導体装置の製造方法を提供すること。

【解決手段】基板上に半導体膜を形成する工程、前記半導体膜を含む前記基板上にゲート絶縁膜を形成する工程、前記ゲート絶縁膜上にゲート電極を形成する工程、前記ゲート電極をマスクとして前記ゲート絶縁膜をエッチングし、前記半導体膜を露出する工程、全面に金属層を形成する工程、前記ゲート電極をマスクとして前記半導体膜に不純物を注入する工程、及び前記不純物注入領域に熱処理を施し、前記半導体膜中の不純物を活性化するとともに、前記半導体膜と金属層との界面に金属シリサイド層を形成する工程を具備することを特徴とする。

(もっと読む)

配線構造と配線形成方法及び薄膜トランジスター基板とその製造方法

【課題】薄膜トランジスター基板の配線形成に関する。Alなどの抵抗の高い材料に替えてAgなどの配線抵抗の低い材料を用いる。しかし、Agは蒸着が難しく、又蒸着されても後続のパターニング工程から配線の浮き上がり、又は剥離が誘発されやすい欠点を持っている。この欠点を解決して接着力が改善された低抵抗Agの配線構造を提供する。

【解決手段】下部構造物上に形成された銀(Ag)酸化物を含む下部膜と、下部膜上に形成された銀(Ag)または銀(Ag)合金を含む銀(Ag)導電膜を含む配線構造とした。これにより配線不良による配線の信頼性の低下が防止できる。

(もっと読む)

配線及びその形成方法と薄膜トランジスタ基板及びその製造方法

【課題】接着性が向上し、伝導性に優れた配線及びその形成方法とこれを用いて形成された薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】 配線は、酸化反応性金属またはシリサイド化反応性金属、及び銀を含む接着層と、前記接着層上に形成される銀導電層と、前記銀導電層上に形成され、前記酸化反応性金属及び前記銀を含んで形成される保護層とを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界効果型トランジスタが形成される半導体層の結晶性の劣化を抑制しつつ、電界効果型トランジスタが形成される半導体層下に低抵抗化されたバックゲート電極を配置する。

【解決手段】単結晶半導体基板11上には埋め込み酸化膜12が形成され、埋め込み酸化膜12上には、バックゲート電極を構成する第1単結晶半導体層13が形成されている。さらに、第1単結晶半導体層13上には埋め込み酸化膜14が形成され、埋め込み酸化膜14上には、メサ分離された第2単結晶半導体層15a、15bが積層され、第2単結晶半導体層15a、15bの膜厚は第1単結晶半導体層13の膜厚よりも厚くするとともに、第2単結晶半導体層15a、15bにSOIトランジスタを形成する。

(もっと読む)

表示装置及び表示用薄膜半導体装置

【課題】薄膜トランジスタの活性層となる半導体薄膜のレーザアニールによる再結晶化処理を均一化及び最適化するとともに、ゲート配線の低抵抗化を図る。

【解決手段】表示装置は、各薄膜トランジスタ4のゲート電極1を互いに接続するゲート配線6と、各薄膜トランジスタ4のソース電極Sを互いに接続する信号配線7とが絶縁基板上で互いに交差する様に形成されている。ゲート配線6は、個々のゲート電極1と一体的に形成された一体部6aと、これらを互いに接続する別体部6bとに分かれている。ゲート電極1はゲート配線6の別体部6bより低い熱伝導性を有し、ゲート配線6の別体部6bはゲート電極1より低い電気抵抗を有する。信号配線7とゲート配線6の一体部6aとが絶縁膜14をはさんで交差する。

(もっと読む)

表示装置

【課題】表示装置における表示領域よりも配線幅の狭い周辺駆動回路領域において、互いに異なる配線層間を接続するコンタクトプラグの接触不良による歩留りや信頼性の低下を防止する。

【解決手段】表示領域2よりも配線幅が狭い周辺駆動回路領域3における第2の層間絶縁膜10の膜厚を、表示領域2における第1の層間絶縁膜9の膜厚よりも薄くしたことで、周辺駆動回路領域3におけるコンタクトホールのアスペクト比を、表示領域2におけるアスペクト比に近づけることができ、スパッタリング法によりコンタクトホール内部に形成されたソース電極13及びドレイン電極14が、多結晶シリコン膜6と接続しやすくなる。

(もっと読む)

薄膜トランジスタ基板の製造方法

【課題】パーティクルを効率的に除去して、金属薄膜の品質を向上させる薄膜トランジスタ基板の製造方法を提供する。

【解決手段】絶縁基板上にゲート金属層を形成する段階と、前記ゲート金属層上に感光膜パターンを形成する段階と、前記感光膜パターンを利用して、前記ゲート金属層をエッチングしてゲート配線を形成する段階と、前記感光膜パターンをストリップして、前記ゲート配線を露出させる段階と、前記露出したゲート配線を硝酸を含む洗浄液で洗浄する段階とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル層に応力が付加され、かつ高信頼なMOSFETを実現する。

【解決手段】半導体基板と、前記半導体基板の表面に対向して設けられ、単結晶または多結晶構造を有する一対のソース・ドレイン電極と、前記ソース・ドレイン電極の間の前記半導体基板の表面に形成された単結晶チャネル領域と、前記チャネル領域上にゲート絶縁膜を介して形成されたゲート電極と、前記ソース・ドレイン電極の上部に形成された金属化合物層と、前記ソース・ドレイン電極の下部に位置し、前記ソース・ドレイン電極を構成する物質の固有の格子間隔とは異なる格子間隔を保持した結晶構造を有する応力付与層と、前記応力付与層の下部に位置する第1の絶縁層とを具備する。

(もっと読む)

コンタクトホール形成方法及びこれ用いた薄膜トランジスタ基板の製造方法

【課題】エッチング比制御が可能なコンタクトホール形成方法を提供すること。また、コンタクトホール下部に位置した金属配線の酸化を防止するコンタクトホール形成方法を提供すること。さらに、そのようなコンタクトホール形成方法を用いた薄膜トランジスタ基板の製造方法を提供すること。

【解決手段】本発明によると、乾式エッチング方法によってコンタクトホールを形成する方法及びこれを用いた薄膜トランジスタ基板の製造方法が提供される。コンタクトホール形成方法は、銀を含む金属配線が形成されている基板を準備し、基板全面に低温工程で絶縁膜を形成し、フッ素系ガス及び窒素ガスを含む無酸素ガスを用いた乾式エッチングによって絶縁膜の所定位置をエッチングして金属配線を露出することを含む。

(もっと読む)

平板表示装置と平板表示装置の製造方法

【課題】データ配線と透明電極層間の接触構造を改善した平板表示装置を提供する。

【解決手段】平板表示装置は、絶縁基板と、絶縁基板上に形成されているデータ配線と、データ配線上にデータ配線を露出させる第1接触口を有する層間絶縁膜と、第1接触口の少なくとも一部とその周辺の層間絶縁膜上に形成されている連結部材と、連結部材上に形成されて連結部材を露出させる第2接触口を有するゲート絶縁膜及びゲート絶縁膜上に形成されている有機半導体層を含む。

(もっと読む)

デュアルゲートCMOS構造体を製造する方法、キャパシタ、及び、デュアルゲート・キャパシタ

【課題】 極薄SOIベースのデュアルゲートCMOSキャパシタ及び製造方法を提供すること。

【解決手段】 デュアルゲートCMOS構造体のための製造方法及びデバイスである。この構造体は、絶縁層(100)内の第1プレート(106a−106d)と、第1プレートに電気的に対応する絶縁層の上方の第2プレート(110a−110d)とを含む。分離構造体(108a−108d)が、第1プレートと第2プレートとの間にある。

(もっと読む)

表示デバイス

【課題】 透明電極膜(画素電極)との接続にAl合金よりも電気抵抗の低いCu合金膜を使用し、且つ、バリアメタルを形成せずとも透明電極との間で低抵抗の直接接続を実現し、液晶パネルなどに適用した場合に高い表示品質を与える表示デバイスを提供すること。

【解決手段】 Cu合金膜からなる配線・電極部と透明導電膜が、高融点金属薄膜を介することなく直接接続している表示デバイスであって、前記Cu合金膜中に、Znおよび/またはMgを総量で0.1〜3.0原子%含有させ、あるいはNiおよび/またはMnを総量で0.1〜0.5原子%含有させ、バリアメタルなしで透明電極との間で低抵抗の直接接続を可能にした。

(もっと読む)

有機半導体装置

【課題】 多数の分子材料に一般的に適用が可能な、有機半導体薄膜層との間でキャリヤを効率よく出し入れするための電気的接点となる電極及び電流を流すための電流経路となる導電性の高い層を提供することを課題とする。

【解決手段】 薄膜トランジスタの能動領域を構成し、弱い電子供与性分子からなる第1の有機半導体層と、第1の有機半導体層に重ねて形成された強い電子授容性分子からなる、一対の第2の有機半導体層を備え、第1及び第2の有機半導体層の界面を上記薄膜トランジスタのソース、ドレイン領域及びその引き出し電極としたことを特徴とする有機半導体装置によって解決される。

(もっと読む)

581 - 600 / 732

[ Back to top ]