Fターム[5F110AA03]の内容

Fターム[5F110AA03]に分類される特許

681 - 700 / 732

表示装置の作製方法

【課題】本発明は、しきい値のずれが生じにくく、高速動作が可能な逆スタガ型TFTを有する表示装置の作製方法を提供する。また、スイッチング特性が高く、コントラストがすぐれた表示が可能な表示装置の作製方法を提供する。更には、少ない原料でコスト削減が可能であり、且つ歩留まりが高い表示装置の作製方法を提供する。

【解決手段】 本発明は、耐熱性の高い材料でゲート電極を形成した後、非晶質半導体膜の結晶化を促進する触媒元素を有する層、非晶質半導体膜、及びドナー型元素又は希ガス元素を有する層を形成し加熱して、非晶質半導体膜を結晶化すると共に触媒元素を結晶性半導体膜から除いた後、該結晶性半導体膜の一部を用いて半導体領域を形成し、該半導体領域に電気的に接するソース電極及びドレイン電極を形成し、ゲート電極に接続するゲート配線を形成して、逆スタガ型TFTを形成する。

(もっと読む)

歪み完全空乏型シリコン・オン・インシュレータ半導体デバイスおよびこの製造方法

絶縁体(104)上に半導体層(106)を備える、その上に絶縁体(104)を有する半導体基板(102)を提供する。半導体層(106)に歪みを引き起こす深いトレンチ分離(108)を形成する。半導体層(106)上にゲート絶縁体(202)およびゲート(204)を形成する。ゲート(204)の周りにスペーサ(304)を形成し、スペーサ(304)の外側の半導体層(106)および絶縁体(104)を除去する。スペーサ(304)の外側にくぼんだソース/ドレイン(402)を形成する。  (もっと読む)

(もっと読む)

半導体装置、その製造方法、および情報処理装置

【課題】ソース・ドレイン領域の占有面積が小さい半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1910は、素子分離領域101と活性領域102とを有する半導体基板100と、活性領域102上にゲート絶縁膜103を介して設けられ、側壁の少なくとも一部がゲート電極側壁絶縁膜105で覆われたゲート電極104と、ゲート電極104の両側にゲート電極側壁絶縁膜105を介してそれぞれ設けられたソース領域106およびドレイン領域106とを備えている。ソース領域106およびドレイン領域106の少なくとも一方は、コンタクト配線と接触するための第2の面を有し、第2の面は、第1の面AA’に対して傾いており、第2の面は、素子分離領域の表面と80度以下の角度で交差する。

(もっと読む)

半導体装置

【課題】 本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】 本発明は、上層と、上層よりも広い幅を有する下層とからなる2層構造とする。TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。上層の端面から突出させた下層部分と、ITOとを接合させる。

(もっと読む)

半導体装置およびその製造方法

【課題】 寄生抵抗が低く、良好な性質を有する半導体装置およびその製造方法を提供する。

【解決手段】 本発明にかかる半導体装置100の製造方法は、(a)絶縁層8上に設けられた半導体層10の上方にゲート絶縁層20を形成する工程と、(b)前記ゲート絶縁層20の上方にゲート電極22を形成する工程と、(c)前記半導体層10に不純物を導入することにより、ソース領域26およびドレイン領域14を形成する工程と、(d)前記半導体層10にフッ素を導入することにより第1のフッ素含有領域50、52を形成する工程と、(e)前記半導体層10の半導体と遷移金属を反応させることにより、低抵抗半導体金属合金層32、34を形成する工程と、を含む。

(もっと読む)

薄層トランジスタ、それを用いたアクティブマトリックス型表示装置、及び、液晶表示装置

【課題】 基板との密着性と導電性に優れ、簡易に形成された電極を有する、電極の高解像化が実現された薄層トランジスタ、及び、該薄層トランジスタを備えてなる電気的特性に優れたアクティブマトリックス型表示装置及び駆動用LSIチップのドライバ入出力配線の導電性が改良され、高解像度で配線が形成されてなる液晶表示装置を提供する。

【解決手段】 光開裂によりラジカル重合を開始しうる重合開始部位と基材結合部位とを有する化合物を表面に結合させてなる基板上に、ラジカル重合可能な不飽和化合物を接触させてパターン状にエネルギーを付与し、該基板上にパターン状のグラフトポリマーを生成した後、該グラフトポリマー生成領域に導電性材料を付与してなる導電層をゲート電極110とし、該ゲート電極110上に、ゲート絶縁膜114、半導体膜118、ソース電極120、ドレイン電極122を順次備えてなる薄層トランジスタ。

(もっと読む)

液晶表示装置及びその作製方法、並びに液晶テレビジョン装置

【課題】 本発明は、材料の利用効率を向上させ、少ないフォトマスク数で、しきい値のずれが生じにくく、高速動作が可能なTFTを有する液晶表示装置の作製方法を提供する。

【解決手段】 本発明は、非晶質半導体膜に触媒元素を添加し加熱して、結晶性半導体膜を形成するとともに該結晶性半導体膜から触媒元素を除き、その後逆スタガ型薄膜トランジスタを作製する。また本発明は、薄膜トランジスタのゲート電極層と画素電極層を同工程同材料を用いて形成し、工程の簡略化と、材料のロスの軽減を達成する。

(もっと読む)

表示デバイスおよびその製法、ならびにスパッタリングターゲット

【課題】アルミニウム合金膜と透明電極が直接コンタクトすることを可能とし、バリアメタルの省略を可能にするアルミニウム合金膜を用いた表示デバイスとその製造技術を提供すること。

【解決手段】ガラス基板上に配置された薄膜トランジスタと、透明電極によって形成された画素電極と、これら薄膜トランジスタと画素電極を電気的に接続するアルミニウム合金膜によって形成された接続配線部を主たる構成要素として備えた表示デバイスとその製法を開示する。

(もっと読む)

横型MOSトランジスタ

【課題】 配線抵抗及び配線容量を低減するとともに、チップ面積を削減する。

【解決手段】 SOI基板30は、シリコン基板31の上にシリコン酸化膜32が形成され、このシリコン酸化膜32の上にN−型シリコン層33が形成されて構成される。ドレイン領域35は、シリコン層33の表面からシリコン酸化膜32まで到達して形成される。ドレイン電極42は、SOI基板30の裏面に電気的接触して形成される。導電体プラグ41は、ドレイン領域35の表面からドレイン領域35およびシリコン酸化膜32を貫通してシリコン基板31中に延在して、ドレイン領域35およびシリコン基板31に電気的接触して形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】 界面抵抗Rcが小さいSchottky−S/D構造を含むMOSトランジスタを提供すること。

【解決手段】 チャネル型が第1導電型であるMOSトランジスタは、第1および第2のチャネル領域CHを含む第1導電型半導体領域1と、第1および第2のチャネル領域CH上に設けられたゲート絶縁膜2と、ゲート絶縁膜2上に設けられたゲート電極3と、第1および第2のチャネル領域CHを挟むように設けられ、かつ、第1導電型半導体領域1とショットキー接合する、互いに離間した第1および第2のソース/ドレイン領域4を備えている。

(もっと読む)

半導体装置

【課題】配線の電気抵抗を低減した半導体装置を提供する。

【解決手段】絶縁表面を有する基板上に形成された薄膜トランジスタと、基板上に形成された第1の配線と、薄膜トランジスタの多結晶珪素膜からなる活性層と、ゲイト絶縁膜と、ゲイト電極、及び第1の配線上に形成された第1の絶縁膜と、第1の絶縁膜上に形成され、第1の絶縁膜に設けられた複数のコンタクトホールを介して第1の配線と電気的に接続している第2の配線と、薄膜トランジスタ及び第2の配線上に形成された第2の絶縁膜と、第2の絶縁膜上に形成され、第2の絶縁膜に設けられたコンタクトホールを介して薄膜トランジスタに電気的に接続された画素電極と、基板と対向して配置された対向基板とを有する。

(もっと読む)

液晶表示装置の製造方法

【課題】液晶表示装置の低抵抗配線を作製するにあたって、ヒロック、エッチング残渣、ITO等との電気化学反応の発生を防止し、かつスパッタ時のダスト発生を抑制する。

【解決手段】Al合金配線を有する液晶表示装置を製造するにあたって、Y、Sc、La、Ce、Nd、Sm、Gd、Tb、Dy、Er、Th、Sr、Ti、Zr、V、Nb、Ta、Cr、Mo、W、Mn、Tc、Re、Fe、Co、Ni、Pd、Ir、Pt、Cu、Ag、Au、Cd、Si、PbおよびBから選ばれる第1の元素を0.001〜30原子%の範囲で含み、残部が実質的にAlからなるインゴットまたは焼結体を、大気溶解法、真空溶解法、急冷凝固法、粉末冶金法で作製するにあたって、O、NおよびHから選ばれる第2の元素を含むガスを使用し、得られたインゴットまたは焼結体を加工してスパッタターゲットを作製する。このスパッタターゲットをスパッタして形成したAl合金膜にエッチング処理を施してAl合金配線を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 微粒子とこの微粒子に結合した有機半導体分子とによって導電路が形成され、その導電性が電界によって制御されるように構成された半導体装置及びその製造方法であって、デバイス構造を工夫することによって性能が向上した半導体装置及びその製造方法を提供することにある。

【解決手段】 金などの微粒子10と、この微粒子に結合した有機半導体分子13との結合体を電極2の上に層状に形成し、電極2の反対側の結合体層の面上に電極6を設け、電極2と電極6との間の結合体層の膜厚方向に形成された導電路の導電性を、ゲート電極4を通じて制御する縦型電界効果トランジスタを形成する。上記結合体層では微粒子10と有機半導体分子13とが交互に結合したネットワーク型の導電路が形成される。この導電路では、有機半導体分子内の導電路が微粒子内の導電路によって連結され、有機半導体分子内の移動度を最大限に利用することができる。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】 ソース・ドレインの界面形状とショットキー障壁高さ、電極比抵抗を同時に制御可能なショットキートランジスタを提供する。

【解決手段】 チャネル領域を構成する半導体領域112と、半導体領域112上にゲート絶縁膜113を介して形成されたゲート電極114と、ゲート電極114に対応して半導体領域112の両側に形成されたソース・ドレイン電極とを備えたMIS型電界効果トランジスタにおいて、ソース・ドレイン電極は、半導体領域112を挟んで形成され、且つキャリアがトンネル可能な厚さに形成されたトンネル絶縁膜116と、トンネル絶縁膜に接して形成された第1の金属層117と、第1の金属層117に接して形成され、第1の金属層117よりも小さい比抵抗を持つ第2の金属層118と、をチャネル長方向に積層してなる。

(もっと読む)

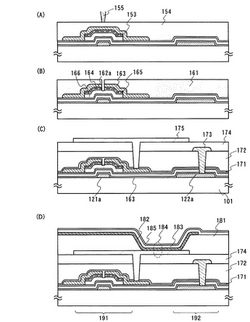

液晶表示装置の製造方法およびTFT基板

【課題】液晶表示装置製造の費用減少、生産性向上。

【解決手段】TFT部及びゲート−パッド連結部に第1及び第2金属膜を蒸着しそれら金属膜をパターニングしゲート電極及びゲートパッドを形成する段階、全面に絶縁膜を形成する段階、第1及び第2非晶質シリコン膜パターンをTFT部の絶縁膜上に形成する段階であって第2非晶質シリコン膜全体の下部表面が第1非晶質シリコン膜表面と当接するようそれらのパターンを形成する段階、ソース及びドレイン電極をTFT部上に形成しソース及びドレイン電極間の第2非晶質シリコン膜を除去する段階、ドレイン電極及びゲートパッドの一部が露出されるよう保護膜を形成しゲートパッドの一部上の絶縁膜を除去する段階、第1及び第2画素電極パターンを形成する段階を含み、第1金属膜はCr、Mo、Ta及びTiのうち1つの金属膜であり、第2金属膜はAl又はAl合金である。

(もっと読む)

半導体装置及びその作製方法、並びにテレビジョン

【課題】本発明は、しきい値のずれが生じにくく、高速動作が可能な逆スタガ型のTFTを有する半導体装置の作製方法を提供する。また、少ない原料でコスト削減が可能であり、且つ歩留まりが高い半導体装置の作製方法を提供する。

【解決手段】 本発明は、耐熱性の高い材料でゲート電極を形成した後、非晶質半導体膜を成膜し、該非晶質半導体膜に触媒元素を添加し加熱して結晶性半導体膜を形成し、該結晶性半導体膜上にドナー型元素又は希ガス元素を有する層を形成し加熱して触媒元素を結晶性半導体膜から除いた後、該結晶性半導体膜の一部を用いて半導体領域を形成し、該半導体領域に電気的に接するソース電極及びドレイン電極を形成し、ゲート電極に接続するゲート配線を形成して、逆スタガ型のTFTを形成して半導体装置を作製する。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】 抵抗が低く、画素電極または半導体層との接触性が優れた配線を有する薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】 本発明は、液晶表示装置または有機発光表示装置用薄膜トランジスタ表示板の配線に関し、モリブデン(Mo)にニオビウム(Nb)、バナジウム(V)またはチタニウム(Ti)を所定量含むモリブデン合金層とアルミニウム層の積層構造を形成することによって、既存の純粋モリブデン(Mo)を使用した場合に比べて、モリブデン合金層とアルミニウム層の相対的なエッチング速度の差が減少し、エッチング工程時におけるアンダーカット、オーバーハング及びマウスバイトなどが発生しない。更に、半導体層または画素電極との接触特性も改善されたことを特徴とする低抵抗性及び耐薬品性を同時に有する薄膜トランジスタ表示板及びその製造方法である。

(もっと読む)

フラットパネルディスプレイ用Ag基合金配線電極膜およびAg基合金スパッタリングターゲット、並びにフラットパネルディスプレイ

【課題】 優れた電気伝導性を示すと共に、大気中で繰り返し高温加熱処理が施された場合であっても、優れた耐凝集性を示すフラットパネルディスプレイ用Ag基合金配線電極膜を提供する。

【解決手段】 フラットパネルディスプレイ用の配線電極膜であって、Biを0.01〜1.5at%含有し(Cu、Au及びPdよりなる群から選択される1種以上を合計で0.1〜1.5at%含んでいてもよい)、残部実質的にAgからなることを特徴とするフラットパネルディスプレイ用Ag基合金配線電極膜。

(もっと読む)

シリサイド膜の形成方法

【課題】 シリサイド膜を薄くしても細線効果を抑えることが可能なシリサイド膜の形成方法を提供する。

【解決手段】 SOI基板全面に対してアルゴンイオンを注入した後,基板を約300℃に調整し,ロングスロー・スパッタリング法を用いてチタン膜21(膜厚15nm)を形成する。基板を大気に曝すことなく連続的にチタン窒化膜23(膜厚30nm)を形成する。窒素雰囲気中で1回目の熱処理(750℃)を行い,ゲート領域,ソース領域,およびドレイン領域にそれぞれ自己整合的にシリサイド膜31,32,33(膜厚30nm)を形成する。チタン窒化膜と未反応のチタン膜を除去した後,2回目の熱処理(850℃)を行う。高抵抗の結晶構造C49を有するシリサイド膜31,32,33は,低抵抗の結晶構造C54を有するシリサイド膜に相転移する。

(もっと読む)

電界効果型トランジスタ

【課題】バックグランドキャリアに起因したオフ電流の低減を可能とする構造を有する電界効果型トランジスタを提供する。

【解決手段】電界効果型トランジスタは、ゲート電極12、ゲート絶縁層13、ソース/ドレイン電極21、並びに、ゲート電極12へのゲート電圧への印加によって誘起されるチャネル領域15をその一部分に有する有機半導体材料層14を備えており、ソース/ドレイン電極21は、(a)ゲート絶縁層13及びチャネル領域15を構成する有機半導体材料層14の部分に接しており、チャネル領域15に電荷注入可能な第1の導電材料から成る第1導電材料層22、並びに、(b)チャネル領域15を構成しない有機半導体材料層14の部分に接しており、第1の導電材料よりも有機半導体材料層14への電荷注入効率の悪い第2の導電材料から成る第2導電材料層23から成る。

(もっと読む)

681 - 700 / 732

[ Back to top ]