Fターム[5F110AA07]の内容

Fターム[5F110AA07]に分類される特許

161 - 180 / 669

薄膜トランジスタ、表示装置及び薄膜トランジスタの作製方法

【課題】チャネル形成領域に結晶化率の高い領域を配し、ソースとドレインの間に高抵抗な領域を配し、電界効果移動度が高くオン電流が大きい薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタの下地層に「結晶核の生成を抑制する不純物」を含ませ、または下地層の表面に「結晶核の生成を抑制する不純物」を存在させ、下地層上に設けられた第1の配線層と、第1の配線層に少なくとも一部が接する不純物半導体層と、少なくとも一部が不純物半導体層を介して第1の配線層と電気的に接続される半導体層と、半導体層上に設けられた第1の絶縁層と、少なくとも半導体層と第1の絶縁層を覆って設けられた第2の絶縁層と、第2の絶縁層上であって、不純物半導体層の少なくとも一部、及び不純物半導体層によって形成されるソース領域とドレイン領域の間に重畳して設けられた第2の配線層と、を有する薄膜トランジスタとする。

(もっと読む)

薄膜トランジスタ

【課題】電気特性が良好な薄膜トランジスタを提供する。

【解決手段】ゲート電極を覆うゲート絶縁層と、ゲート絶縁層に接し、且つ凹凸状の微結晶半導体領域及び非晶質半導体領域を有する半導体層と、半導体層の一部に接し、不純物半導体層と、不純物半導体層に接する配線と、微結晶半導体領域及び配線の間に形成される第1の酸化物領域と、非晶質半導体領域及び配線の間に形成される第2の酸化物領域とを有し、エネルギー分散型X線分光法において測定される、配線を構成する元素のプロファイル及び半導体層を構成する元素のプロファイルの交点から、半導体層側において、第1の酸化物領域における酸素プロファイルの最大傾き接線m1及び第2の酸化物領域における酸素プロファイルの最大傾き接線m2は、1<m1/m2<10である薄膜トランジスタである。

(もっと読む)

薄膜トランジスタ及びその作製方法

【課題】チャネル形成領域に結晶化率の高い領域を配し、電界効果移動度が高く、オン電流が大きい薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタの半導体層中に逆錐形状の結晶粒を含ませ、下地層上に設けられた第1の配線層と、第1の配線層に少なくとも一部が接する不純物半導体層と、少なくとも一部が不純物半導体層を介して第1の配線層と電気的に接続される半導体層と、半導体層上に設けられた第1の絶縁層と、少なくとも半導体層と第1の絶縁層を覆って設けられた第2の絶縁層と、第2の絶縁層上であって、不純物半導体層の少なくとも一部、及び不純物半導体層によって形成されるソース領域とドレイン領域の間に重畳して設けられた第2の配線層と、を有する薄膜トランジスタとする。

(もっと読む)

薄膜トランジスタとその作製方法

【課題】薄膜トランジスタのオン電流を大きくする。

【解決手段】薄膜トランジスタのバックチャネル部に凸部を設ける。該凸部は、ソースまたはドレインからチャネル形成領域まで引いたバックチャネル部の接線を避けて設けられる。該凸部により電荷のトラップ箇所とオン電流の経路を遠ざけることができ、オン電流を大きくすることができる。バックチャネル部の側面の形状は曲面であってもよいし、断面において直線で表される形状であってもよい。更には、一括してエッチングを行うことでこのような形状を形成する方法を提供する。

(もっと読む)

薄膜トランジスタ

【課題】電気特性が良好で生産性の高い薄膜トランジスタを提供する。

【解決手段】ゲート電極を覆うゲート絶縁層と、ゲート絶縁層に接する半導体層と、半導体層の一部に接し、ソース領域及びドレイン領域を形成する不純物半導体層と、不純物半導体層に接する配線とを有し、半導体層において、ゲート絶縁層側に形成される凹凸状の微結晶半導体領域と、当該微結晶半導体領域に接する非晶質半導体領域とを有し、半導体層及び配線の間に障壁領域を有する薄膜トランジスタである。

(もっと読む)

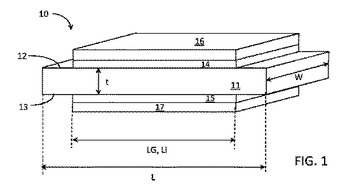

多層拡張ドレイン構造を有する高電圧ラテラルトランジスタ

【課題】低いオン抵抗特性を有し、オフ状態において高電圧を維持する高電圧トランジスタいを提供する。

【解決手段】低いオン抵抗特性を有し、オフ状態において高電圧を維持する高電圧トランジスタは、多層拡張ドレイン構造の近傍に一又は二以上のソース領域が配置されており、この構造は、一又は二以上の誘電体層によってフィールドプレート部材から分離された拡張されたドリフト領域を含んでいる。フィールドプレート部材は最も低い回路ポテンシャルにおいて、トランジスタはオフ状態においてドレインに印加される高電圧を維持する。層状の構造は、種々の方法で製造することができる。MOSFET構造は、ソース領域近傍のデバイスに組み込まれるか、あるいはMOSFET構造を省略して、スタンドアロンのドリフト領域を有する高電圧トランジスタ構造を製造することができる。

(もっと読む)

薄膜トランジスタ

【課題】電気特性が良好な薄膜トランジスタを、生産性高く作製する方法を提供する。

【解決手段】ゲート電極を覆うゲート絶縁層と、ゲート絶縁層に接する半導体層と、半導体層の一部に接し、ソース領域及びドレイン領域を形成する不純物半導体層と、不純物半導体層に接する配線とを有し、半導体層において、ゲート絶縁層側に形成される凹凸状の微結晶半導体領域と、当該微結晶半導体領域に接する分離された非晶質半導体領域とを有し、微結晶半導体領域は、非晶質半導体領域に覆われていない第1の微結晶半導体領域と、分離された非晶質半導体領域と接する第2の微結晶半導体領域とで形成され、第1の微結晶半導体領域の厚さd1は第2の微結晶半導体領域の厚さd2より薄く、且つ第1の微結晶半導体領域の厚さd1が30nm以上である。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに半導体装置

【課題】薄膜トランジスタのリーク特性を維持しつつ、オン電流を大幅に改善することができる薄膜トランジスタ及びその製造方法並びに半導体装置の製造方法を提供すること。

【解決手段】半導体薄膜を形成する工程と、前記半導体薄膜にシリコンを注入する工程と、チャネル形成領域とソース形成領域及びドレイン形成領域との間にそれぞれ位置するLDD形成領域上にマスクを形成する工程と、前記LDD形成領域上にマスクを形成した半導体薄膜上にシリコンを注入する工程と、前記半導体薄膜を熱処理により結晶化する工程と、を有する薄膜トランジスタの製造方法とした。

(もっと読む)

マルチゲートIII−V量子井戸構造

マイクロ電子構造を形成する方法を記載する。方法の実施形態は、基板上にIII−Vトライゲートフィンを形成する段階と、III−Vトライゲートフィンの周囲にクラッド材を形成する段階と、クラッド材の周りに高誘電率ゲート誘電体を形成する段階とを備える。 (もっと読む)

誘電体分離型半導体装置

【課題】高耐圧かつ、電流駆動能力が高く、かつ電流集中による素子破壊の起こりにくい誘電体分離型半導体装置を提供する。

【解決手段】半導体支持基板の上に、絶縁された第一導電型の半導体領域とを有する誘電分離基板に形成した誘電体分離型半導体装置において、第一導電型の半導体領域と絶縁分離領域の間と、前記第1導電型の半導体領域の基板表面側と、に形成されたドレイン領域と、第一導電型のソースと第二導電型の半導体領域のチャネルからなる複数個の単位ソース領域と、第一導電型の半導体領域の基板表面側に形成されたドレイン領域と前記複数個の単位ソース領域の間を制御する複数個のゲート電極とを、備え、隣接する前記単位ソース領域間に絶縁分離領域が、基板底面側から基板表面側に向けて突き出した形状とされ、この絶縁分離領域上の素子表面領域が前記第一導電型の半導体領域より抵抗値が高い。

(もっと読む)

表示装置

【課題】狭額縁化が可能であり、表示特性に優れた表示装置を提供する。

【解決手段】駆動回路及び画素部を有し、駆動回路は、デュアルゲート型の薄膜トランジスタを用いて構成され、画素部はシングルゲート型の薄膜トランジスタを用いて構成される表示装置である。該表示装置おけるデュアルゲート型の薄膜トランジスタは、半導体層が微結晶半導体領域及び一対の非晶質半導体領域で形成され、ゲート絶縁層及び絶縁層が半導体層の微結晶半導体領域に接する。

(もっと読む)

半導体装置

【課題】良質な半導体装置を提供することを目的としている。

【解決手段】素子分離領域間の凸部108を含むシリコン基板106と、凸部108上の絶縁部112と、絶縁部112上のシリコンフィン114と、上面が凸部108の上面よりも低く位置する素子分離領域内の素子分離層116と、シリコンフィン114に設けられたソース/ドレイン領域と、ソース/ドレイン領域104のシリコンフィン114の側面から外側に突き出た横方向エピ成長シリコン部118と、ゲート電極領域102内のゲート絶縁層122を介してシリコンフィン114上に設けられるゲート電極124と、ゲート電極124の側面に隣接する第1のスペーサ128と、ソース/ドレイン領域104内の凸部108の側面を覆う第2のスペーサ130とを備える。

(もっと読む)

ダブルゲートナノ構造FET

少なくとも1つのナノ構造を備えた電界効果トランジスタ(FET)半導体デバイスであって、少なくとも、2つの主面を有する、均一にドープされたビーム形状のナノ構造と、ナノ構造の各主面に設けられたゲート電極と、ダブルゲートナノ構造ピンチオフFETを形成するための、ナノ構造の各主面とゲート電極との間の絶縁層とを備えたデバイス。FETのピンチオフ電圧及び電流を独立して調整できることが、かかるFETの利点である。  (もっと読む)

(もっと読む)

トランジスタ

【課題】生産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供する。または、新たな半導体材料を用いた新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体中で電子供与体(ドナー)となりうる不純物を除去することで、真性又は実質的に真性な半導体であって、シリコン半導体よりもバンドギャップが大きい酸化物半導体でチャネル形成領域が形成される縦型トランジスタであり、酸化物半導体の厚さが1μm以上、好ましくは3μmより大、より好ましくは10μm以上であり、酸化物半導体に接する電極の一方の端部が、酸化物半導体の端部より内側にある。

(もっと読む)

半導体装置の製造方法

【課題】半導体膜の厚みを適当な範囲に制御することによって、大きいドレイン電流を有するとともに、所望の電気的特性を備える半導体装置の製造方法、を提供する。

【解決手段】半導体装置の製造方法は、50nmを超え150nm以下の厚みを有し、第1の層7mと第2の層7nとを有する半導体膜7を形成する工程を備える。半導体膜7を形成する工程時、第1の層7mに含まれる水素の割合は、第2の層7nに含まれる水素の割合よりも小さい。半導体装置の製造方法は、半導体膜7を熱処理することによって、半導体膜7に含まれる水素を低減する工程と、ゲート絶縁膜17およびゲート電極21を形成する工程と、半導体膜7にソース領域9およびドレイン領域13を形成する工程と、半導体膜7を水素雰囲気中で熱処理することによって、半導体膜7に含まれる水素を0.5原子%以上10原子%以下に設定する工程とを備える。

(もっと読む)

電界効果トランジスタ

【課題】蛇行した形状に形成されたリセス部を備えることにより、オン抵抗を低減することができる電界効果トランジスタを提供することを目的とする。

【解決手段】電界効果トランジスタ1は、チャネル層11と、チャネル層11とヘテロ接合を構成するキャリア供給層12と、キャリア供給層12の表面から掘り下げて形成されたリセス部13と、リセス部13に沿って形成された第1絶縁層31と、第1絶縁層31の上に形成された第1ゲート電極23と、リセス部13に対してチャネル長方向の一方側に形成されたソース電極21と、リセス部13に対してチャネル長方向の他方側に形成されたドレイン電極22とを備える。リセス部13は、ソース電極21とドレイン電極22とが平面視で平行に対向するチャネル長の範囲内において、蛇行しながらチャネル長方向と交差する方向に延長されている。

(もっと読む)

半導体装置

【課題】ソース・ゲート間およびドレイン・ゲート間に発生する2次元電子ガスの濃度を最適にしたまま、オン抵抗を低くして、消費電力の低い半導体装置を提供する。

【解決手段】第2のAlGaN層6のAlの組成比は、第1のAlGaN層5のAlの組成比よりも大きい。このため、ゲート電極8に電圧を印加したとき、GaN層3の凹溝30の内面の側面31と第2のAlGaN層6との第1の界面S1に2次元電子ガスを発生させつつ、第2のAlGaN層6における凹溝30の内面の側面31に平行な部分と絶縁層7との第2の界面S2に2次元電子ガスを発生させることを抑制できる。

(もっと読む)

非線形素子、表示装置、および電子機器

【課題】逆方向飽和電流の低い非線形素子(例えば、ダイオード)を提供する。

【解決手段】例えば、基板上に設けられた第1の電極と、前記第1の電極上に接して設けられ、二次イオン質量分析法で検出される水素濃度が5×1019atoms/cm3以下である酸化物半導体膜と、前記酸化物半導体膜上に接して設けられた第2の電極と、前記第1の電極、前記酸化物半導体膜、及び前記第2の電極を覆うゲート絶縁膜と、前記ゲート絶縁膜に接して設けられ、前記第1の電極、前記酸化物半導体膜、及び前記第2の電極を介して対向する複数の第3の電極と、を有し、前記複数の第3の電極は、前記第1の電極または前記第2の電極と接続されている非線形素子を提供する。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法および使用方法

【課題】 スイッチング速度の低下やオン抵抗の増大を抑制しつつ、オフ耐圧を改善可能な半導体装置を提供する。

【解決手段】

半導体層11および12は、基板10上に形成され、第1の電極101、第2の電極102および絶縁膜14は、それぞれ、半導体層11および12上に形成され、絶縁膜14は、第1の電極101と第2の電極102との間に配置され、フィールドプレート電極17Aおよび17Bは、複数であり、かつ、絶縁膜14上に点在し、第1の電極101および第2の電極102は、半導体層11および12を介して電気的に接続されており、前記第1の電極と前記第2の電極との間の電圧印加時における電流の方向と垂直方向の各フィールドプレート電極の長さ、および、前記電流の方向と垂直方向に隣接する各フィールドプレート電極間の距離が、それぞれ、第1の電極101と第2の電極102との間の距離以下であることを特徴とする半導体装置。

(もっと読む)

電界効果型トランジスタ

【課題】動作速度が速く、オン時には大電流を流すことができ、オフ時にはオフ電流がきわめて低減された電界効果型トランジスタ、例えば薄膜トランジスタを提供する。

【解決手段】酸化物半導体に含まれる水素が5×1019/cm3以下、好ましくは5×1018/cm3以下、より好ましくは5×1017/cm3以下として、酸化物半導体に含まれる水素若しくはOH基を除去し、キャリア濃度を5×1014/cm3以下、好ましくは5×1012/cm3以下とした酸化物半導体膜でチャネル形成領域が形成される縦型薄膜トランジスタである。

(もっと読む)

161 - 180 / 669

[ Back to top ]