Fターム[5F110AA07]の内容

Fターム[5F110AA07]に分類される特許

201 - 220 / 669

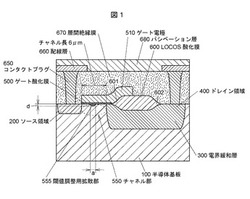

高耐圧半導体装置及びその製造方法

【課題】チャネルの閾値調整が容易で、オン抵抗の小さい高耐圧半導体装置及びその製造方法を提供する。

【解決手段】第1導電型であるp型の半導体基板100上に形成された第2導電型であるn型のソース領域200と、半導体基板100の表面から所定の深さまで形成された第2導電型であるn型の電界緩和層300と、電界緩和層300の領域内においてソース領域200から遠い領域の上層領域に形成されたドレイン領域400と、ドレイン領域400とソース領域200の間で半導体基板100の表面の活性領域に形成されたゲート酸化膜500と、ゲート酸化膜500の下のチャネル部550の一部に形成される閾値調整用拡散部555と、ドレイン領域400とゲート酸化膜500の間の半導体層表面に形成されたLOCOS酸化膜600と、ゲート酸化膜500上からLOCOS酸化膜600上に張り出して形成されたゲート電極510と、を有して構成する。

(もっと読む)

トランジスタ回路

【課題】 高耐圧の薄膜トランジスタと高電流駆動能力を持った薄膜トランジスタを同一基板上に形成する。

【解決手段】 絶縁性基板上に形成され、半導体層、ソース領域、ドレイン領域で構成される薄膜トランジスタを備えるトランジスタ回路において、半導体層の下側に第1の絶縁層を介してボトムゲート層があり、半導体層を挟んでボトムゲート層と対向する側に第2の絶縁層を介してトップゲート層を具備した少なくとも一つの第1の薄膜トランジスタと、半導体層の下側に第1の絶縁層を介してボトムゲート層のみを具備する少なくとも一つの第2の薄膜トランジスタと、を同一基板上に形成したことを特徴とする。

(もっと読む)

微結晶半導体膜及び薄膜トランジスタの作製方法

【課題】結晶性の高い微結晶半導体膜を作製する。また、本電気特性が優れ、信頼性の高い薄膜トランジスタ、及びそれを有する表示装置を量産性高く作製する。

【解決手段】一定流量の水素を導入しつつ、第1の流量のシリコンまたはゲルマニウムを含む堆積性気体を導入する工程と、第2の流量のシリコンまたはゲルマニウムを含む堆積性気体を導入する工程とを繰り返して、水素及びシリコンまたはゲルマニウムを含む堆積性気体を混合し、高周波電力を供給して、基板上に微結晶半導体膜を作製する。

(もっと読む)

トンネル電界効果デバイス

【課題】 トンネル電界効果トランジスタ(TFET)構造用の間接誘導トンネル・エミッタを提供する。

【解決手段】 このTFET構造は、第1の半導体材料から形成された細長いコア・エレメントを少なくとも部分的に取り囲み、TFET構造のソース領域に対応する位置に配置された外装と、外装とコア・エレメントとの間に配置された絶縁体層と、外装をコア・エレメントにショートさせるソース接点とを含み、ON状態中にTFET構造のチャネル領域内にトンネリングするために十分なキャリア濃度をコア・エレメントのソース領域に導入するように外装が構成される。

(もっと読む)

トランジスタ及びトランジスタの製造方法

【課題】トランジスタのオン電流の安定を図ること。

【解決手段】トランジスタ(駆動トランジスタ6、スイッチトランジスタ5)における半導体膜6b、5bを、チャネル保護膜6d、5dで覆われているチャネル領域よりも、チャネル保護膜6d、5dで覆われていない領域の方を薄く形成することによって、その半導体膜6b、5b上に密着性よく不純物半導体膜(6f,6g、5f,5g)を形成し、そのトランジスタ6、5のオン電流を所望する値に安定させるように、オン電流を好適に向上させることを可能にした。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタを構成する各部材の抵抗を小さくし、トランジスタのオン電流の向上を図り、集積回路の高性能化を図ることを課題の一とする。

【解決手段】単結晶半導体基板上に絶縁層を介して設けられ、素子分離絶縁層によって素子分離されたn型FET及びp型FETを有する半導体装置であって、それぞれのFETは、半導体材料を含むチャネル形成領域と、チャネル形成領域に接し、半導体材料を含む導電性領域と、導電性領域に接する金属領域と、チャネル形成領域に接するゲート絶縁層と、ゲート絶縁層に接するゲート電極と、金属領域を一部に含むソース電極またはドレイン電極と、を有する。

(もっと読む)

半導体装置

【課題】窒化物半導体を用いたノーマリオフ型のトランジスタを備えた半導体装置において、駆動時のゲート電流を低減しつつ、トランジスタの過渡応答特性を安定させる。

【解決手段】半導体装置は、基板101と、基板101の上に積層された複数の窒化物半導体層からなり、且つチャネル領域を含む第1の窒化物半導体層104Sと、第1の窒化物半導体層104Sの上に形成され、且つチャネル領域と逆導電型の第2の半導体層105と、第2の半導体層105に接するように形成され、金属層107からなる導電層と、導電層の上に形成された絶縁体層110と、絶縁体層110の上に形成されたゲート電極111と、第2の半導体層105の両側方に形成されたソース電極108及びドレイン電極109とを備えている。

(もっと読む)

薄膜トランジスタ及びその作製方法

【課題】オフ電流が低く、オン電流及び電界効果移動度が高い薄膜トランジスタを提供する。

【解決手段】逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁層として窒化シリコン層と当該窒化シリコン層が酸化された酸化シリコン層を積層して形成し、該ゲート絶縁層の酸化シリコン層との界面直上から結晶成長した微結晶半導体層を形成する。ゲート絶縁層の直上から結晶成長するため、結晶性の高いオン電流及び電界効果移動度が高い薄膜トランジスタとすることができる。また、バッファ層を設けてオフ電流を低減させる。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタを構成する各部材の抵抗を小さくし、トランジスタのオン電流の向上を図り、集積回路の高性能化を図ることを課題の一とする。

【解決手段】単結晶半導体基板上に絶縁層を介して設けられ、素子分離絶縁層によって素子分離されたn型FET及びp型FETを有する半導体装置であって、それぞれのFETは、半導体材料を含むチャネル形成領域と、チャネル形成領域に接し、半導体材料を含む導電性領域と、導電性領域に接する金属領域と、チャネル形成領域に接するゲート絶縁層と、ゲート絶縁層に接するゲート電極と、金属領域を一部に含むソース電極またはドレイン電極と、を有する。

(もっと読む)

半導体装置

【課題】オン抵抗、出力容量を低減した半導体装置を提供する。

【解決手段】絶縁層2の上に互いに接して設けられた、第2導電型の第1の半導体層34、前記第1の半導体層よりも不純物濃度の低い第2導電型の第2の半導体層33、第1導電型の第3の半導体層31、前記第3の半導体層よりも不純物濃度の高い第1導電型の第4の半導体層32、前記第4の半導体層の表面に設けられた第2導電型の第5の半導体層35と、前記第2の半導体層と前記第3の半導体層との境界の上に設けられたトレンチ溝51と、前記トレンチ溝内及び前記トレンチ溝外の前記第2,第3,第4の半導体層の上に絶縁膜42を介して設けられた制御電極23と、前記第1の半導体層の上に設けられた第1の主電極21と、前記第4,第5の半導体層の上に前記制御電極と離隔して設けられた第2の主電極22と、を備える半導体装置。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタにおけるオン電流の向上とリーク電流の低減を図る。

【解決手段】微結晶シリコン領域51の両端側が非晶質シリコン領域52となっている半導体膜5bを備えるスイッチトランジスタ5において、チャネル保護膜5dが、半導体膜5bにおける微結晶シリコン領域51を覆いつつ、そのチャネル保護膜5dの両端側で、微結晶シリコン領域51側の非晶質シリコン領域52の一部を覆い、また、ソース・ドレイン領域となる不純物半導体膜5f,5gが、微結晶シリコン領域51と直接接触せず、半導体膜5bにおける非晶質シリコン領域52と接することで、ドレイン電極5hとソース電極5iとが不純物半導体膜5f,5gを介して半導体膜5bと電気的に接続することで、微結晶シリコンに起因するホールエレクトロンペアの発生を抑えて、リーク電流の低減を図った。

(もっと読む)

半導体装置、それを用いたプラズマディスプレイ駆動用半導体集積回路装置、及びプラズマディスプレイ装置

【課題】SOI基板上に形成される、電流密度の大きな横型IGBTを提供する。

【解決手段】酸化膜溝側に2つ以上の第二導電型ベース層からなるエミッタ領域を有し、エミッタ領域の第二導電型ベース層をドリフト層より高濃度の第一導電型層で覆う横型IGBT構造において、酸化膜溝側のゲート電極長をコレクタ側のゲート電極長より縮小し、前記高濃度の第一導電型層を前記第二導電型ベース層間とコレクタ側の前記第二導電型ベース層下に形成することにより、耐圧を維持したまま前記の第一導電型層の高濃度化が実現し電流密度が向上する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に、酸化物半導体層より導電率の高いバッファ層を形成し、該バッファ層の上にソース電極層及びドレイン電極層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

薄膜トランジスタ

【課題】薄膜トランジスタのオン電流及びオフ電流に係る問題点を解決することを課題の一とする。

【解決手段】薄膜トランジスタにおいて、ゲート絶縁層と、ソース領域及びドレイン領域との間であって、且つ少なくともソース領域及びドレイン領域側に、窒素を有し且つ非晶質構造の中で結晶領域を有する半導体層をバッファ層として有する。非晶質半導体をチャネル形成領域に有する薄膜トランジスタと比較して、薄膜トランジスタのオン電流を高めると共に、微結晶半導体をチャネル形成領域に有する薄膜トランジスタと比較して、薄膜トランジスタのオフ電流を低減することができる。

(もっと読む)

薄膜トランジスタ及び表示装置

【課題】半導体層をゲート電極によって遮光したボトムゲート型薄膜トランジスタのオフ電流を低減する。

【解決手段】ゲート電極層と、第1の半導体層と、前記第1の半導体層上に接して設けられた前記第1の半導体層よりもキャリア移動度が低い第2の半導体層と、前記ゲート電極層と前記第1の半導体層との間に接して設けられたゲート絶縁層と、前記第2の半導体層に接して設けられた不純物半導体層と、前記不純物半導体層及び前記第1及び第2の半導体層に一部が接して設けられたソース電極及びドレイン電極層と、を有し、前記第1の半導体層のゲート電極層側は全面が前記ゲート電極層によって覆われており、前記第1の半導体層と前記ソース電極及びドレイン電極層が接する部分のポテンシャル障壁は0.5eV以上である薄膜トランジスタを提供する。

(もっと読む)

トランジスタの製造方法、トランジスタ及び回路基板

【課題】優れた電気特性を有するトランジスタの製造方法、トランジスタ及び回路基板を提供する。

【解決手段】トランジスタ1は、基板10と、基板10の表面に形成されたゲート電極12と、基板10上にゲート電極12を覆うように形成されたゲート絶縁膜14と、ゲート電極12の両側にゲート絶縁膜14を介して形成されたソース電極16及びドレイン電極18と、ソース電極16及び前記ドレイン電極18上の厚肉部220とソース電極16及びドレイン電極18によって挟まれたゲート絶縁膜14上に設けられ、厚肉部220よりも膜厚の薄い薄肉部222と薄肉部222上の一部に形成された凸部224とを有する有機半導体膜22と、を備えて概略構成されている。

(もっと読む)

薄膜トランジスタ及びその製造方法、電気光学装置、並びにセンサー

【課題】オン電流が高く、特性シフトが低減された薄膜トランジスタを提供する。

【解決手段】基板上に、活性層としてのIn、Ga、及びZnを含む酸化物半導体膜と、ゲート電極と、ゲート絶縁膜と、ソース電極と、ドレイン電極と、を有し、

前記酸化物半導体膜のモル比〔In:Ga:Zn〕を2.0−x:x:y(但し、0.0<x<2.0、0.0<y)で表したとき、前記酸化物半導体膜の膜厚方向についての前記yの分布において、前記基板に近い側の膜面、及び、前記基板から離れた側の膜面よりも、前記yが大きい領域が存在する。

(もっと読む)

トランジスタを有するトランジスタ基板及びトランジスタを有するトランジスタ基板の製造方法

【課題】微結晶シリコンをチャンネル領域として用い、コンタクト歩留まりを向上させ、良好な特性を備えるトランジスタを有するトランジスタ基板及びその製造方法を提供する。

【解決手段】トランジスタ100は、基板11と、ゲート電極112と、ゲート絶縁膜113と、第1の半導体層114と、第2の半導体層115と、ストッパ膜116と、オーミックコンタクト層117、118と、ドレイン電極119と、ソース電極120と、を備える。微結晶シリコンを用いた第1の半導体層114上に第2の半導体層115を積層させた上で、第1の半導体層114及び第2の半導体層115の側面でオーミックコンタクト層117、118とコンタクトを取ることにより、コンタクト歩留まりを向上させ、良好な特性を備えるトランジスタを有するトランジスタ基板及びその製造方法を提供することができる。

(もっと読む)

半導体装置

【課題】10GHz程度以上のクロック周波数での動作が可能な高速半導体装置の提供。

【解決手段】n−MOSFET100n、p−MOSFET100pを有し、n−MOSFETのチャンネルを形成する第1の領域の表面が(100)面から±10°以内の面または(110)面から±10°以内の面のを有し、p−MOSFETのチャンネルを形成する第2の領域の表面が((110)面から±10°以内の面または(100)面から±10°以内の面のを有し、第1及び第2の領域の各々から各々の両端の前記ソース電極、ドレイン電極の各々までの抵抗を4Ω・μm以下とし、かつ第1の領域と第1のゲート絶縁層との界面及び第2の領域と第2のゲート絶縁層との界面を、各領域のソースからドレインに向かう方向での長さ2nmにおけるピーク・トゥ・バレイが0.3nm以下であるような平坦度とした半導体装置。

(もっと読む)

半導体装置

【課題】インパクトイオン化現象によって発生した電子・正孔を効率よく吸収することが可能で正常な動作特性と高い信頼性を実現する半導体装置を提供する。

【解決手段】半導体装置20は、基板21に対して順次積層されたバッファ層22、下地化合物半導体層23f(下地化合物半導体層23)、インパクトイオン制御層24、下地化合物半導体層23s(下地化合物半導体層23)、チャネル画定化合物半導体層26f(チャネル画定化合物半導体層26)、チャネル画定化合物半導体層26s(チャネル画定化合物半導体層26)、AlGaN(窒化アルミニウムガリウム)層28、GaN(窒化ガリウム)層29を備えている。インパクトイオン制御層24は、下地化合物半導体層23の積層範囲(積層範囲の厚さTst)内に積層されてインパクトイオン化現象の発生位置を制御する。

(もっと読む)

201 - 220 / 669

[ Back to top ]