Fターム[5F110AA13]の内容

Fターム[5F110AA13]に分類される特許

1 - 20 / 248

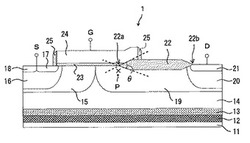

半導体装置およびその製造方法

【課題】LOCOS酸化膜端部の直下の電界集中が容易に緩和され、LOCOS酸化膜直下の半導体導電層の良好な耐圧および抵抗を実現することのできる半導体装置を提供する。

【解決手段】半導体装置(1)は、LOCOS酸化膜(22)の半導体基板の表面に対してラテラル方向に終端しているエッジ(22a、22b)の少なくとも一部(22a、22b)が、上面と下面とに15度以上30度以下の角度(θ)で挟まれて終端するプロファイルを有している。

(もっと読む)

半導体装置の作製方法

【課題】量産性の高い新たな半導体材料を用いた大電力向けの半導体装置の作製方法を提供する。

【解決手段】GRTA装置を用いて、第1の酸化物半導体膜に熱を加え、熱が加えられた第1の酸化物半導体膜に、酸素を添加して第2の酸化物半導体膜とし、GRTA装置を用いて、酸素が添加された第2の酸化物半導体膜に熱を加える。GRTA装置は、高温のガスを用いて加熱処理を行う装置であって、当該GRTA装置を用いると短時間での高温加熱処理が可能となる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】ソース領域110は、溝部300側面の第2面32に面し、一部が面31と面32の交線と平行な方向に延在する。ドリフト領域140は、溝部300のうち面32と反対の面33に面し、一部が面31および面33の交線と平行な方向に延在して設けられ、ソース領域110よりも低濃度に形成される。ドレイン領域120は、ドリフト領域140を介し溝部300の反対側に位置し、ドリフト領域140と接するように設けられ、ドリフト領域140よりも高濃度に形成される。第1ゲート絶縁層200は、溝部300の側面のうち面32と面33に交わる方向の面である面34と接するとともに、面31上のうち少なくともチャネル領域130と接する。ゲート電極400は、第1ゲート絶縁層200上に設けられ。溝部300はドリフト領域140よりも深い。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】比較的簡素な構成で電流コラプスの発生を抑制し、デバイス特性の劣化を抑えた信頼性の高い高耐圧のAlGaN/GaN・HEMTを実現する。

【解決手段】SiC基板1上に化合物半導体積層構造2を備えたAlGaN/GaN・HEMTにおいて、3層のキャップ層2eを用いることに加え、キャップ層2eのドレイン電極5の近傍(ゲート電極6とドレイン電極5との間で、ドレイン電極5の隣接箇所)に高濃度n型部位2eAを形成し、高濃度n型部位2eAでは、そのキャリア濃度が電子供給層2dのキャリア濃度よりも高く、そのエネルギー準位がフェルミエネルギーよりも低い。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】第1導電型の第1ドリフト領域140は、平面視でソース領域110から離間して設けられている。第1導電型の第2ドリフト領域150は、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第1導電型のドレイン領域120は、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。チャネル領域130上には、ゲート絶縁層200およびゲート電極400が設けられている。第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接している。

(もっと読む)

半導体装置

【課題】インバータ回路を構成する直列接続された素子を備えた半導体装置において、その直列接続の高電位配線の影響による耐圧低下が生じるのを防止する半導体装置の提供。

【解決手段】第1および第2の素子は、各々、電流のスイッチングを行うトランジスタと、還流を行うダイオードとを含み、かつ、トランジスタの第1主電極とダイオードの第1主電極が電気的に接続され、トランジスタの第2主電極とダイオードの第2主電極が電気的に接続され、第1の素子および第2の素子は、第1の素子におけるトランジスタの第1主電極と、第2の素子におけるトランジスタの第2主電極が電気的に接続され、かつ、半導体基板を平面視したときに、第1の素子におけるトランジスタの第1主電極とドリフト領域の間の導電性半導体領域と、第2の素子におけるトランジスタの第2主電極とドリフト領域の間の導電性半導体領域とが対向するように、配置されていることを特徴とする。

(もっと読む)

横型素子を有する半導体装置

【課題】耐圧バラツキを抑制し、歩留りを向上させることが可能となる横型素子を有する半導体装置を提供する。

【解決手段】横型FWDなどの横型素子に備えられるSRFP21について、の不純物濃度を1×1018cm-3以上となるようにする。このように、横型FWD7などに備えられるSRFP21について、の不純物濃度を1×1018cm-3以上とすることにより、耐圧バラツキを抑制することが可能となり、的確に目標とする耐圧を得ることができる製品とすることが可能になる。したがって、製品の歩留りを向上させることが可能となる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いたボトムゲート型のトランジスタにおいて、高いゲート電圧がゲート電極層に印加される場合、ドレイン電極層の端部近傍(及びソース電極層の端部近傍)に生じる恐れのある電界集中を緩和し、スイッチング特性の劣化を抑え、信頼性が向上された構造を提供する。

【解決手段】チャネル形成領域上に重なる絶縁層の断面形状を、テーパ形状とし、チャネル形成領域上に重なる絶縁層の膜厚は、0.3μm以下、好ましくは5nm以上0.1μm以下とする。チャネル形成領域上に重なる絶縁層の断面形状の下端部のテーパ角θを60°以下、好ましくは45°以下、さらに好ましくは30°以下とする。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

半導体装置

【課題】耐圧の低下を抑制しつつ電流駆動能力の向上と小型化とを実現できる半導体装置を提供する。

【解決手段】半導体装置1は、SOI基板の半導体層の上面に沿って形成されたゲート電極31と、ソース拡散領域181〜18Nと、電荷収集領域191〜19N+1と、ドレイン拡散領域16と、電界緩和領域17とを備える。ソース拡散領域181〜18Nと電荷収集領域191〜19N+1とは、Y軸方向に沿って交互に配列されている。ソース拡散領域181〜18Nの各々の幅をWeffとし、ゲート電極31の長さをLgとし、ゲート電極31とドレイン拡散領域16との互いに対向する端部間の距離をLdriftとするとき、Weff/2≦Lg+Ldrift/2、との関係式が成立する。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス条件の見直しを最小限に抑制しつつ電気的特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、半導体構造11の上面領域に形成された島状の絶縁膜20と、絶縁膜20の上面領域に配列された複数の凸状絶縁部23と、これら凸状絶縁部23と絶縁膜20とを被覆する層間絶縁膜26とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

トランジスタ

【課題】新たな半導体材料を用いたトランジスタを提供する。

【解決手段】水素濃度が1×1016cm−3以下の領域を有する酸化物半導体層又はキャリア密度が1×1014cm−3未満の領域を有する酸化物半導体層を有し、酸化物半導体層の膜厚は、酸化物半導体層のドナー密度に基づく空乏層の広がり得る最大幅よりも薄いトランジスタである。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物イオンの注入による悪影響を防止しつつ水平方向の耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、素子を構成し、電流が流れる一対の不純物領域が、半導体基板の第1主面の表層に形成されたものであり、水平方向の耐圧を確保するため、フィールドプレート33を有している。これに加えて、この半導体装置は、半導体基板の表面から、素子の電流経路となる第1不純物領域37および第2不純物領域38よりも深い所定の深さおいて、少なくとも第1不純物領域および第2不純物領域の間の領域に半導体基板と同一成分の非晶質層24を有する。この非晶質層は、単結晶および多結晶よりも高抵抗の層であり、擬似的なフィールドプレートとして機能する。そして、この非晶質層は、不活性元素のイオン注入により形成される。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワー絶縁ゲート型電界効果トランジスタ(パワーMISFET)を提供する。

【解決手段】半導体層103を挟んでゲート電極105とドレイン電極102を形成し、ゲート電極105の側面に半導体層109を形成し、ゲート電極105の頂上部と重なる部分で、半導体層109とソース電極112が接する構造を有する。このようなパワーMISFETのドレイン電極とソース電極の間に500V以上の電源と負荷を直列に接続し、ゲート電極105に制御用の信号を入力して使用する。

(もっと読む)

半導体装置

【課題】高耐圧を確保でき、かつ大電流を流すことができるMOSトランジスタを備えた半導体装置を提供する。

【解決手段】P型拡散層15に起因してN型拡散層13に第1空乏層23が形成される。ゲート電極19にゲート電圧が印加されていない状態では、P型ポリシリコンからなるゲート電極19及びN型拡散層13の仕事関数差に起因してN型拡散層13に第2空乏層25が形成される。空乏層23,25によってソースコンタクト用拡散層9とドレインコンタクト用拡散層11が電気的に遮断される。ゲート電極19にゲート電圧が印加された状態では、第2空乏層25が消滅又は縮小することによってソースコンタクト用拡散層9とドレインコンタクト用拡散層11がN型拡散層13を介して電気的に導通する。

(もっと読む)

半導体装置の作製方法

【課題】トランジスタの微細化を達成し、電界緩和がなされた、酸化物半導体を用いた半導体装置を提供することを課題の一とする。

【解決手段】ゲート電極の線幅を微細化し、ソース電極層とドレイン電極層の間隔を短縮する。ゲート電極をマスクとして自己整合的に希ガスを添加し、チャネル形成領域に接する低抵抗領域を酸化物半導体層に設けることができるため、ゲート電極の幅、即ちゲート配線の線幅を小さく加工しても位置精度よく低抵抗領域を設けることができ、トランジスタの微細化を実現できる。

(もっと読む)

半導体装置

【課題】高い開口率を有し、安定した電気特性を有する薄膜トランジスタを有する、信頼

性のよい表示装置を作製し、提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動

回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物

半導体によって構成された駆動回路用薄膜トランジスタと、金属によって構成された駆動

回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体に

よって構成され且つ半導体層が酸化物半導体によって構成された画素用薄膜トランジスタ

と、酸化物導電体によって構成された表示部用配線とを有する。

(もっと読む)

半導体装置

【課題】パワーデバイスである大電力用途向けの電界効果トランジスタにおいて、特性の良好な電界効果トランジスタを提供する。

【解決手段】第1のゲート電極と、第1のゲート電極を覆うゲート絶縁層と、第1のゲート電極と重畳して、且つゲート絶縁層と接する酸化物半導体層と、酸化物半導体層の端部を覆うキャリア密度の高い酸化物半導体層と、キャリア密度の高い酸化物半導体層と接するソース電極及びドレイン電極と、ソース電極、ドレイン電極及び酸化物半導体層を覆う絶縁層と、絶縁層と接し、且つ、ソース電極及びドレイン電極の間に設けられる第2のゲート電極と、を有し、キャリア密度の高い酸化物半導体層は、酸化物半導体層を介して対向し、且つ酸化物半導体層の端部の上面、下面、及び側面のそれぞれ一部、並びにゲート絶縁層の上面一部と接する半導体装置である。

(もっと読む)

半導体装置とその製造方法

【課題】 半導体装置を高耐圧化する技術を提供することを目的とする。

【解決手段】 半導体装置100は、p型の埋込み層26と、p型埋込み層26上に設けられており、ヘテロ接合面3が構成されている窒化物半導体のヘテロ接合層32を備えている。p型埋込み層26は、ソース電極10側からドレイン電極2側に向けて厚みが減少する厚み減少部24を有している。厚み減少部24では、ソース電極10側の減少開始点14からドレイン電極2側の減少終了点16までの長さ24bが、減少開始点14における厚み24aよりも長い。

(もっと読む)

1 - 20 / 248

[ Back to top ]