Fターム[5F110AA15]の内容

Fターム[5F110AA15]に分類される特許

1 - 20 / 183

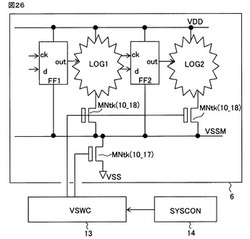

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

絶縁ゲート電界効果トランジスタのシミュレーション方法、シミュレーション装置および集積回路

【課題】広いレンジのゲート長には適用可能な、絶縁ゲート電界効果トランジスタのシミュレーション方法、シミュレーション装置および当該シミュレーション方法によって設計された集積回路を提供する。

【解決手段】ボディコンタクト142を有するSOI絶縁ゲート電界効果トランジスタ10のソース電流またはドレイン電流を、ゲート−ボディオーバラップ領域160の電流を余剰のゲート幅に流れる電流として考慮に入れて求める際に、余剰のゲート幅のゲート長依存性を考慮にいれてソース電流またはドレイン電流をシミュレーションする。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】素子面積の増大を抑制しつつ、駆動電流の高いON/OFF比と安定した特性を実現できる半導体装置及びその製造方法を提供する。

【解決手段】絶縁層と、絶縁層上に形成された半導体層と、半導体層に形成された部分空乏型のトランジスター10とを備え、トランジスター10は、半導体層上に絶縁膜を介して形成されたゲート電極14と、ゲート電極14両側下の半導体層に形成されたソース15又はドレイン16と、ボディーの下部に設けられた不純物層17,18とを有し、不純物層17,18は、ボディー領域の下部の両側端部に形成され、ソース15、ドレイン16とは接しない。

(もっと読む)

半導体装置

【課題】安定したボディ固定動作と共に、高集積化、低寄生容量化や配線容量の低減化を図ることができる、SOI基板上に形成される半導体装置を得る。

【解決手段】ソース領域1,ドレイン領域2及びゲート電極3で形成されるMOSトランジスタにおいて、ゲート一端領域及びゲート他端領域に部分分離領域11a及び11bが形成され、部分分離領域11aに隣接してタップ領域21aが形成され、部分分離領域11bに隣接してタップ領域21bが形成される。部分分離領域11a,11b、タップ領域21a,21b及び活性領域1,2の周辺領域は全て完全分離領域10が形成される。

(もっと読む)

フィン型電界効果トランジスタ

【課題】フィン型電界効果トランジスタはその動作原理から、低消費電力化を図るためには、動作時のバルク領域は完全空乏化される必要があった。結果として、プロセスばらつきがバルク領域のばらつきを生み、消費電力にばらつきを与えるという問題が生じていた。

【解決手段】本発明のフィン型電界効果トランジスタは、ゲート絶縁膜を介してチャネル領域に電界を印加するためのゲート電極を備えるフィン型電界効果トランジスタにおいて、バルク領域に所定の電位を印加するためのバルク電極を、ゲート電極と別に備えられている。このような構造にすることで、フィンの幅を空乏層程度に保つことを必要せず、基板電位を変化させることでデバイスの特性を変化させる、基板バイアス効果によって消費電力を削減することが可能となる。

(もっと読む)

埋め込みガードリング及び耐放射線性分離構造並びにその製造方法

【課題】大量の商業マイクロエレクトロニクスメーカーがアクセスし易い最先端の基礎設備を使用して、高性能且つ費用対効果に優れた耐放射線性集積回路(RHICs)を提供する。

【解決手段】様々な形式の放射線エネルギーによって引き起こされる有害な影響を減少し、又は排除するために、従来の設計及びプロセスを使用する一方で特殊構造を含んで半導体デバイスを作成する。このような半導体デバイスは本願で開示された1台以上の寄生的な分離デバイス、及び/又は、埋め込みガードリング構造を含む。これら新規な構造に対応する設計、及び/又は、工程ステップの導入には、従来のCMOS製作工程との互換性がある。したがって、比較的低い費用で比較的簡単に実施することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

半導体装置

【課題】電界効果型トランジスタのLSI製造後にしきい電圧の制御が可能で、かつ、回路面積を増大させず、かつ信頼性に優れるという特徴を有する技術を提供する。

【解決手段】シリコン半導体支持基板1の上面に設けられた積層膜(3nm以上4nm以下の第1のシリコン酸化膜2/0.3nm以上2nm以下のシリコン窒化膜3/5nm以上10nm以下の第2のシリコン酸化膜4/3nm以上20nm以下の膜厚)を有するSOI層5と、上記構造に所定の間隔を介して互いに対向して設けられたソース・ドレイン拡散層6と、当該ソース拡散層とドレイン拡散層の間の上記半導体基板の表面上に形成されたゲート絶縁膜7と、上記ゲート絶縁膜の上に形成されたゲート電極8を具備してなる電界効果型半導体装置において、シリコン支持基板1から電圧を印加することにより、直接トンネル効果によって電荷をシリコン窒化膜3に一定時間保持してしきい電圧を調整する。

(もっと読む)

半導体装置および携帯電話機

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】RXスルートランジスタ群TH(RX)は、互いに直列に接続されたMISFETQ1〜Q5において、それぞれのMISFETのボディ領域と、隣接するMISFETのソース領域あるいはドレイン領域とを、それぞれ、ダイオード(整流素子)を介して接続する。そして、特に、nチャネル型MISFETの場合、MISFETのボディ領域から隣接するMISFETのソース領域あるいはドレイン領域へ向う向きが順方向となるようにダイオードを接続する。

(もっと読む)

カレントミラー回路、電流生成回路及び発光装置

【課題】負荷に供給する電流を精度よく出力する。

【解決手段】ゲート電極とドレイン電極が短絡されている第1トランジスタTr1と、第1トランジスタTr1のゲート電極に、ゲート電極が接続された第2トランジスタTr2と、を備えるカレントミラー回路10において、第1トランジスタTr1と第2トランジスタTr2は、絶縁膜12を介してゲート電極1の上部に設けられてチャネル領域が形成される半導体膜2と、半導体膜2上のチャネル領域を覆う領域に設けられる保護膜3と、半導体膜2のチャネル領域を挟む一対の端部に離間して設けられるとともに保護膜3の一部に重なって設けられソース電極6及びドレイン電極7とをそれぞれ有するとともに、少なくとも第2トランジスタTr2は、ソース電極6の保護膜3に対するチャネル長方向への重なり長がドレイン電極7の保護膜3に対する重なり長より長い構造を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】交流電圧で使用することができる半導体装置を提供する。

【解決手段】半導体基板11に形成された第1トランジスタT1と、半導体基板11上にBOX層12を介して形成された第2トランジスタT2と、を備え、第1トランジスタT1は、半導体基板11の表面に形成された第1ボディ領域11fと、この第1ボディ領域11fを挟むように形成された第1ソース領域11d及び第1ドレイン領域11eと、有し、第1ボディ領域11f上に第2トランジスタT2の第2ドレイン領域13cが配置され、第1ドレイン領域11e上に第2トランジスタT2の第2ボディ領域13aが配置され、第1ドレイン領域11eとBOX層12における第2ボディ領域13aとの間に接続層17が形成され、かつ第2ドレイン領域13cが第1トランジスタT1のゲート電極を兼ねた。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】単結晶半導体層のテーパー形状を有する端部の特性を良好にすることを課題とする。

【解決手段】加速されたイオンを単結晶半導体基板に照射することによって、単結晶半導体基板中に脆化領域を形成し、単結晶半導体基板とベース基板とを、絶縁膜を介して貼り合わせ、脆化領域において単結晶半導体基板を分離して、ベース基板上に絶縁膜を介して第1の単結晶半導体層を形成し、第1の単結晶半導体層に対してドライエッチングを行って、端部の形状がテーパー形状である第2の単結晶半導体層を形成し、第2の単結晶半導体層の端部に対して、ベース基板側の電位を接地電位としたエッチングを行う。

(もっと読む)

半導体装置、並びに、半導体装置の製造方法及び駆動方法

【課題】絶縁層上に形成された部分空乏型のトランジスターにおいて、ヒストリー効果を低減し、なおかつ高いON/OFF比、及び急峻なサブスレッショルド特性を実現する。

【解決手段】絶縁層上の半導体層に形成された第1導電型のソース領域、第1導電型のドレイン領域、及び、第2導電型のボディ領域と、第1ゲート絶縁膜と、第1ゲート電極と、を含む部分空乏型の第1トランジスターと、絶縁層上の半導体層に形成された第1ダイオードと、を具備し、第1ダイオードは、第1導電型の第1不純物領域と、第1不純物領域上に形成された第2導電型の第2不純物領域と、を含み、第1トランジスターのボディ領域は、第1ダイオードの第1不純物領域及び第2不純物領域に接続されている。

(もっと読む)

半導体装置

【課題】本実施形態は、ボディコンタクトの面積を相対的に縮小し信頼性を向上させた半導体装置を提供することを目的とする。

【解決手段】実施形態に係る半導体装置は、第1および第2のドレイン領域の間に設けられたソース領域を備える。第1のドレイン領域とソース領域との間には、第1のボディ領域が形成され、第2のドレイン領域とソース領域との間には、第2のボディ領域が形成されている。さらに、第1のボディ領域および第2のボディ領域の少なくとも一方に接続された複数のキャリアパス領域と、第1および第2のボディ領域から離間して設けられたコンタクト領域と、を備える。キャリアパス領域は、第1または第2のボディ領域とコンタクト領域との間を電気的に接続し、ソース領域は、第1および第2のボディ領域と、複数のキャリアパス領域と、コンタクト領域と、によって囲まれたことを特徴とする。

(もっと読む)

半導体装置及び駆動方法

【課題】絶縁層上に形成された部分空乏型のトランジスターにおいて、ヒストリー効果を低減し、なおかつ高いON/OFF比、及び急峻なサブスレッショルド特性を実現する。

【解決手段】絶縁層上の半導体層に形成された第1導電型のソース領域、第1導電型のドレイン領域、及び、第2導電型のボディ領域と、第1ゲート絶縁膜と、第1ゲート電極と、を含む部分空乏型の第1トランジスターと、絶縁層上の半導体層に形成された第2導電型のソース領域、第2導電型のドレイン領域、及び、第1導電型のボディ領域と、第2ゲート絶縁膜と、第2ゲート電極と、を含む第2トランジスターと、を具備し、第1トランジスターの第2導電型のボディ領域は、第2トランジスターの第2導電型のソース領域及び第2導電型のドレイン領域の内の一方に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造の縦型のMISFETの提供

【解決手段】Si基板1上に、一部に空孔4を有する絶縁膜2が設けられ、空孔4上及び絶縁膜2の一部上に横方向半導体層6が設けられ、半導体層6の側面の一部に導電膜3が接して設けられ、絶縁膜2により素子分離されている。半導体層6上の、空孔4直上部に縦方向半導体層7が設けられ、半導体層7の上部にドレイン領域(10,9)が設けられ、離間し、相対して下部にソース領域8が設けられ、ソース領域8は延在して、半導体層6全体に設けられている。半導体層7の全側面には、ゲート酸化膜11を介してゲート電極12が設けられ、ドレイン領域10、ゲート電極11及び導電膜3を介したソース領域8には、バリアメタル18を有する導電プラグ19を介してバリアメタル21を有する配線22が接続されている縦型のMISFET。

(もっと読む)

半導体装置の製造方法

【課題】 ソース領域側だけに不活性イオン注入領域が形成される非対称型SOI電界効果トランジスタを容易に実現する半導体装置の製造方法を提供する。

【解決手段】 イオン注入前にトランジスタが形成される半導体層のゲート電極について対称構造をなす2つの電極のいずれか一方をソース又はドレインとして指定する電極指定データを予め保持する設計工程と、電極指定データに応じてソース領域側だけのイオン注入を可能にするためのイオン注入用マスクを製作するマスク製作工程と、対称をなす2つの電極を有する半導体層表面にフォトレジストを塗布しイオン注入用マスクを用いて露光してフォトレジストの少なくともソース領域に対応する部分を除去するレジスト形成工程と、レジスト形成工程の実行後、イオン注入用マスクに対応して残されたフォトレジストを有する半導体層表面からイオンを注入する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】ソース/ドレイン領域と基板との間の容量の低下を防止でき、パンチスルー現象を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板上に第1絶縁膜を介してゲート電極を形成する工程と、前記ゲート電極の上面及び側面を覆う第2絶縁膜を形成する工程と、前記第2絶縁膜をマスクとして前記半導体基板の表面に溝部を形成する工程と、前記溝部の底面上に、該溝部の側壁の上部の露出を残す厚さで第3絶縁膜を形成する工程と、前記露出された溝部の側壁の上部を起点としたエピタキシャル成長により、前記第3絶縁膜上に前記半導体のエピタキシャル層を形成する工程と、前記エピタキシャル層に不純物を導入してソース/ドレイン領域を形成する工程と、を有することを特徴とする

(もっと読む)

半導体装置の製造方法

【課題】ボディー抵抗の低減化を図った部分分離ボディー固定SOI構造の半導体装置及びその製造方法を得る。

【解決手段】NMOSトランジスタのソース・ドレイン領域形成時において、N+ブロックレジスト51におけるN+ブロック領域41のゲート方向延長領域41aによって、ゲート方向延長領域41a下のウェル領域11には、N型の不純物が注入されることを回避する。ゲート電極9の長手方向延長線上においてN型の不純物が注入される恐れのあるウェル領域11である高抵抗形成領域を、従来の高抵抗形成領域A1より狭い高抵抗形成領域A2とすることができる。

(もっと読む)

1 - 20 / 183

[ Back to top ]