Fターム[5F110AA16]の内容

Fターム[5F110AA16]に分類される特許

101 - 120 / 2,903

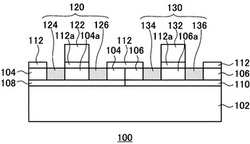

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層104に形成された第1チャネル型の第1MISFET120の第1ソース124および第1ドレイン126が、第1半導体結晶層104を構成する原子と、ニッケル原子との化合物、または、コバルト原子との化合物、またはニッケル原子とコバルト原子との化合物からなり、第2半導体結晶層106に形成された第2チャネル型の第2MISFET130の第2ソース134および第2ドレイン136が、第2半導体結晶層106を構成する原子と、ニッケル原子との化合物、または、コバルト原子との化合物、または、ニッケル原子とコバルト原子との化合物からなる。

(もっと読む)

薄膜トランジスタ及びそれを利用した圧力センサー

【課題】本発明は、薄膜トランジスタ及びそれを利用した圧力センサーに関する。

ものである。

【解決手段】本発明の薄膜トランジスタは、ソース電極と、ドレイン電極と、半導体層と、ゲート電極と、絶縁層と、を含む。前記ソース電極は、前記ドレイン電極と間隔をあけて設置される。前記半導体層は、前記ソース電極及び前記ドレイン電極にそれぞれ電気的に接続される。前記半導体層は一つのチャネルを有し、該チャネルは前記ソース電極及び前記ドレイン電極の間に位置する。前記ゲート電極は、前記絶縁層により、前記ソース電極、前記ドレイン電極及び前記半導体層と絶縁状態で設置される。前記絶縁層は、弾性率が0.1MPa〜10MPaである高分子材料からなる。

(もっと読む)

電子デバイス及び半導体装置の製造方法

【課題】簡素な装置で、短時間にて形成することができ、しかも、電極と能動層との間のコンタクト抵抗の低減を確実に図ることができる電荷注入層を備えた電子デバイスを提供する。

【解決手段】電子デバイスは、第1電極15、第1電極と離間して設けられた第2電極15、及び、第1電極15の上から第2電極15の上に亙り設けられた、有機半導体材料から成る能動層14を少なくとも備えており、第1電極15と能動層14との間、及び、第2電極15と能動層14との間には、電荷注入層16が形成されており、電荷注入層16は、酸化されることで電気伝導度の値が増加した有機材料から成る。

(もっと読む)

半導体装置の作製方法

【課題】 大面積のガラス基板上に薄膜からなる集積回路を形成し、他の基体に転写して分断を行い、接触、好ましくは非接触でデータの受信または送信が可能な微細なデバイスを大量に効率よく作製する方法を提供することを課題とする。特に薄膜からなる集積回路は、非常に薄いため移動時に飛んでしまう恐れがあり、取り扱いが難しかった。

【解決手段】 本発明は、剥離層に達する多数の穴または多数の溝を設け、穴(または溝)およびデバイス部に重ならない領域にパターン形状を有する材料体を設けた後、ハロゲン化フッ素を含む気体又は液体を導入して、前記剥離層を選択的に除去する。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

薄膜トランジスタ及びそれを利用した圧力センサー

【課題】本発明は、薄膜トランジスタ及びそれを利用した圧力センサーに関する。

ものである。

【解決手段】本発明の薄膜トランジスタは、ソース電極と、ドレイン電極と、半導体層と、ゲート電極と、絶縁層と、を含む。前記ソース電極は、前記ドレイン電極と間隔をあけて設置される。前記半導体層は、前記ソース電極及び前記ドレイン電極にそれぞれ電気的に接続される。前記半導体層は、弾性率が0.1MPa〜10MPaである高分子複合材料層である。前記高分子複合材料層は、高分子基材及び該高分子基材に分散された複数のカーボンナノチューブからなる。前記ゲート電極は、前記絶縁層により、前記半導体層、前記ソース電極及び前記ドレイン電極と絶縁状態で設置される。

(もっと読む)

半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供する

ことを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウ

ム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて

、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化

物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以

下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有

し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でス

パッタリングを行う。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】酸化物半導体を用いた薄膜トランジスタにおいては、酸素原子等を酸化物半導体中に十分かつ均一に拡散させることが困難である。

【解決手段】半導体装置であって、ゲート電極と、前記ゲート電極の一方の表面を覆うように配置されたゲート絶縁膜と、前記ゲート絶縁膜に重ねて配置された酸化物半導体と、前記酸化物半導体に重ねて配置されたソース電極及びドレイン電極と、前記ソース電極及びドレイン電極と、前記ゲート絶縁膜層との間に、前記酸化物半導体に接するように配置された酸素原子含有膜と、を有する。

(もっと読む)

半導体装置及び発光装置

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成す

る。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用チャネル保護型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。半導体装置に設けられる該薄膜トランジスタは多階調マスクによって形成されたレジストマスクを用いて作製する。

(もっと読む)

半導体装置

【課題】導体半導体接合を用いて、優れた特性を示す、あるいは、作製の簡単な、あるいは、より集積度の高い電界効果トランジスタを提供する。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

検波器及び受信機

【課題】低電圧、低電流、或いは低電力といった条件下でも使用することが可能な検波器を提供する。

【解決手段】検波器は、信号入力端子に接続された第1導電型の第1の半導体領域と、信号出力端子に接続された第2導電型の第2の半導体領域であって、第1の半導体領域に接して位置する第2の半導体領域と、交流的に接地された第1導電型の第3の半導体領域であって、第1の半導体領域から離間し且つ第2の半導体領域に接して位置する第3の半導体領域と、一端が第2の半導体領域に接続され、他端が交流的に接地された第1の抵抗素子と、を含む。

(もっと読む)

絶縁膜形成用印刷インキ組成物、該絶縁膜形成用印刷インキ組成物から形成された絶縁膜。

【課題】 良好な絶縁特性を有する絶縁膜の形成に使用される高精細印刷インキ組成物および該印刷インキ組成物から形成された絶縁膜を提供すること。

【解決手段】 少なくとも不揮発性成分と溶剤を含有する絶縁膜形成用印刷インキ組成物であって、反転オフセット印刷、剥離オフセット印刷、マイクロコンタクト印刷のいずれかに用いられ、ポリシロキサンが不揮発性成分の75重量%以上であることを特徴とする絶縁膜形成用印刷インキ組成物。

(もっと読む)

薄膜トランジスタの製造方法およびロール状薄膜トランジスタ

【課題】本発明は、低温かつ安価な製造工程により作製可能であり、トランジスタ特性に優れる薄膜トランジスタおよびその製造方法を提供することを主目的とするものである。

【解決手段】本発明は、基板と、ゲート電極と、ゲート絶縁層と、酸化物半導体層と、ソース電極と、ドレイン電極と、を有する薄膜トランジスタの製造方法であって、酸化性ガスを含む雰囲気で酸化物半導体層を形成する酸化物半導体層形成工程と、上記酸化物半導体層形成工程後、上記酸化物半導体層の少なくともチャネル領域に酸素欠損を付与して上記チャネル領域のキャリア濃度を制御するキャリア濃度制御工程と、を有することを特徴とする薄膜トランジスタの製造方法を提供する。

(もっと読む)

電気光学装置の製造方法

【課題】層間絶縁膜のコンタクトホールの内部にコンタクト用導電膜および埋め込み膜を設けた場合でも、コンタクトホールの外部で画素電極とコンタクト用導電膜とを確実に導通させることができる電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置100を製造するにあたって、層間絶縁膜45上にコンタクトホール45aの底部45eおよび内壁45fに重なるコンタクト用導電膜90をITO膜により形成した後、コンタクトホール45aの内部を埋める埋め込み膜48をシリコン酸化膜により形成し、その後、埋め込み膜48に対して反応性イオンエッチングを行い、コンタクト用導電膜90を露出させる。また、コンタクトホール45aの内部には埋め込み膜48を残す。その際、埋め込み膜48とコンタクト用導電膜90とのエッチング選択比を利用して埋め込み膜48を選択的に除去してコンタクト用導電膜90を露出させる。

(もっと読む)

酸化物薄膜トランジスタ及びその製造方法

【課題】短チャネルを実現し、薄膜トランジスタの性能を向上させる酸化物薄膜トランジスタ及びその製造方法を提供する。

【解決手段】本発明による酸化物薄膜トランジスタの製造方法は、基板110上に第1導電膜からなるゲート電極121及びゲートライン116を形成する段階と、ゲート電極121及びゲートライン116が形成された基板110上にゲート絶縁膜115aを形成する段階と、ハーフトーン露光を用いて、ゲート絶縁膜115aが形成されたゲート電極121の上部に第2導電膜からなるソース電極122、第1ドレイン電極123、及び第1データライン117を形成し、かつ第1ドレイン電極123の延長部及び第1データライン117上に第3導電膜からなる第2ドレイン電極123’及び第2データライン117’を形成する段階と、ソース電極122及び第1ドレイン電極123上に酸化物半導体からなるアクティブ層124を形成する段階とを含む。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

表示基板の製造方法

【課題】過剰なエッチングによる不良を減少させるための表示基板の製造方法を提供する。

【解決手段】互いに交差する信号ラインによって定義された複数の単位画素Pを有する表示領域DAと表示領域DAを取り囲む周辺領域PAを含む基板110上にフォトレジスト膜を塗布する段階と、フォトレジスト膜をパターニングして、表示領域DAで信号ラインとオーバーラップされる第1パターン部P1と、周辺領域PAで信号ラインと重畳されない領域に形成された複数のダミー開口部DOを含む第2パターン部P2とを形成する段階と、第1パターン部P1及び第2パターン部P2が形成された基板110上に透明電極層117a、117bを形成する段階と、ストリップ溶液で第1パターン部P1、第2パターン部P2、及び第1及び第2パターン部上に形成された透明電極層117a、117bを除去して、単位画素Pに対応する画素電極PE及びダミー開口部DOに対応するダミー電極DMを形成する段階と、を含む。

(もっと読む)

薄膜トランジスタ及びアレイ基板の製造方法

【課題】従来のボトムゲートのトップコンタクト構造の薄膜トランジスタを製造する時、使用されるマスクの数が多いので、該薄膜トランジスタの製造コストが高くなる。

【解決手段】ソース・ドレイン電極及びパターニングされた活性層を製造するためのマスクに、チャンネル領域に対応する幅が露光装置の分解能より小さいスリットを形成し、露光量を大きくすることで、ソース・ドレイン電極を通常に形成でき、さらに該マスクを用い、露光量を小さくすることで、所望形状の活性層を形成できる。

(もっと読む)

101 - 120 / 2,903

[ Back to top ]