Fターム[5F110AA16]の内容

Fターム[5F110AA16]に分類される特許

141 - 160 / 2,903

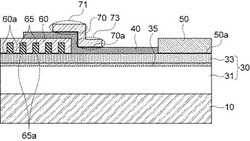

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成し、ドレイン電極と該ソース電極との間にフローティングガードリングを設けることによって、ノーマリ−オフで動作する半導体素子を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間で窒化物半導体層30にショットキー接合されたフローティングガードリング75と、ドレイン電極50とソース電極60との間及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、誘電層40上に形成され、一部が、誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

記憶素子および信号処理回路

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路を提供する。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、アモルファスシリコン、ポリシリコン、微結晶シリコン、あるいは酸化物半導体等の化合物半導体をチャネル形成領域に含み、そのチャネル長が最小加工線幅の10倍以上あるいは、1μm以上であるトランジスタを用いる。上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

絶縁膜の製造方法

【課題】質量密度の高い絶縁膜の製造方法を提案すること。

【解決手段】絶縁膜の製造方法は、基板の上に絶縁膜を形成するステップと、その絶縁膜を処理するステップとを備えている。絶縁膜は、SiとOとを含んでおり、たとえばSiO2膜である。第2のステップでは、絶縁膜の温度を551℃以上574℃以下として、活性状態の希ガスと活性状態の酸素とを絶縁膜に供給する。

(もっと読む)

ナノワイヤの配列方法、及び分離方法

【課題】所望の長さのナノワイヤを、所望の向き、位置に配列させる方法。

【解決手段】ナノワイヤの配列方法であって、二つの電極を有する基板上に、両末端が互いに異なる二つの極性であるナノワイヤを静置、第1電極に第1極性の電圧を印加し、その反対の第2極性の片末端を第1電極上に固定、第1電極に第1極性の電圧を印加した状態で、第1電極から第2電極に流体を流す、第1電極の電圧を自然電位に設定後、第2極性の電圧を第2電極に印加し、第1極性の片末端を第2電極に固定、第2電極に第2極性の電圧を印加した状態で、第2電極から第1電極に流体を流す、第2電極の電圧を自然電位に設定後、第1電極に第1極性の電圧を印加し、第2極性の片末端を第1電極上に固定、第1電極に第1極性の電圧を印加した状態で、第2電極から第1電極に流体を流す、第1電極に第1極性の電圧を印加した状態で、第1電極から第2電極に流体を流す、を順次行う。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】低温成膜可能な酸化物で半導体膜を形成した逆スタガ型薄膜トランジスタであって、半導体膜上に形成した保護膜の紫外線等に対する耐光性と耐環境安定性を向上させてなる薄膜トランジスタ及びその製造方法を提供する。

【解決手段】基板1上にパターン形成されたゲート電極2と、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3上にパターン形成された酸化物半導体膜4と、酸化物半導体膜4上にパターン形成されたソース電極6S及びドレイン電極6Dと、ソース電極6S及びドレイン電極6D間に露出する酸化物半導体膜4を少なくとも覆う保護膜7とを有するボトムゲートトップコンタクト構造の薄膜トランジスタ10であって、保護膜7を、酸化物半導体材料で形成する。このとき、酸化物半導体膜4及び保護膜7が、InMZnO(MはGa,Al,Feのうち少なくとも1種)を含むアモルファス酸化物である酸化物半導体材料からなることが好ましい。

(もっと読む)

デバイスの製造方法、表示装置の製造方法、表示装置および電子機器

【課題】簡易な工程で製造歩留まりを向上させることが可能なデバイスの製造方法および表示装置の製造方法等を提供する。

【解決手段】基板11上にデバイス(TFT層12)を形成する工程は、薄膜を形成する工程(工程S11)と、薄膜上にフォトレジスト膜を形成する工程(工程S12)と、露光マスクM1を用いてフォトレジスト膜に対して露光を行う露光工程(工程S13)と、露光がなされたフォトレジスト膜をエッチングする工程(工程S15)とを含んでいる。露光工程では、フォトレジスト膜に対する露光を複数回連続して行う(工程S131,S132)。これにより、製造工程の増加を抑えつつ、異物の混入等に起因した薄膜パターンにおけるエッチング不良を低減することができる。

(もっと読む)

コプレナ型の酸化物半導体素子とその製造方法

【課題】折り曲げ耐性が向上したコプレナ型の酸化物半導体を提供し、また、コンタクトホールを精巧に形成するコプレナ型の酸化物半導体の製造方法を提供する。

【解決手段】絶縁性を有する基板と、前記基板上に配置され、チャネル領域及び電極接続領域を有する酸化物半導体層と、前記酸化物半導体層上に配置され、コンタクトホールを有するゲート絶縁層と、前記ゲート絶縁層上に配置されたソース電極、ドレイン電極、及びゲート電極と、を有するコプレナ型の酸化物半導体素子であって、前記ゲート絶縁層は、架橋ポリマーで形成されていることを特徴とするコプレナ型の酸化物半導体素子とその製造方法。

(もっと読む)

有機半導体素子の製造方法および有機半導体素子

【課題】有機半導体層の移動度を低下させることなく、容易に有機半導体層をパターニングした有機半導体素子を得ることができる有機半導体素子の製造方法を提供する。

【解決手段】液晶性有機半導体材料を配向させる配向層1上にソース電極2およびドレイン電極3を形成するソース電極およびドレイン電極形成工程と、上記ソース電極および上記ドレイン電極を覆うように上記配向層上に、液晶性有機半導体材料を有する有機半導体層4を形成する有機半導体層形成工程と、上記有機半導体層上の少なくとも上記ソース電極および上記ドレイン電極間のチャネル領域C上に、誘電体層5を形成する誘電体層形成工程と、上記誘電体層が形成された上記有機半導体層を上記液晶性有機半導体材料の液晶相温度でアニール処理するアニール処理工程と、を有することを特徴とする有機半導体素子の製造方法。

(もっと読む)

有機半導体素子の製造方法および有機半導体素子

【課題】簡便な工程で、有機半導体層の移動度を低下させることなくパターニングした有機半導体素子を得ることができる有機半導体素子の製造方法を提供する。

【解決手段】ソース電極1およびドレイン電極2を覆うように有機半導体層3を形成する有機半導体層形成工程と、上記有機半導体層上の少なくとも上記ソース電極1および上記ドレイン電極2間のチャネル領域C上に、第一誘電体層4を形成する第一誘電体層形成工程と、上記第一誘電体層を覆うように上記有機半導体層上に、第二誘電体層5を形成する第二誘電体層形成工程と、を有し、第二誘電体層5は、第一誘電体層4の周囲で有機半導体層3と接触する接触部を有し、接触部Xにおける有機半導体層3および第二誘電体層5の界面に、有機半導体層と第二誘電体層とが混ざり合った混合層6を形成することを特徴とする有機半導体素子の製造方法。

(もっと読む)

有機トランジスタの製造方法

【課題】良好な特性を有する有機トランジスタを、インクジェット法により製造する。

【解決手段】有機半導体層7は、インクジェット法によって、有機半導体材料を溶媒に溶解した有機半導体溶液を塗布して形成され、塗布された有機半導体溶液の縁部71が、ソース電極5とドレイン電極6間に配置されるように、ソース電極5とドレイン電極6間のちょうど中間位置よりずらした位置に、塗布領域の中心が位置するように、有機半導体溶液を塗布することを特徴とする。また、ソース電極5が配置されている位置、又はドレイン電極6が配置されている真上に、塗布領域の中心が位置するように、有機半導体溶液を塗布する。

(もっと読む)

ナノワイヤの配列方法、及び分離方法

【課題】所定の長さのナノワイヤを所定の向きに、所定の位置に配列させる方法、並びに所定の長さのナノワイヤを分離抽出する方法を提供する。

【解決手段】基板上の所定の位置にナノワイヤを配置するためのナノワイヤの配列方法であって、前記ナノワイヤの両端を固定するための、所定の距離を離間させた対となる固定化部位を設けた基板を作製する工程と、両末端に前記基板上の固定化部位と特異的な結合を形成するための結合部位を有するナノワイヤを作製する工程と、前記ナノワイヤを含有する液を前記基板上に分散させ、前記ナノワイヤの結合部位を前記基板上の固定化部位に結合させる工程と、前記対となる固定化部位の相対する方向に対して略垂直に流体を流す工程とを順次行うことを特徴とする。

(もっと読む)

有機半導体素子の製造方法

【課題】有機半導体層のパターン精度が良好であり、トランジスタ特性に優れた有機半導体素子を容易に製造することが可能な製造方法を提供すること。

【解決手段】液晶性有機半導体材料を配向させる配向層1上にソース電極2およびドレイン電極3を形成する電極形成工程と、ソースおよびドレイン電極を覆うように配向層1上に、液晶性有機半導体材料を有する有機半導体層4を形成する工程と、基板5と上記基板上にパターン状に形成された親液部6および撥液部7を有する有機半導体層転写基板8を用い、撥液部がソースおよびドレイン電極間のチャネル領域C上に配置されるように、有機半導体層4上に積層して、親液部6上に、その液晶相温度で熱転写する工程と、液晶相温度よりも低い温度で、配向層1から剥離することにより、親液部6上に熱転写された有機半導体層4を配向層1から除去する工程と、を有することを特徴とする有機半導体素子の製造方法。

(もっと読む)

有機半導体素子の製造方法

【課題】高い精度で効率良く有機半導体をパターニングすることができる有機半導体素子の製造方法を提供する。

【解決手段】有機半導体層形成用溶液に対して撥液性がある撥液部2を有する基体1と、前記基体1上に形成されたソース電極3及びドレイン電極4と、前記基体1の撥液部2の一部上に形成された遮蔽層5とを有し、前記ソース電極3及び前記ドレイン電極4に金もしくは/及び白金、又は酸化還元電位が銀以下の金属が含まれている有機半導体素子用基板6上に紫外線又は含酸素プラズマを前記有機半導体素子用基板6に照射して、前記有機半導体層形成用溶液に対して親液性がある親液部7に変性する有機半導体素子用基板6の形成工程と、有機半導体層8の形成工程と、前記ソース電極3及び前記ドレイン電極4に酸化還元電位が銀以下の金属が含まれている場合は還元工程と、を有する有機半導体素子の製造方法。

(もっと読む)

薄膜トランジスタ構造および表示装置

【課題】酸化物半導体上の保護膜形成時などにおける酸化物半導体表面の欠陥(ダメージ)に伴うTFT特性の劣化を、新たな処理工程を設けることなく簡易に且つ確実に低減することができ、製造コストの低減化、生産性および歩留まりの向上を実現できる技術を提供する。

【解決手段】本発明の薄膜トランジスタ構造は、薄膜トランジスタの半導体層に用いられ、In、Zn、およびSnの金属元素を含むIn−Zn−Sn酸化物と;前記In−Zn−Sn酸化物の上部に表面層と、を有している。保護膜形成前の表面層をX線光電子分光法(XPS)で検出し、酸素の1s電子(O1s)に帰属するピークエネルギーの強度をピーク分離によって求めたとき、下記式(1)の関係を満足する。

B/(A+B)≧0.33 ・・・ (1)

Aは、金属元素と結合するO1sのピークエネルギーの強度、

Bは、Cおよび/またはHの非金属元素と結合するO1sのピークエネルギーの

強度を意味する。

(もっと読む)

有機半導体素子の製造方法

【課題】高い精度で効率良くパターニングすることができる有機半導体素子の製造方法を提供する。

【解決手段】有機半導体層形成用溶液に対して撥液性がある撥液部2を有する基体1を準備する第1工程、前記基体1の撥液部2上に遮蔽層5を形成する第2工程、前記基体1の撥液部2の一部を前記有機半導体層形成用溶液に対して親液性がある親液部7に変性する第3工程、及び、前記第1工程、前記第2工程、または前記第3工程の後に行い、前記基体1上にソース電極3及びドレイン電極4を形成する第4工程を有する有機半導体素子用基板6の形成工程と、有機半導体層8を親液部7上に形成する有機半導体層8の形成工程と、を有する有機半導体素子の製造方法。

(もっと読む)

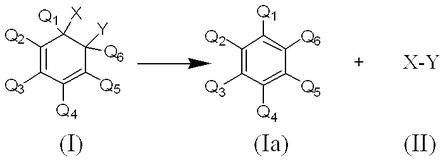

芳香環を有するπ電子共役系化合物を含有する膜状体の製法、及び該π電子共役系化合物の製法

【課題】低いエネルギー付与でπ電子共役化合物を得る製造方法、及びこの技術を利用し、難溶性π電子共役系化合物の連続した薄膜の効率的な製造方法を提供する。更に該薄膜の有機電子デバイスへ応用する。

【解決手段】π電子共役系化合物前駆体(I)を含む溶媒の塗工液を基材に塗布して形成された塗工膜より、式(II)で示される脱離性置換基を脱離させ(Ia)で示されるπ電子共役系化合物を含有する膜状体を生成することを特徴とする膜状体の製造方法。

[式(I)、(Ia)、(II)中、XおよびYは水素原子もしくは脱離性置換基を表す。Q2乃至Q5はそれぞれ独立して水素原子、ハロゲン原子または、1価の有機基であり、Q1とQ6は水素原子、ハロゲン原子または、前記脱離性置換基以外の一価の有機基である。Q1乃至Q6は隣り合った基同士でそれぞれ結合して環を形成していてもよい。]

(もっと読む)

141 - 160 / 2,903

[ Back to top ]