Fターム[5F110AA16]の内容

Fターム[5F110AA16]に分類される特許

201 - 220 / 2,903

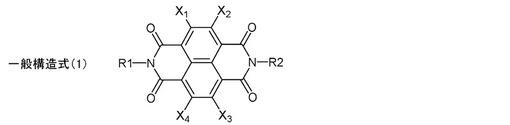

有機半導体薄膜用材料、該材料を用いた有機半導体薄膜の形成方法および有機薄膜トランジスタ

【課題】印刷製膜法により形成された有機半導体薄膜を大面積にわたり均一に作成することが容易であり、高い電子移動度および高いオン/オフ値を有するとともに、微粒子を用いた分散液塗布法により有機半導体薄膜を形成することのできる有機半導体薄膜用材料、有機半導体薄膜および有機トランジスタを提供すること。

【解決手段】n型有機半導体素子として使用可能な有機半導体薄膜用材料であって、80℃〜250℃の温度領域に相転移温度を有し、下記一般構造式(1)で表されるナフタレンテトラカルボキシジイミド誘導体を含むことを特徴とする有機半導体薄膜用材料、有機半導体薄膜および有機トランジスタ。 (もっと読む)

(もっと読む)

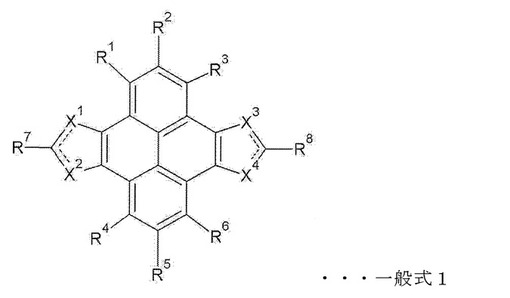

有機半導体化合物及び有機半導体高分子並びにこれを含むトランジスタ及び電子素子

【課題】有機半導体化合物及びこれを重合して得られる有機半導体高分子を提供する。

【解決手段】下記の一般式1で表わされる有機半導体化合物および有機半導体高分子。 (もっと読む)

(もっと読む)

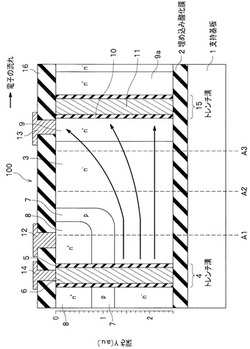

半導体装置

【課題】オン抵抗が低く、かつ、容易に素子分離もできる半導体装置を提供する。

【解決手段】第1絶縁膜2の上の第1導電型の第1半導体層3の表面を含む上部に設けられた第2導電型の第1半導体領域7と、第1半導体領域7の上部に設けられた第1導電型の第2半導体領域8と、側面が第1半導体層3と第1半導体領域7と第2半導体領域8に接する第1トレンチ4と、第1トレンチ4の側面に沿って設けられたゲート絶縁膜5と、第1トレンチ4内に埋め込まれたゲート電極6と、第1半導体領域7と第1トレンチ4から離れて第1半導体層3の上部に設けられた第1導電型の第3半導体領域9と、側面が第3半導体領域9に接し第3半導体領域9に対して第1半導体領域7の反対側に配置された第2トレンチ15と、第2トレンチ15の側面に沿って設けられた素子分離絶縁膜10と、第2トレンチ15内に埋め込まれたポリシリコン埋め込み領域11とを有する。

(もっと読む)

アクセプター性の基を有する化合物、これを用いた有機薄膜及び有機薄膜素子

【課題】本発明の目的は、電子輸送性に優れる有機n型半導体として利用可能な化合物を提供することにある。本発明の目的はまた、係る化合物を含む有機薄膜、及びこの有機薄膜を備える有機薄膜素子を提供することにある。

【解決手段】かご状化合物又は脂肪族炭化水素化合物から誘導される4価以上の基であるコア部と、該コア部に結合した4以上の側鎖基と、を備え、側鎖基のうち2以上がアクセプター性の基を有する、化合物。

(もっと読む)

ホール形成方法、並びに該方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステム

【課題】プロセス再現性が高く、微細なホールを効率よく低コストで形成することができるホール形成方法、並びに、該ホール形成方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムの提供。

【解決手段】基材上にピラー形成液を付与してピラーを形成するピラー形成工程と、前記ピラーが形成された基材上に絶縁膜形成材料を付与して絶縁膜を形成する絶縁膜形成工程と、前記ピラーを除去して前記絶縁膜に開口部を形成するピラー除去工程と、前記開口部が形成された絶縁膜を熱処理する熱処理工程とを含むホール形成方法である。

(もっと読む)

表示装置及び電子機器

【課題】アクティブマトリクス型基板において、薄膜トランジスタと、その端子接続部を

同時に作り込み、少ないマスク数で歩留まりの良い表示装置を提供する。

【解決手段】画素部および外部入力端子を有する表示装置であって、画素部は、ゲート電

極と、半導体膜と、ゲート電極上に形成された絶縁膜、および絶縁膜上に半導体膜と電気

的に接続された電極を有するTFTを有し、外部入力端子は、ゲート電極と同じ層に形成

された第1の配線と、電極と同じ層に形成され、絶縁膜に形成されたコンタクトホールを

介し第1の配線と接続された第2の配線と、第2の配線に接続され、第2の配線上に形成

された透明導電膜と、第2の配線と透明導電膜が接続している位置で透明導電膜と電気的

に接続するフレキシブルプリント配線板を有する表示装置。

(もっと読む)

半導体装置の作製方法

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成する。

(もっと読む)

ジチオケトピロロピロール系ポリマー

【課題】高いフィールド効果移動性、空気安定性、及び良好な溶解性を示す半導体ポリマーを提供すること。

【解決手段】ピロロ[3,4−C]ピロールー2,5−ジチオンを必須単位とし、該化合物の3−位及び6−位を結合手として繰り返し単位を構成し、エテニル、エチニル、アリール、置換アリール、ヘテロアリール、置換ヘテロアリール等を共重合成分として含むポリマー。

(もっと読む)

半導体装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安

価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピン

グ法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時

に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300

℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶

質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

同時両極性電界効果型トランジスタ及びその製造方法

【課題】単一金属酸化物半導体材料をチャネル層として使用時に極性をp型伝導又はn型伝導に変更できる同時両極性電界効果型トランジスタを実現し、さらに、該同時両極性TFTを用いたCMOS構造のトランジスタを提供する。

【解決手段】基板上に設けたチャネル層と、前記チャネル層上又は下にゲート絶縁膜を介して設けられて前記チャネル層のキャリア濃度を制御するゲート電極を有する電界効果型トランジスタにおいて、前記チャネル層材料は、酸化第一スズ(SnO)薄膜であり、前記チャネル層とゲート絶縁膜との界面の欠陥準位密度が5×1014cm−2eV−1以下であり、前記チャネル層は、電子(n型)及び正孔(p型)伝導性の両方の動作が可能な同時両極性を有することを特徴とする同時両極性電界効果型トランジスタ。

(もっと読む)

複合酸化物焼結体及びそれからなるスパッタリングターゲット

【課題】TFT特性の均一性、TFT特性の再現性及びTFTの歩留りが良好なTFTパネルが得られる複合酸化物焼結体、及びそれからなるスパッタリングターゲットを提供すること。

【解決手段】In、Zn及びSnを含み、焼結体密度が相対密度で90%以上であり、平均結晶粒径が10μm以下であり、バルク抵抗が30mΩcm以下であり、直径10μm以上の酸化スズの凝集粒子数が、1.00mm2あたり2.5個以下である複合酸化物焼結体。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置(薄膜トランジスタ)を製造する。

【解決手段】本発明は、(a)基板SUBの上方に、第1金属酸化物を含有する半導体からなる導電層を形成する工程と、(b)導電層上に第2金属酸化物を含有する半導体からなる犠牲層SLを形成する工程と、(c)導電層と犠牲層SLとの積層膜を加工する工程と、(d)上記(c)工程の後、犠牲層SL上に、金属膜を形成する工程と、(e)上記(d)工程の後、上記金属膜の第1領域をドライエッチングにより除去する工程と、(f)上記(e)工程の後、上記第1領域の上記犠牲層SLをウェットエッチングにより除去する工程と、を有し、上記(c)工程と、上記(f)工程との間に、(g)導電層に熱処理を施し、導電層を結晶化し、導電層CLcとする工程を有する。かかる工程によれば、ドライエッチングにより生じた犠牲層SLのダメージ領域DRを除去できる。

(もっと読む)

基板洗浄装置、基板洗浄方法、表示装置の製造装置及び表示装置の製造方法

【課題】洗浄工程数を減らし、さらに、基板に対する汚染粒子の再付着を防止する。

【解決手段】基板洗浄装置1は、基板Wを搬送する搬送部2と、その搬送部2により搬送される基板Wの被洗浄面Sに、酸化膜除去可能な液体中に酸化性ガスを溶存状態および微小気泡状態で有する洗浄液を供給する供給ノズル3とを備え、その供給ノズル3は、被洗浄面S上に到達した微小気泡がサイズ変化を抑えつつ基板Wの外縁まで移動する流速で洗浄液を供給する。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、少ない工程で多層配線化を実現し、小面積で高機能な機能回路を有する配線基板及び半導体装置を提供する。またこのような高機能な機能回路を表示装置と同一基板上に一体形成した半導体装置を提供することを課題とする。

【解決手段】本発明は、絶縁表面を有する基板上に、第1の配線と、第2の配線と、第3の配線と、第1の層間絶縁膜と第2の層間絶縁膜と、第1のコンタクトホールと第2のコンタクトホールを有し、前記第2の配線の幅を前記第1の配線の幅より広いか、あるいは前記第3の配線の幅を前記第1の配線の幅もしくは前記第2の配線の幅より広く、且つ前記第2のコンタクトホールの直径を前記第1のコンタクトホールの直径より大きく形成することを特徴とする。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の作製工程において、フォトリソグラフィ工程数を削減する。

【解決手段】トランジスタの、ゲート電極となる導電膜、ゲート絶縁膜となる絶縁膜、チャネル領域が形成される半導体膜およびチャネル保護膜となる絶縁膜を連続で形成し、多階調マスクであるフォトマスクによって露光し現像したレジストマスクを用いて、(1)レジストマスクのない領域において、チャネル保護膜となる絶縁膜、チャネル領域が形成される半導体膜、ゲート絶縁膜となる絶縁膜およびゲート電極となる導電膜を連続してエッチングし、(2)レジストマスクをアッシングなどによって後退させ、レジストマスクを残膜厚が小さい領域のみを除去することで、チャネル保護膜となる絶縁膜の一部を露出させ、(3)露出したチャネル保護膜となる絶縁膜の一部をエッチングし、一対の開口部を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート部におけるリーク電流が低減できる反面、プロセス上の制約があるため製造が困難で、ゲートリーク電流を安定して低減させることが困難だった。

【解決手段】基板と、前記基板上に形成され且つ二次元キャリアガスを有する半導体機能層と、前記半導体機能層上において互いに離間して形成される第1及び第2の主電極と、前記半導体機能層上における前記第1及び第2の主電極間に形成される制御電極と、前記半導体機能層と前記制御電極との間に形成される金属酸化膜と、を備え、

前記金属酸化膜と前記半導体機能層との接合界面における結晶格子は不連続であることを特徴とする半導体装置。

(もっと読む)

プリント不揮発性メモリ

【課題】低コストで高スループットなプリント技術を使用した不揮発性メモリセルを提供する。

【解決手段】同一水平レベルにおいて所定の距離で離間している第1及び第2の半導体アイランドであって、第1の半導体アイランド2が制御ゲートを構成し、第2の半導体アイランド3がソース端子及びドレイン端子を構成する、当該第1及び第2の半導体アイランドと、第1の半導体アイランド2の少なくとも一部の上のゲート誘電体層4と、第2半導体アイランドの少なくとも一部の上のトンネリング誘電体層5と、ゲート誘電体層4とトンネリング誘電体層5の少なくとも一部の上のフローティングゲート7と、制御ゲート2並びにソース端子及びドレイン端子に電気的に接触する金属層と、を備える。一つの効果的な実施形態では、不揮発性メモリセルを、「全プリント」加工技術を使用して製造することができる。

(もっと読む)

複合酸化物膜形成用の塗布液、並びに当該塗布液を使用した複合酸化物膜の製造方法及び電界効果トランジスタの製造方法

【課題】より簡便な、かつ高温の焼成を必要としない条件で、基板の所望の位置に複合酸化物の薄膜を形成させることのできる塗布液及びそれを使用した方法を提供すること。

【解決手段】インジウム(In)のキレート化合物(I)、亜鉛(Zn)のキレート化合物又は酢酸塩(Z)、及び有機溶媒(A)を含む複合酸化物膜形成用の塗布液を塗布して基材の表面に塗膜を形成し、次いでこの塗膜を焼成することにより複合酸化物膜に転換させる。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタの作製に用いるフォトリソグラフィ工程を従来よりも少なくし、且つ、信頼性の高い半導体装置を提供する。

【解決手段】第1の基板上に酸化物半導体層を有するトランジスタを含む回路と、当該第1の基板とシール材で固定された第2の基板とを有し、当該シール材、当該第1の基板、及び当該第2の基板で囲まれる閉空間は、減圧状態、或いは乾燥空気を充填する半導体装置に関する。当該シール材は、少なくとも前記トランジスタを囲み、閉じられたパターン形状を有する。また当該回路は、酸化物半導体層を有するトランジスタを含む駆動回路である。

(もっと読む)

薄膜トランジスターの製造方法

【課題】例えば製造工程数の増加を招くことなく、複数の半導体層に水素化処理を確実に行う。

【解決手段】薄膜トランジスターの製造方法は、基板(10)上に、複数の半導体層(110)を同一層として形成する工程と、複数の半導体層を覆うようにシリコン酸化膜(130)を形成する工程と、シリコン酸化膜上に複数の半導体層を覆うようにシリコン窒化膜(140)を形成する工程と、シリコン窒化膜上に複数の半導体層を覆うように導電膜(121)を形成する工程と、導電膜及びシリコン窒化膜をエッチングにより一括でパターニングすることで、導電膜の一部からなるゲート電極(120)を形成するとともに、このエッチングの際、シリコン酸化膜の上層をオーバーエッチングする工程と、オーバーエッチングする工程の後に、半導体層にオーバーエッチングされたシリコン酸化膜を介して水素化処理を行う工程と、を有する。

(もっと読む)

201 - 220 / 2,903

[ Back to top ]