Fターム[5F110CC05]の内容

Fターム[5F110CC05]の下位に属するFターム

順スタガドープ (105)

Fターム[5F110CC05]に分類される特許

101 - 120 / 2,051

半導体装置

【課題】導体半導体接合を用いて、優れた特性を示す、あるいは、作製の簡単な、あるいは、より集積度の高い電界効果トランジスタを提供する。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

(もっと読む)

電子デバイス

【課題】薄膜トランジスタおよび/または電子デバイスの電荷キャリア移動度を増大させ、高い移動度および優れた安定性を達成する。

【解決手段】薄膜トランジスタの半導体層は、半導体組成物として、ポリマー結合剤および小分子半導体を含む。また、半導体層は、ソース電極およびドレイン電極の間の方向に配列したアライメント層上に堆積されている。アライメント層は、電子デバイスの電界効果移動度を増大させるために使用される。

(もっと読む)

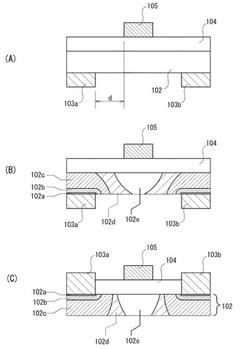

膜の製造方法および表示装置の製造方法

【課題】微細な貫通孔を有する膜を形成することが可能な膜の製造方法、およびこの方法を用いた表示装置の製造方法を提供する。

【解決手段】第1パターンおよび第2パターンを有する凹版を用いて、第1パターンの膜を基材へ形成する第1転写工程と、第1パターンの膜上に第2パターンの膜を形成して、基材上に貫通孔を有する膜を形成する第2転写工程とを備えた膜の製造方法。基板に、TFT,絶縁膜および有機EL素子を順に形成する工程を含み、絶縁膜を形成する工程は、第1パターンおよび第2パターンを有する凹版を用いて、第1パターンの膜を基材へ形成する第1転写工程と、第1パターンの膜上に第2パターンの膜を形成して、基材上に貫通孔を有する膜を形成する第2転写工程とを備えた表示装置の製造方法。

(もっと読む)

薄膜トランジスタの製造方法およびロール状薄膜トランジスタ

【課題】本発明は、低温かつ安価な製造工程により作製可能であり、トランジスタ特性に優れる薄膜トランジスタおよびその製造方法を提供することを主目的とするものである。

【解決手段】本発明は、基板と、ゲート電極と、ゲート絶縁層と、酸化物半導体層と、ソース電極と、ドレイン電極と、を有する薄膜トランジスタの製造方法であって、酸化性ガスを含む雰囲気で酸化物半導体層を形成する酸化物半導体層形成工程と、上記酸化物半導体層形成工程後、上記酸化物半導体層の少なくともチャネル領域に酸素欠損を付与して上記チャネル領域のキャリア濃度を制御するキャリア濃度制御工程と、を有することを特徴とする薄膜トランジスタの製造方法を提供する。

(もっと読む)

有機薄膜トランジスタの評価方法

【課題】処有機薄膜トランジスタのチャネル領域の電荷状態の微視的様相を観測でき、電荷トラップなどの欠陥による電荷密度の変化を捉えることが可能な、有機薄膜トランジスタの評価方法を提供する。

【解決手段】基板上にゲート電極と、ソース電極と、ドレイン電極と、ゲート絶縁膜層と、有機半導体層とを備え、前記電極を介して印加する電圧によって該電極で画されたチャネル領域の電荷状態が制御を受ける薄膜トランジスタの評価方法であって、前記電極を通じて矩形波または正弦波により時間振動する変調電圧を印加するとともに、前記チャネル領域にレーザー光を照射してその透過光を得、前記変調電圧の高電圧時における透過光強度(T)と、該透過光強度(T)から前記変調電圧の低電圧時における透過光強度を差し引いた値(ΔT)を測定して、それらの値(TとΔT)に基づいて前記チャネル領域の電荷密度分布を求める。

(もっと読む)

半導体装置

【課題】フォトセンサを有する半導体装置において、外光のノイズを軽減し、且つトランジスタのオフ電流によるリークが原因となるノイズも低減する。

【解決手段】マトリクス状に配置された複数のフォトセンサを有する。複数のフォトセンサはそれぞれ、光電変換素子と増幅回路とを有する。バックライトを点灯して被検出物に光を照射して第p行目のフォトセンサでリセット動作及び蓄積動作を行った後、バックライトを非点灯として第(p+1)行目のフォトセンサでリセット動作及び蓄積動作を行い、その後全行のフォトセンサの選択動作を順次行う。隣接する行のフォトセンサで得られた出力信号の差分を取得し、差分を用いて被検出物の撮像画像の生成や被検出物の存在する領域の検出を行う。増幅回路は蓄積された電荷を保持するトランジスタを有し、当該トランジスタはチャネルが酸化物半導体層に形成される。

(もっと読む)

半導体装置

【課題】処理実行中に電源をオフしてもデータが保持され、且つ従来よりも占有面積が小さいDフリップフロップ回路を有する半導体装置を提供する。

【解決手段】入力端子が、第1のトランスミッションゲートの第1の端子に電気的に接続され、第1のトランスミッションゲートの第2の端子が、第1のインバータの第1の端子及び機能回路の第2の端子に電気的に接続され、第1のインバータの第2の端子及び機能回路の第1の端子が、第2のトランスミッションゲートの第1の端子に電気的に接続され、第2のトランスミッションゲートの第2の端子が第2のインバータの第1の端子及びクロックドインバータの第2の端子に電気的に接続され、第2のインバータの第2の端子及びクロックドインバータの第1の端子は出力端子に電気的に接続されており、機能回路にはオフ電流が小さいトランジスタと容量素子との間にデータ保持部を有する半導体装置とする。

(もっと読む)

半導体装置

【課題】連想メモリは一つのメモリセル内の素子数が多く、一つのメモリセルの面積が大きくなりやすい。そこで、一つのメモリセルの面積を小さくする。

【解決手段】読み出し用のトランジスタのチャネル容量(ゲート電極とチャネル形成領域との間の容量)を用いて電荷の保持を行う。つまり、読み出し用のトランジスタを電荷保持用のトランジスタとして兼用する。また、読み出し用且つ電荷保持用のトランジスタのゲートに電荷供給用のトランジスタのソース又はドレインの一方を電気的に接続する。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】電力の供給がない状況でもデータの保持が可能、かつ書き込み回数にも制限がない、新たな構造の半導体記憶装置を提供する。また、単位面積あたりの記憶容量を増加させる。

【解決手段】一対の電極と、一対の電極の側壁と接して設けられた絶縁膜と、該絶縁膜を介して一対の電極間に設けられ、一対の電極の上面の高さよりも上面の高さの低い第1のゲート電極と、第1のゲート電極上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜および一対の電極と接して設けられた酸化物半導体膜と、少なくとも酸化物半導体膜上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜上に設けられた第2のゲート電極と、を有する第1のトランジスタと、一対の電極の一方を介して第1のトランジスタと接続されるキャパシタと、を有し、該キャパシタに保持される電位に応じてデータが記憶されるメモリセルからなる半導体記憶装置である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。また、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】多値書き込みを行う半導体装置、及び半導体装置の駆動方法において、酸化物半導体層を含むトランジスタを用いたメモリセルに書き込みを行う書き込みトランジスタのオンオフを制御する信号線を、ビット線に沿うように配置し、読み出し動作時に容量素子に与える電圧を書き込み時にも利用して、多値書き込みを行う。トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体である酸化物半導体材料を用いることで、長期間にわたって情報を保持することが可能である。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】演算部と、メモリと、演算部及びメモリを制御する制御部と、を有し、制御部は、揮発性の記憶回路と揮発性の記憶回路に保持されたデータを記憶するための第1の不揮発性の記憶回路との組を複数有し、メモリは、第2の不揮発性の記憶回路を複数有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する。

(もっと読む)

半導体記憶装置

【課題】データ保持のためのリフレッシュ動作の頻度を低減し、消費電力の小さいDRAMを提供する。また、DRAMに占めるキャパシタの面積を縮小し、集積度の高い半導体記憶装置を提供する。

【解決手段】ビット線、ワード線、トランジスタおよびキャパシタからなる半導体記憶装置であり、トランジスタは、ソース電極およびドレイン電極と、少なくともソース電極およびドレイン電極の上面と接する酸化物半導体膜と、少なくとも酸化物半導体膜の上面と接するゲート絶縁膜とを有し、上面から見て網状の導電膜の網の目の部分に設けられる。ここで、キャパシタは、一対の電極の一方と、網状の導電膜と、一対の電極の一方および網状の導電膜の間に設けられた第2の絶縁膜と、を有する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、更にソース線を削減することにより単位面積あたりの記憶容量を増加させる。

(もっと読む)

フォトセンサの駆動方法、半導体装置の駆動方法、半導体装置、及び電子機器

【課題】小型でコントラストの高い画像データを取得することができるフォトセンサを提供する。該フォトセンサを用いた半導体装置を提供する。

【解決手段】受光素子と、スイッチング素子であるトランジスタと、トランジスタを介して受光素子と電気的に接続する電荷保持ノードとを有するフォトセンサにおいて、導通状態から非導通状態とするためにトランジスタへ供給する駆動パルスの入力波形の立ち下がり時間を遅延させ、電荷保持ノードが保持する電荷の減少を抑制する。

(もっと読む)

記憶装置、及び半導体装置

【課題】プロセスを複雑化させることなく、単位面積あたりの記憶容量を高めることができる記憶装置を提案する。

【解決手段】複数のメモリセルと、複数のワード線と、複数のビット線とを有し、複数のメモリセルは、スイッチング素子と、第1の電極及び第2の電極を有する容量素子と、をそれぞれ有し、複数のメモリセルの少なくとも1つにおいて、複数のワード線のうち一のワード線に与えられる電位に従って、スイッチング素子が複数のビット線のうち一のビット線と第1の電極の接続を制御し、なおかつ、第2の電極が複数のワード線のうち一のワード線とは異なる一のワード線に接続されている記憶装置。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】記憶回路におけるデータの保持期間を長くする。また、消費電力を低減する。また、回路面積を小さくする。また、1回のデータの書き込みに対する該データの読み出し可能回数を増やす。

【解決手段】記憶回路を具備し、記憶回路は、ソース及びドレインの一方にデータ信号が入力される第1の電界効果トランジスタと、ゲートが第1の電界効果トランジスタのソース及びドレインの他方に電気的に接続される第2の電界効果トランジスタと、一対の電流端子を有し、一対の電流端子の一方が第2の電界効果トランジスタのソース又はドレインに電気的に接続される整流素子と、を備える。

(もっと読む)

有機半導体素子の製造方法および有機半導体素子

【課題】本発明は、有機半導体層の移動度を低下させることなく、容易に有機半導体層をパターニングした有機半導体素子を得ることができる有機半導体素子の製造方法を提供することを主目的とする。

【解決手段】本発明は、ソース電極およびドレイン電極を覆うように、低分子有機半導体材料を有する有機半導体層を形成する有機半導体層形成工程と、上記ソース電極および上記ドレイン電極間のチャネル領域を含むように、上記有機半導体層上に第一誘電体層を形成する第一誘電体層形成工程と、上記低分子有機半導体材料を溶解することができる溶媒で、上記有機半導体層の一部を洗浄することにより、第一誘電体層非形成領域の上記有機半導体層を除去する洗浄除去工程と、上記第一誘電体層を覆うように第二誘電体層を形成する第二誘電体層形成工程と、を有することを特徴とする有機半導体素子の製造方法を提供することにより、上記課題を解決する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路における消費電力を低減すること。また、半導体集積回路における動作の遅延を低減すること。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

101 - 120 / 2,051

[ Back to top ]