Fターム[5F110DD21]の内容

Fターム[5F110DD21]に分類される特許

161 - 180 / 538

半導体およびその製造方法

【課題】SOI構造を有するCMOSトランジスタにおいて、CMOSトランジスタのチャネル領域に応力を印加する構造の製造方法の提供。

【解決手段】単結晶のシリコン基板11の表面に素子分離領域13Iにより画成されたnチャネルMOSトランジスタ10Aが形成された第1の素子領域13AとpチャネルMOSトランジスタ10Bが形成された第2の素子領域13Bとを含む単結晶シリコンの活性層13を形成し、シリコン基板と活性層との間に形成されたシリコン酸化膜を有し、シリコン酸化膜は第1の素子領域の下および第2の素子領域の下に連続して延在し、nチャネルMOSトランジスタのチャネル領域のシリコン酸化膜は最大の膜厚を有し、ゲート長方向に向かって膜厚を減少させ、pチャネルMOSトランジスタのチャネル領域のシリコン酸化膜は最小またはゼロの膜厚を有し、チャネル領域から、ゲート長方向に向かって膜厚を増大させることを特徴とする。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】優れた電気伝導特性を安定して示すカーボンナノチューブ電界効果トランジスタを再現性よく製造することができる方法を提供すること。

【解決手段】まず、LOCOS法によりシリコン基板のコンタクト領域に酸化シリコン膜を形成する。次いで、シリコン基板のチャネル領域に、コンタクト領域の酸化シリコン膜よりも薄い絶縁膜を形成する。次いで、シリコン基板上にチャネルとなるカーボンナノチューブを配置した後、カーボンナノチューブを保護膜で被覆する。最後に、ソース電極およびドレイン電極をそれぞれ形成して、ソース電極およびドレイン電極をそれぞれカーボンナノチューブに電気的に接続させる。このようにして製造された電界効果トランジスタは、チャネルとなるカーボンナノチューブが汚染されていないため、優れた電気伝導特性を安定して示す。

(もっと読む)

有機電界効果トランジスタ

【課題】

この種の有機電界効果トランジスタ(OFET)としては、各種の形態が存在するが、いずれも、それぞれに長短を有するものである。

本発明は、トップコンタクト構造(TC)とボトムコンタクト構造(BC)の両構造に固有の欠点を克服するため、そして、局所的に有機物半導体層の面内配向を制御するため上記課題を解決した構造を提供することを目的とする。

【解決手段】

本発明の有機電界効果トランジスタは、ソース電極及びドレイン電極が基板に埋め込まれてなることを特徴とし、有機電界効果トランジスタにおいて、前記基板には前記ソース電極及びドレイン電極のそれぞれの設置個所に凹所が形成され、当該凹所内に前記ソース電極及びドレイン電極が設置されてなり、前記凹所の両側壁が上部に向かうほど開くように傾斜させてあることを特徴とする。

(もっと読む)

アクティブマトリクス基板およびその製造方法

【課題】導電層配線の形状が良好であるアクティブマトリクス基板の製造方法を提供する。

【解決手段】本発明に係るアクティブマトリクス基板の製造方法は、金属ナノ粒子を含むインクを用いたインクジェット法により、複数の部位に低抵抗導電層23を形成する工程を含んでおり、絶縁性基板11上にインクの受容層12を形成する受容層形成工程と、低抵抗導電層23が形成される複数の部位のうち、互いに隣り合う第1導電層配線および第2導電層配線が形成される各部位の間において、受容層12にスリット14を形成するスリット形成工程と、スリット形成工程の後に、インクジェット法により上記各部位に低抵抗導電層23を形成する導電層形成工程とを含んでいる。

(もっと読む)

薄膜トランジスタおよび薄膜トランジスタを作製する方法

【課題】既知のTFTの性能を改良する。

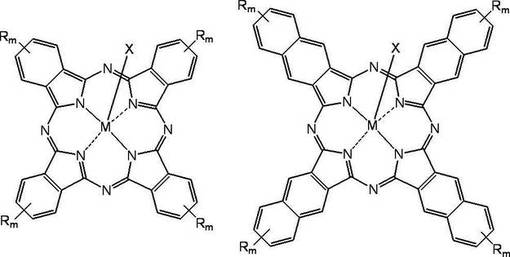

【解決手段】半導体層が、式(I)または式(II):

(式中、Mは、三価の金属原子でり、mは、0〜6の整数であり、Rは、独立に、ハロゲン、アルキル、置換アルキル、アルコキシ、置換アルコキシ、フェノキシ、フェニルチオ、アリール、置換アリール、ヘテロアリール、かつXは、ハロゲン原子である。)

(もっと読む)

半導体装置

【課題】本発明は、SOI基板を用い、1枚の基板上に実際の装置に独立して適用可能なドライバ機能を搭載した半導体装置を提供することを目的とする。

【解決手段】支持シリコン基板31の上面に酸化膜32が積層され、該酸化膜32の上面に活性シリコン層33が積層されたSOI基板30、30a、30bに形成された半導体装置50、50a〜50dであって、

前記SOI基板30、30a、30bの表面40は、前記支持シリコン基板31が露出した支持シリコン基板露出領域41と、前記活性シリコン層33が形成された活性シリコン層領域42、43とを有し、

前記支持シリコン基板露出領域41又は前記活性シリコン層領域42、43の一方には出力回路10、10a〜10eが形成され、他方には該出力回路10、10a〜10eを駆動制御する制御回路20、20a〜20dが形成されたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】横方向固相エピタキシャル成長法において単結晶膜成膜工程に要する時間を短縮し、半導体装置の製造を短時間で行う。

【解決手段】単結晶シリコン部403及び絶縁膜401が表面において露出したウエハ200を、構成元素としてSiを含むガスの雰囲気中に曝露し、単結晶シリコン部403及び絶縁膜401の上にアモルファスのシリコン膜402を成膜する成膜工程と、成膜工程後に、シリコン膜402を加熱して、単結晶シリコン部403を基にしてシリコン膜402を単結晶化させる加熱工程と、加熱工程後に、ウエハ200を構成元素としてSiを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、単結晶化した部分を残留させつつ、単結晶化しなかった部分を除去する選択成長工程と、を含む半導体装置の製造方法であって、ウエハ200に対して、成膜工程、加熱工程及び選択成長工程を繰り返す。

(もっと読む)

半導体装置の作製方法

【課題】面方位が(100)の単結晶シリコン膜および面方位が(110)の単結晶シリコン膜を有するSOI基板を、高い歩留まりで作製する方法を提供する。

【解決手段】面方位が(100)の第1の単結晶シリコン基板1000内に第1のイオンをドープして、第1の脆化層を形成する。面方位が(110)の第2の単結晶シリコン基板1002内に第2のイオンをドープして選択的に第2の脆化層を形成する。第1の加熱処理では、第1の脆化層のみから第1の単結晶シリコン基板の一部をはく離し、第1の単結晶シリコン膜を形成する。第2の単結晶シリコン基板であって、第2の脆化層が形成されていない領域を除去し、第2の加熱処理では、第2の脆化層から第2の単結晶シリコン基板の一部をはく離し、第2の単結晶シリコン膜を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層に新たな機能を有する素子を設けた半導体装置を提供する。

【解決手段】半導体基板上に形成された第1配線層150、及び半導体素子200を備える。第1配線層150は、絶縁層156と、絶縁層156の表面に埋め込まれた第1配線154とを備える。半導体素子200は、半導体層220、ゲート絶縁膜160、及びゲート電極210を備える。半導体層220は、第1配線層150上に位置する。ゲート絶縁膜160は、半導体層220の上又は下に位置する。ゲート電極210は、ゲート絶縁膜160を介して半導体層220の反対側に位置する。

(もっと読む)

半導体装置、半導体装置の製造方法、および電子機器

【課題】隔壁パターンの段差によって半導体層をパターニングする方法を、印刷法を用いてソース電極およびドレイン電極を形成するボトムゲート・トップコンタクト型の有機TFTの作製に適用して作製可能な半導体装置を提供する。

【解決手段】基板3上に形成された島パターン5、島パターン5の上部に延設されたゲート電極7、ゲート電極7を覆う状態で基板3上に設けられたゲート絶縁膜9、島パターン5を内包する形状の開口部11aを有してゲート絶縁膜7上に設けられた隔壁パターン11、開口部11aの底面を覆う形状に分断して設けられた半導体層13、島パターン5の上部における半導体層13上に設けられたソース電極15sおよびドレイン電極15dを備えた半導体装置1である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】結晶欠陥が少なく結晶性の高い単結晶シリコン層が絶縁膜上に形成されてなる半導体装置の製造方法及び半導体装置を得るという課題があった。

【解決手段】基板1の一面1aに絶縁膜2を形成する工程と、絶縁膜2を開口して基板1を露出させる穴2cを形成する工程と、穴2cの内壁面を覆うように結晶成長補助膜3を形成する工程と、穴2cを充填するとともに、絶縁膜2の前記基板と反対側の面2aを覆うように非結晶シリコン層を形成する工程と、前記非結晶シリコン層を、レーザーアニール法により単結晶シリコン層5とする工程と、を有する半導体装置101の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

薄膜トランジスタ及び電気光学装置並びに電子機器

【課題】薄膜トランジスタにおいて、光リーク電流の発生を抑制しつつ、製造方法の簡素化を図る。

【課題を解決するための手段】薄膜トランジスタは、基板(10)上に、第1の方向に延在する凸状の段差(12a)を表面に有する下地膜(12)と、下地膜上に第1の方向に交差する第2の方向に沿って長手状に形成され、凸状の段差に対応した段差を表面に有し、凸状の段差に重なる領域において、チャネル幅方向に沿った幅寸法が局所的に狭く形成された半導体層(30a)と、半導体層にゲート絶縁膜(13)を介して対向配置されたゲート電極(30b)とを備える。

(もっと読む)

薄膜トランジスタおよび半導体組成物

【課題】移動度、電流オンオフ比が高く、閾値電圧は可能な限りゼロ(0)に近い薄膜トランジスタを提供する。

【解決手段】S、Se、O等を含む特定の種類の有機半導体材料を含有する薄膜トランジスタ。

(もっと読む)

薄膜トランジスタおよび半導体組成物

【課題】移動度、電流オンオフ比が高く、閾値電圧が可能な限りゼロ(0)に近い薄膜トランジスタを提供する。

【解決手段】半導体層を含む薄膜トランジスタであって、前記半導体層が、式(A)で表される半導体材料を含有する、薄膜トランジスタ。

(Xは、S、Se、O、NR6から選択され;R1、R2、R3、R4、R5、R6は、水素、アルキル、置換アルキル、アリール、置換アリール、ヘテロアリール、ハロゲン、−CN、−NO2から選択され;Ar、Ar’は、共役した2価の部分であり;a、bは、0〜10の整数であり;mは、0または1であり;nは、2以上の整数である。)

(もっと読む)

半導体素子およびその製造方法並びに表示装置

【課題】過剰なエッチングを生じることなく、同一のエッチング行程において、複数のコンタクトホールを同時に形成することができ、歩留まりおよび生産性に優れた半導体素子およびその製造方法並びに表示装置を提供することを目的とする。

【解決手段】TFT12は、ボトムゲート電極20、ボトムゲート絶縁膜17、半導体層13、トップゲート絶縁膜18、トップゲート電極14及び層間絶縁膜19がこの順に積層された構造を有する。また、トップゲート絶縁膜18および層間絶縁膜19には、コンタクトホール25〜28が形成されている。また、層間絶縁膜19の表面には、ボトムゲート電極20、半導体層13、およびトップゲート電極14の各々に接続される配線30〜32が形成されている。そして、ボトムゲート電極20の、配線31との接続領域34に、ボトムゲート電極20の下方に配置されるとともに、ボトムゲート電極20を支持する段差部材35が設けられている。

(もっと読む)

グラファイト薄膜の切断方法、グラファイト薄膜を備える積層基板、およびこれを用いる電界効果トランジスタ

【課題】複雑な加工技術を用いることなく、グラファイト薄膜をナノスケール幅に切断することができるグラファイト薄膜の切断方法を提供すること。

【解決手段】複数の段差部1aを有する基板1の表面に、グラファイト薄膜2を設ける工程と、グラファイト薄膜2が設けられた基板1を、酸素含有雰囲気下で加熱して、グラファイト薄膜2を段差部1aの位置で切断する工程とを含む、グラファイト薄膜の切断方法。

(もっと読む)

電気光学装置及びその製造方法

【課題】例えば、液晶装置の画像表示領域のうち非開口領域が占める割合を増大させることなく、画素スイッチング用素子等の半導体素子における光リーク電流を低減する。

【解決手段】第1層間膜(41)は、第2遮光膜(11)上に形成されている。第1層間膜(41)は、第2遮光膜(11)の形状に対応してTFTアレイ基板10の上方に向かって突出した第1突状部(41a)を有している。このような第1層間膜(41)は、半導体層(1a)の下地になる絶縁膜である。したがって、第2遮光膜(11)上に第1層間膜(41)が形成されるだけで、第1層間膜(41)のうち第2遮光膜11に重なる部分が第2遮光膜(11)の形状に対応した形状を有する第1突状部41aになる。

(もっと読む)

MIS電界効果トランジスタ及び半導体基板の製造方法

【課題】高温特性を改善した高集積、高速且つ高性能なMISFETを得ること。

【解決手段】半導体基板に絶縁膜を埋め込んだトレンチ素子分離領域を選択的に設け、この絶縁分離された半導体基板上に、半導体基板と同じ第1の半導体を、筒状構造を有して縦方向にエピタキシャル成長させ、この第1の半導体層に自己整合して、格子定数がやや大きい第2の半導体を内側面の横方向にエピタキシャル成長させることにより、第1の半導体層に歪みを加える。この第2の半導体層の上部内側面を除く内側面に接して絶縁膜を設け、この絶縁膜の側面間を空孔となし、この空孔に栓をするように、第2の半導体層の上部内側面間に導電膜を設ける。歪み半導体層の外側面にはゲート絶縁膜を介してゲート電極を設ける。歪み半導体層及び第2の半導体層の上部にはドレイン領域を設け、歪み半導体層及び第2の半導体層の下部且つ半導体基板の表面にはソース領域を設けておき、配線体をそれぞれの領域に接続した縦型のMISFETを構成すること。

(もっと読む)

半導体インク配合物

【課題】薄膜トランジスタの製造において有用な半導体インク配合物を提供する。

【解決手段】半導体インク配合物は、構造式(A)のチオフェン部分を含む半導体材料と、第1の溶媒と、第1の溶媒と混和性であり、第1の溶媒の表面張力に等しいかまたはそれより大きい表面張力を有する第2の溶媒とを含み、該半導体材料が室温にて0.1重量%未満の溶解度を有する。

(上記構造式(A)中、R1は、アルキルおよび置換アルキルから選択される。)

(もっと読む)

有機デバイスとその製造方法

【課題】大気雰囲気下での使用や、デバイスとして駆動するため電界が印加された際に、有機分子層同士を結合している共有結合が切断され、分子層積層構造が崩壊する恐れがない、耐久性に優れた分子層積層膜による有機薄膜を作製して用い、素子寿命が改善された有機デバイスを提供する。

【解決手段】基板11と、該基板11上第一の有機分子層12と、該第一の有機分子層12に積層された第二の有機分子層14とを備え、該第一の有機分子層12と第二の有機分子層14が、第一の結合部13によって接続され、前記第一の結合部13の構成が、前記第一の有機分子層12と前記第二の有機分子層14との間を接続する第一の共有結合部131と、前記第一の有機分子層12および/または前記第二の有機分子層14と、前記第一の共有結合部131の構成原子との間を接続する第一の化学結合132からなる有機デバイス。

(もっと読む)

161 - 180 / 538

[ Back to top ]