Fターム[5F110DD21]の内容

Fターム[5F110DD21]に分類される特許

121 - 140 / 538

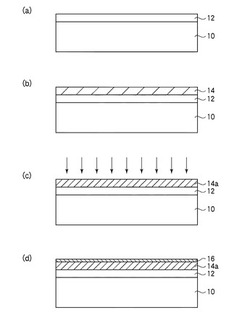

グラフェン膜の製造方法及び半導体装置の製造方法

【課題】成膜時間を短縮し得るグラフェン膜の製造方法及び半導体装置の製造方法を提供する。

【解決手段】基板10上に炭素を含有する触媒金属層14を形成する工程と、炭素含有ガスを用いて触媒金属層上にグラフェン膜16を成長する工程とを有している。

(もっと読む)

半導体装置

【課題】回路ブロックを構成するMOS型トランジスタを同一構造にしたまま駆動電圧を下げ、消費電力を低くすることができる複数の回路ブロックから構成される半導体装置の提供。

【解決手段】本半導体装置の構造は、消費電力を低くしたい回路ブロック11が設けられている半導体基板14の厚さ19を薄くすることにより、MOS型トランジスタの閾値を小さくでき、駆動電圧を下げ、所望の回路ブロックの消費電力を下げることができる。

(もっと読む)

薄膜半導体装置、薄膜半導体製造装置及び薄膜半導体製造方法

【課題】低温プロセスで形成可能であり、また比較的高い電界効果移動度を実現でき、かつ光、熱に対して安定な特性を有し、曲げ環境にも適用できる薄膜半導体の製造方法を提供する。

【解決手段】プラスチック基板2と、バリア層3と、半導体層7と、半導体層7の上下いずれかの面に接して形成された絶縁層8aと、半導体層7、ソース電極9a、ドレイン電極9b、およびゲート電極9c、ゲート絶縁膜8aとを有し、半導体層7は、少なくとも一つの非金属元素、少なくとも一つの半金属元素、少なくとも一つの金属元素を含み、非金属元素が、少なくとも酸素(O)と窒素(N)の混合物で、酸素(O)に対する窒素(N)の比(N数密度/O数密度)が0乃至2である。

(もっと読む)

グラフェン・ベースの三次元集積回路デバイス

半導体装置の作製方法

【課題】結晶粒の位置とその大きさを制御した結晶質半導体膜を作製し、さらにその結晶質半導体膜をTFTのチャネル形成領域に用いることにより高速動作を可能にする。

【解決手段】基板1上に、島状で且つ端部にテーパーを有する膜2を設け、無機絶縁膜3、非晶質半導体膜を形成する。そして、レーザーアニールにより非晶質半導体膜を結晶化させる。島状で且つ端部にテーパーを有する膜2または無機絶縁膜3の材料及び膜厚を適宜調節することによって半導体膜の冷却速度を遅くして結晶粒径の大きな第1領域4aを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】低容量且つ高温特性が良好な素子分離領域を有する高速なMIS電界効果トランジスタを提供する。

【解決手段】半導体基板1にウエル領域2が設けられ、ウエル領域2内には上部、下部及び側面にシリコン酸化膜3を有し、内部が空孔4に形成されたトレンチ素子分離領域が選択的に設けられ、トレンチ素子分離領域により画定されたウエル領域2が設けられた半導体基板1上にゲート酸化膜9を介してゲート電極10が設けられ、ゲート電極10の側壁にサイドウォール11が設けられ、ウエル領域2が設けられた半導体基板1には、ゲート電極10に自己整合して低濃度のソースドレイン領域(6、7)及びサイドウォール11に自己整合して高濃度のソースドレイン領域(5、8)が設けられ、高濃度のソースドレイン領域にはそれぞれバリアメタル14を有する導電プラグ15を介してバリアメタル17を有する配線18が接続されている構造からなるMIS電界効果トランジスタ。

(もっと読む)

トランジスタ及びその製造方法

【課題】キャリア移動度を高く、かつ、動作のための印加電圧を低くしつつ、オフ電流が低いトラジスタを提供すること。

【解決手段】基板上にて互いに離間したソース電極及びドレイン電極を有し、前記基板上における前記ソース電極と前記ドレイン電極との間にチャネル部を有し、前記チャネル部上に所定の間隔をおいてゲート電極を有し、前記チャネル部は、カーボンナノチューブ又はグラフェン若しくは金属ナノワイヤーよりなり、前記基板は、表面において、前記チャネル部と立体交差する複数の導体線が周期的にパターンニングされた導体パターンを有する。

(もっと読む)

埋め込み絶縁層を貫いて半導体層間に接触を有するデバイス、およびこのデバイスの製造プロセス

【課題】簡潔な方法で、SeOI基板上の半導体デバイスの半導体領域に接続するラインを提供すること。

【解決手段】第1の側面によると、本発明は埋め込み絶縁層(3、BOX)によってベース基板(2)から隔離された半導体材料の薄い層(1)を含むSeOI(Semiconductor−On−Insulator)基板上に作製された半導体デバイスに関し、デバイスは、薄い層内に第1の伝導領域(1、D1、S、E)と、ベース基板内に第2の伝導領域(5、BL、SL、IL)とを含み、接触(I1、I2、IN、IP)は絶縁層を貫通して第1の領域と第2の領域を接続する。第2の側面によると、本発明は第1の側面に関する半導体デバイスの製作プロセスに関する。

(もっと読む)

グラフェン膜と金属電極とが電気的接合した回路装置

【課題】グラフェン膜と金属電極との間の接触抵抗を低減してグラフェン膜と金属電極とが良好に電気的接合された回路装置を提供する。

【解決手段】本発明に係るグラフェン膜と金属電極とが電気的接合した回路装置は、単層または複数層からなるグラフェン膜を利用した回路装置であって、前記グラフェン膜と直接接触する下地層としての酸化アルミニウム膜が前記グラフェン膜の下部のみに形成されており、前記酸化アルミニウム膜の組成がAl2-xO3+x(x ≧ 0)であり、前記グラフェン膜と金属電極とが直接接合し、該接合箇所には凹凸構造が形成され、前記凹凸構造は、前記酸化アルミニウム膜に形成された少なくとも1つのコーン状凹部と、前記コーン状凹部を含む前記酸化アルミニウム膜の表面に沿って該表面と平行に成長した前記グラフェン膜と、前記グラフェン膜を覆いかつ前記コーン状凹部を埋めるように形成された前記金属層とから構成されていることを特徴とする。

(もっと読む)

半導体装置およびその作製方法

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびドレイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、酸化物半導体層の厚さは1nm以上10nm以下であり、ゲート絶縁層は、ゲート絶縁層に用いられる材料の比誘電率をεr、ゲート絶縁層の厚さをdとして、εr/dが、0.08(nm−1)以上7.9(nm−1)以下の関係を満たし、ソース電極とドレイン電極との間隔は10nm以上1μm以下である半導体装置である。

(もっと読む)

不揮発性のラッチ回路及び論理回路及びそれを用いた半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力は第2の素子の入力に電気的に接続され、第2の素子の出力は第2のトランジスタを介して第1の素子の入力に電気的に接続されるループ構造を有するラッチ回路であって、チャネル形成領域を構成する半導体材料として酸化物半導体を用いたトランジスタをスイッチング素子として用い、またこのトランジスタのソース電極又はドレイン電極に電気的に接続された容量を有することで、ラッチ回路のデータを保持することができる。これにより不揮発性のラッチ回路を構成することができる。

(もっと読む)

不揮発性のラッチ回路及び論理回路並びにそれを用いた半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力が第2の素子の入力に電気的に接続され、第2の素子の出力が第1の素子の入力に電気的に接続されるループ構造を有するラッチ部と、ラッチ部のデータを保持するデータ保持部とを有し、このラッチ部とデータ保持部とにより不揮発性のラッチ回路が構成される。データ保持部は、チャネル形成領域を構成する半導体材料として酸化物半導体を用いたトランジスタをスイッチング素子として用いている。またこのトランジスタのソース電極又はドレイン電極に電気的に接続された容量を有している。

(もっと読む)

誘電体分離型半導体装置

【課題】高耐圧かつ、電流駆動能力が高く、かつ電流集中による素子破壊の起こりにくい誘電体分離型半導体装置を提供する。

【解決手段】半導体支持基板の上に、絶縁された第一導電型の半導体領域とを有する誘電分離基板に形成した誘電体分離型半導体装置において、第一導電型の半導体領域と絶縁分離領域の間と、前記第1導電型の半導体領域の基板表面側と、に形成されたドレイン領域と、第一導電型のソースと第二導電型の半導体領域のチャネルからなる複数個の単位ソース領域と、第一導電型の半導体領域の基板表面側に形成されたドレイン領域と前記複数個の単位ソース領域の間を制御する複数個のゲート電極とを、備え、隣接する前記単位ソース領域間に絶縁分離領域が、基板底面側から基板表面側に向けて突き出した形状とされ、この絶縁分離領域上の素子表面領域が前記第一導電型の半導体領域より抵抗値が高い。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトランジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置

【課題】良質な半導体装置を提供することを目的としている。

【解決手段】素子分離領域間の凸部108を含むシリコン基板106と、凸部108上の絶縁部112と、絶縁部112上のシリコンフィン114と、上面が凸部108の上面よりも低く位置する素子分離領域内の素子分離層116と、シリコンフィン114に設けられたソース/ドレイン領域と、ソース/ドレイン領域104のシリコンフィン114の側面から外側に突き出た横方向エピ成長シリコン部118と、ゲート電極領域102内のゲート絶縁層122を介してシリコンフィン114上に設けられるゲート電極124と、ゲート電極124の側面に隣接する第1のスペーサ128と、ソース/ドレイン領域104内の凸部108の側面を覆う第2のスペーサ130とを備える。

(もっと読む)

素子基板、素子基板の製造方法、素子基板の製造装置及び表示装置

【課題】動作信頼性の高い素子基板、素子基板の製造方法、素子基板の製造装置及び表示装置を提供すること。

【解決手段】基板と、当該基板上に設けられ、互いのゲート幅が同一方向に揃うように形成された複数のトランジスタ素子とを備える。

(もっと読む)

III族窒化物系半導体素子およびIII族窒化物系半導体素子の製造方法

【課題】低コストで製造することができ、かつ、高い絶縁破壊耐圧を有するIII族窒化

物系半導体素子、およびIII族窒化物系半導体素子の製造方法を提供する。

【解決手段】シリコン層、絶縁層、および表面にシリコンからなる複数の核領域と前記複

数の核領域の間を埋める絶縁領域を有する複合層がこの順に形成された基板と、前記基板

上に形成されたIII族窒化物系半導体からなるバッファ層と、前記バッファ層上に形成

されたIII族窒化物半導体からなる動作層と、前記動作層上に形成された第1の電極お

よび第2の電極とを備え、前記核領域のそれぞれの最大幅L1が、前記第1の電極および

前記第2の電極の間の距離L2よりも小さいことを特徴とする。

(もっと読む)

ナノワイヤデバイスの絶縁

本開示は、マイクロ電子デバイスの製造の分野に関する。少なくとも1つの実施形態において、本願の特徴は、絶縁されたナノワイヤの形成に関し、ナノワイヤに隣接する絶縁構造は、マイクロ電子構造をその上面に形成するために、実質的に平坦な表面となっている。 (もっと読む)

画像表示装置

【課題】樹脂基板等と無機膜との間に、適切な応力緩和膜を形成することにより、樹脂基板等に対して前記無機膜が剥がれ難くした画像表示装置の提供。

【解決手段】薄膜トランジスタが形成されている樹脂基板あるいは樹脂層を有する画像表示装置であって、

前記樹脂基板あるいは樹脂層の前記薄膜トランジスタが形成されている側の面に、第1無機膜および第2無機膜が順次積層されて形成され、

前記第2無機膜は第1の方向に応力を有するのに対し、前記第1無機膜は前記第1の方向と反対の方向に応力を有するように形成され、

前記第1無機膜の応力をσ1、前記第2無機膜の応力をσ2、前記第1無機膜の膜厚をt1、前記第2無機膜の膜厚をt2とした場合、

σtotal = σ1・t1 / (t1 + t2) + σ2・t2 / (t1 + t2) …… (1)

-200 MPa ≦ σtotal ≦ 0MPa …… (2)

上式(1)、(2)の関係を有する。

(もっと読む)

半導体装置

【課題】チャネル形成領域の空乏化領域を増やし、電流駆動能力の高い半導体装置を提供する。

【解決手段】トランジスタを有する半導体装置であって、絶縁表面上に所定の間隔を隔てて互いに平行に配列された複数の短冊状の半導体膜と、前記複数の短冊状の半導体膜の上面及び側面に接するゲート絶縁膜と、前記ゲート絶縁膜を介して前記複数の短冊状の半導体膜の上面及び側面を覆うゲート電極を有する半導体装置である。半導体膜の上部及び側部をチャネル形成領域とすることで、電流駆動能力を向上させることができる。

(もっと読む)

121 - 140 / 538

[ Back to top ]